- 1.In International Workshop on Low Power Design, April 1994.Google Scholar

- 2.A. Chandrakasan et. al. "Optimizing Power Using Transformations". IEEE Transactions on Computer Aided Design. Submitted, Dec. 1993.Google Scholar

- 3.A. Chandrakasan et. al. "HYPER-LP: A System for Power Minimization Using Architectural Transformations". In International Conference on Computer-Aided Design. IEEE/ACM, 1992. Google Scholar

Digital Library

- 4.A. H. Farrahi, G. T~llez, and M. Sarrafzadeh. "Exploiting Sleep Mode Through Activity-Driven Partitioning". Technical report, Northwestern University, EECS Department, Evanston, IL, November 1994.Google Scholar

- 5.C. M. Fiduccia and 1%. M. Mattheyes. "A Linear Time Heuristic for Improving Network Partitions". In Design Automation Conference, pages 175-181, 1989. Google Scholar

Digital Library

- 6.M. 1%. Garey and D. S. Johnson. Computers and Intractability: A Guide to the Theory of NP-completeness. Freeman, 1979. Google Scholar

Digital Library

- 7.B.W. Kernighan and S. Lin. "An Efficient Heuristic Procedure for Partitioning Graphs". Bell System Technical Journal, 49:991-307, Feburary 1970.Google Scholar

Cross Ref

- 8.1%. Mehra and J. l%abaey. "Behavioral Level Power Estimation and Exploration". In International Workshop on Low Power Design, pages 197-9.09. IEEE/ACM, 1994.Google Scholar

- 9.K. Roy and S. Prasad. "Circuit Activity Based Logic Synthesis for Low Power Reliable Operations". IEEE Transactions on VLSI Systems, 1(4):503- 513, 1993.Google Scholar

Digital Library

- 10.G. T@llez, A. H. Farrahi, and M. Sarrafzadeh. "Activity-Driven Clock Design for Low Power Circuits". Technical report, Northwestern University, EECS Department, Evanston, IL, November 1994.Google Scholar

- 11.V. Tiwari, P. Ashar, and S. Malik. "Technology Mapping for Low Power". In Design Automation Conference, pages 74-79. ACM/IEEE, 1993. Google Scholar

Digital Library

- 12.C. Tsui, M. Pedram, and A.M. Despain. "Technology Decomposition and Mapping Targeting Low Power Dissipation". In Design Automation Conference, pages 68-73. ACM/IEEE, 1993. Google Scholar

Digital Library

- 13.H. Vaishnav and M. Pedram. "A Performance Driven Placement Algorithm for Low Power Designs". In EUI%O-DAC, 1993.Google Scholar

- 14.H. J. M. Veendrick. "Short-circuit Dissipation of Static CMOS Circuitry and its Impact on the Design of Buffer Circuits". Journal of Solid State Circuits, pages 468-473, August 1984.Google Scholar

- 15.Y. C. Wet and C. K. Cheng. "Ratio-Cut Partitioning for Hierachical Designs". IEEE Transactions on Computer Aided Design, 40(7):911-99.1, July 1991.Google Scholar

Index Terms

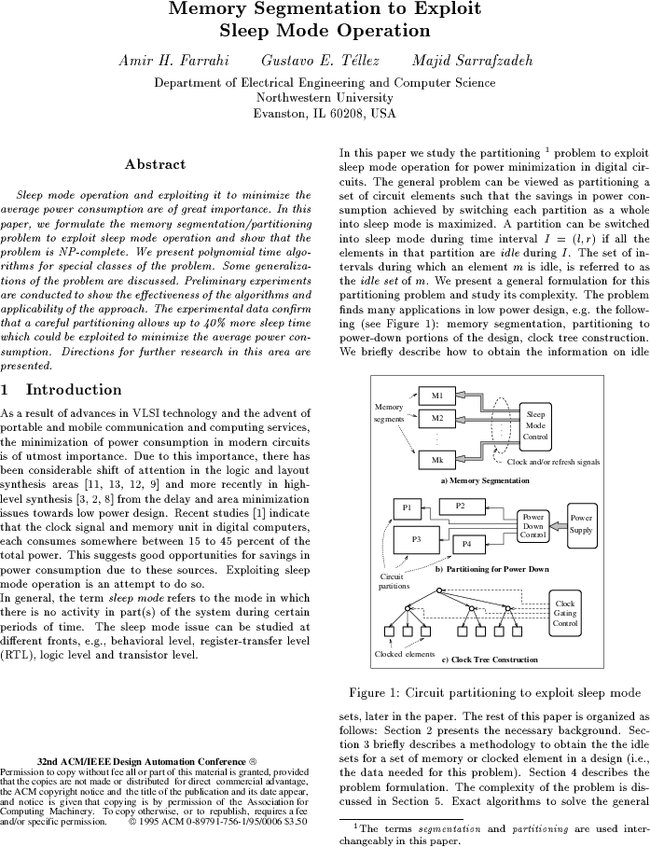

- Memory segmentation to exploit sleep mode operation

Recommendations

Sleep-Mode Voltage Scaling: Enabling SRAM Data Retention at Ultra-Low Power in Embedded Microcontrollers

Special Issue on VIPES, Special Issue on ICESS2015 and Regular PapersIn heavily duty-cycled embedded systems, the energy consumed by the microcontroller in idle mode is often the bottleneck for battery lifetime. Existing solutions address this problem by placing the microcontroller in a low-power (sleep) mode when idle ...

Secure non-volatile memory with scratch pad memory using dual encryption mode: work-in-progress

CODES '18: Proceedings of the International Conference on Hardware/Software Codesign and System SynthesisThis paper proposes a secure non-volatile main memory (NVMM) with a scratch pad memory (SPM) management compiler to reduce the number of bit flips in NVMM.

The main idea is to categorize data to write-intensive and non write-intensive, and apply the CTR ...

A workload-aware flash translation layer enhancing performance and lifespan of TLC/SLC dual-mode flash memory in embedded systems

Similar to traditional NAND flash memory, triple-level cell (TLC) flash memory is used as secondary storage to meet the fast growing demands on storage capacity. TLC flash memory exhibits attractive features such as shock resistance, high density, low ...

Comments