## Symmetrically Modified Laddered H-Bridge Multilevel Inverter with Reduced **Configurational Parameters**

Shyam D, Premkumar K, Thamizhselvan T, Nazar Ali A, Vishnu Priya M

Abstract: Multilevel Inverters are incorporated in this modern world for medium and high-level applications for its adaptability to improve power quality problems. Its necessity is growing big in developing newer techniques and topologies for efficient implementation of DC to AC conversion system. Developing the MLI using less active switching components, less switching losses on active devices and improvement of number of voltage levels is always a tough task. A step forward to solve this problem is to modify the existing H-bridge multilevel inverter to produce Symmetrically Modified Laddered H-Bridge Multi-level Inverter (SMLHB -MLI). Comparative analysis has been carried out with other reputed existing MLI topologies to find out the performance and reduces complexity problem in inverter based on reduced switching methods in inverter side, reduction of active switching components and power diodes.

Keywords: Multilevel inverter (MLI), Pulse Width Modulation (PWM), Symmetrically Modified Laddered H-Bridge (SMLHB), Neutral Point Clamped (NPC), Total Harmonic Distortion (THD)

#### I. INTRODUCTION

Generation of inverter technology provides solution to achieve higher power applications by connecting series semiconductor switches with many DC sources. The structural behaviour of multilevel inverter produces laddered network (staircase) at the output voltage [1][2]. Basically, Inverters are classified based on its structure, which is usually represented as symmetrical type structure and asymmetrical type structure [3]. Both these inverters are efficient in their own ways by improving the quality of the inverter output voltage [4]. Firstly, it provides a brief analysis on the functional parts of the inverter which is to be analysed carefully and then trying different switching strategy to produce harmonic free system. To better understand the

Revised Manuscript Received on October 30, 2019.

\* Correspondence Author

Shyam D\*, Department of EEE, Realtime Adaptive Control Engineering Laboratory, Rajalakshmi Engineering College, Chennai, India. Email: shyamdec1987@gmail.com

Premkumar K, Department of EEE, Realtime Adaptive Control Engineering Laboratory, Rajalakshmi Engineering College, Chennai, India. Email: prem.kamaraj@gmail.com

Thamizhselvan T, Department of EEE, Rajalakshmi Engineering College, Chennai, India.

Nazar Ali A, Department of EEE, Rajalakshmi Engineering College, Chennai, India.

Vishnu Priya M, Department of ECE, Saveetha School of Engineering, Chennai, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

operational principles of the inverter, basic knowledge of what type of system is need to be known. Both symmetrical and asymmetrical type inverters focus on reducing the number of input DC sources rather than reducing the power switches to the system. This brings complexity in the circuits which in turn brings the cost of the inverter to be high [5].

Multilevel inverter (MLI) proffer for high power capabilities, duly resulting in the reduction of level of harmonics and the commutation losses [6][7]. MLIs are used in variety of industrial and power related applications such as industrial motor drives, electrical motors, interfaced for renewable sources using solar/wind, active rectifiers, filters, static compensators and uninterruptible power supply (UPS) The main disadvantage is to bring down their complexity by increasing number of power devices and passive components, and rather complex control circuitry. This presents the features like output voltage boosting capability accompanied with capacitor voltage balancing problem [6]-[8].

Conventional multilevel inverters (MLI) are classified based on Neutral point-clamped MLI (NPC), Flying capacitor MLI, and Cascaded multilevel inverter. When compared to Neutral point clamped MLI and Flying capacitor MLI, Cascaded H-bridge MLI uses a smaller number of components to achieve same number of voltage levels and optimized layout circuit because each level shares the same structure and doesn't require extra clamping diodes or capacitors [5]-[9].

The major setback of Multilevel inverter is to bring down the switching losses, conduction losses, Total Harmonic Distortion (THD) and Harmonics which is added to the system. The primary concern is to reduce harmonics and THD analysis which is present in different multilevel inverter topology. This is incorporated to suppress the harmonics produced by the inverter at its output level [10]-[12]. The major reason for increase in switching losses and harmonics in the system is due to increase in switching components. The cascaded MLI is effective in reduction of selective harmonics which is why it is used in fuel cell applications and battery stored power devices [13]. Research focus has turned towards the improvement on inverter side and few results from various research paper have focused on the improvement of number of levels. As the number of levels in the inverter increases, the combined output waveform has a greater number of output steps [14]-[17]. Harmonic distortions are reduced with increase in steps. Smoothness of the waveform is proportional with increase in voltage level the waveform but the complexity of circuit increases with increase in components [18][19][20].

Various developments in the inverter technology have taken place during a course of time. It might be on the topological side, battery size or different modulation techniques used. Despite of its growth, little concern on the inverter side looks to be harmonics [21][22]. It would create detrimental effect on switching components in both electrical as well as mechanical parts. This also determines the life span of the inverter [23].

Different modulation techniques such as Selective Harmonic Elimination PWM (SHE-PWM), Multi-carrier sinusoidal pulse width modulation (MC-SPWM) and other referenced technique [24]-[28] has been initiated to Hybrid multi-level inverter with new topology in sequence to reduce the THD level with minimum number of switches possible. This would bring down the cost and reduces the switching losses considerably [29][30].

The scope of developing new techniques and topologies in inverter is in rise among researchers [31]-[33]. Multilevel inverter is one among them which is widely used in high power applications. Researchers focus on the switching losses and stresses produced during switching as a result of attaining higher output voltage [34]-[40]. There are significant improvements in symmetrical configuration which provides a smaller number of DC sources added to the system. The drawback in both symmetrical and Asymmetrical configuration is the cascade connection which is added which has the greatest number of switches added to it. In proposed system, A modified ladder network pattern of symmetrical multilevel inverter is implemented with reduced number of active switches, DC sources and power diodes.

# II. PROPOSED SYMMETRICALLY MODIFIED LADDERED H-BRIDGE MULTI-LEVEL INVERTER (SMLHB -MLI)

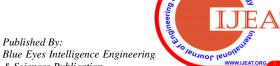

The proposed Symmetrically Modified Laddered H-Bridge MLI (SMLHB -MLI) is a hybrid combination of H-bridge comprising of 2 DC sources  $(V_1, V_2)$ , 4 capacitors, 9 unidirectional switches  $(S_1, S_2, S_3.... S_9)$  and 12 freewheeling diodes connected across each switching sequence. Always bi-directional switching should be provided with almost care because it is a "converted unidirectional switching". That is Bi-directional switch (S<sub>5</sub>) is converted to unidirectional switches in the SMLHB topology. Due to structural implementation of closed loop of the switching sequence, active mode switches present in the system should not be turned ON at the same time, otherwise different values of voltage (random) would appear across the load. The value of capacitors (C1, C2, C3, C4) would be identical to each other and also acts as a voltage divider. Important instruction to be followed while designing the hardware is to provide same capacitor value and that too from same manufacturer is better. The rating of the capacitor voltage must match with the minimum requirement of the DC source connected with the system.

For efficient implementation of the Voltage division rule across each capacitor, A large value of resistance (ceramic resistor usually in Mega Ohm) should be connected across each capacitor in parallel to produce same voltage across them

Design of multilevel inverter (MLI) need to be done to incorporate renewable sources of energy such as solar, wind, hybrid methods to provide constant voltage to the system during peak time and off-peak time. Rooftop with green

building will bring down pollution level and adapt few techniques. Selection of each component has to be handled carefully because these are one-time investment which should not be changed/modified continuously. For every modification or changes, its cost would increase. So, handling and selection process of each component is the most difficult part of the system.

Fig. 1 Configuration of SMLHB MLI topology

Table I Modes of switching of SMLHB MLI

| Mod<br>e | <b>S</b> <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | S <sub>6</sub> | <b>S</b> <sub>7</sub> | S <sub>8</sub> | <b>S</b> 9 | Ou<br>tpu<br>t |

|----------|-----------------------|----------------|----------------|----------------|-----------------------|----------------|-----------------------|----------------|------------|----------------|

| 1        | 1                     | 1              | 0              | 0              | 0                     | 1              | 0                     | 0              | 1          | +4             |

| 2        | 0                     | 1              | 1              | 0              | 0                     | 1              | 0                     | 0              | 1          | +3             |

| 3        | 0                     | 1              | 0              | 0              | 1                     | 0              | 0                     | 0              | 1          | +2             |

| 4        | 0                     | 0              | 0              | 1              | 1                     | 0              | 0                     | 0              | 1          | +1             |

| 5        | 0                     | 0              | 0              | 0              | 0                     | 1              | 1                     | 0              | 0          | 0              |

| 6        | 0                     | 0              | 1              | 0              | 1                     | 0              | 1                     | 0              | 0          | -1             |

| 7        | 1                     | 0              | 0              | 0              | 1                     | 0              | 1                     | 0              | 0          | -2             |

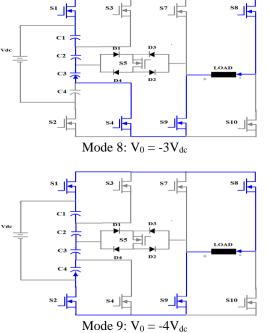

| 8        | 1                     | 0              | 0              | 1              | 0                     | 0              | 1                     | 1              | 0          | -3             |

| 9        | 1                     | 1              | 0              | 0              | 0                     | 1              | 1                     | 1              | 0          | -4             |

As the proposed system is based on symmetrical level of implementation, the DC sources should be same value and identical in nature ( $V_{dc}=V_1=V_2$ ). The maximum operating voltage which is generated at the output side of the SMLHB-MLI topology is shown below in Eq. (1):

Voperating

$$(max) = n\left(\frac{Vdc}{2} + \frac{Vdc}{2}\right)$$

(1)

In order to reach the appropriate level in the symmetrical configuration, proper choosing of the magnitude level of DC source is required.

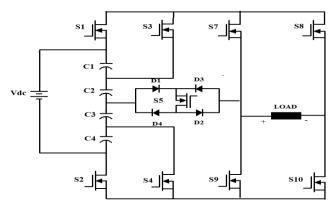

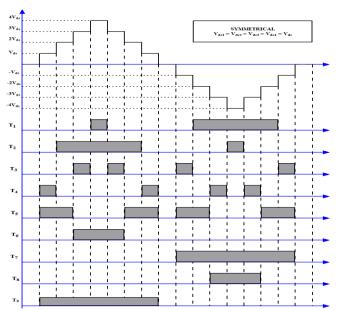

In order to provide proper switching of the SMLHB -MLI to produce 9 level output voltage:  $+V_{dc}$ ,  $+2V_{dc}$ ,  $+3V_{dc}$ ,  $+4V_{dc}$ , 0,  $-V_{dc}$ ,  $-2V_{dc}$ ,  $-3V_{dc}$ ,  $-4V_{dc}$ .

The maximum number of voltage level can be attained by switching certain switches from  $S_1$  to  $S_9$  to operate in different mode condition which is described in Table 1. The converted unidirectional switch  $S_5$  must be switched properly based on the direction of load current. The configuration and schematic diagram of different switching modes for the proposed SMLHB MLI is illustrated in *Fig. 1* and *Fig. 2*.

Journal Website: www.ijeat.org

Fig. 2: Different switching states of SMLHB -MLI (Mode 1-9)

The most common topology in multilevel inverter is H-bridge. There are many method and topologies presented by various researchers in H-bridge. This proposed method is inspired and modified from many H-bridge topologies. The proposed SMLHB -MLI topology produces 9- level output with 12 freewheeling diodes and this proposed topology can be performed for 'N' levels starting from 9-level MLI. For proposed 9-level symmetrical output configuration, the following equations Eq. (2) -Eq. (4) are derived based on number of levels 'N'

Number of DC sources required = (N-1)/4 (2)

Number of Capacitors required = (N-1)/2 (3)

Number of IGBTs required = (N+9)/2 (4)

For each level one additional voltage source is required with converted unidirectional switch is added to the system. For example, 9-level MLI requires 4 capacitors and one converted unidirectional switch which is connected to H-bridge. For 11-level MLI requires 5 capacitors of same value based on the voltage rating and two converted unidirectional switch which is connected to H- bridge. For 13 level MLI, 6 capacitors of same value with three converted unidirectional switches is required and so on.

In this proposed topology, one switch has to be turned ON in each leg to produce positive or negative voltage based on load direction. For producing positive voltage  $S_7$  and  $S_{10}$  has to be turned and for negative voltage  $S_8$  and  $S_9$  has to be turned ON. Two switches from the same leg should not be turned ON otherwise shoot through effect takes place. Among the 9 switches, switch  $S_5$  is converted unidirectional switch. All the switches in the proposed system are IGBT's where the conventional methods are carry forwarded in MOSFET. Each level is obtained based on turning ON and OFF of IGBT's because IGBT has high input impedance and high switching speed.

Retrieval Number: A2074109119/2019©BEIESP DOI: 10.35940/ijeat.A2074.109119

Journal Website: www.ijeat.org

5527

**Fig. 3 Staircase output voltage waveform of SMLHB MLI** In the positive mode,  $S_{10}$  switch is always ON and in the negative mode,  $S_8$  will be always ON. For producing  $+V_{dc}$  (Mode IV),  $S_1$ ,  $S_7$ ,  $S_{10}$  and  $S_2$  switches has to turn ON. For producing  $+2V_{dc}$  (Mode III),  $S_3$ ,  $S_7$ ,  $S_{10}$  and  $S_2$  switches is turned ON. For producing  $-V_{dc}$  (Mode VI),  $S_1$ ,  $S_8$ ,  $S_9$  and  $S_2$  switches has to be turned ON.

#### III. SIMULATION RESULTS OF SMLHB-MLI

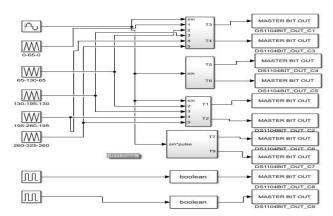

The proposed topology 9-Level SMLHB -MLI are simulated in MATLAB 2015a/Simulink model for resistive load which is shown in Fig. 4. The simulation results for the proposed system is carried for both R and RL load. Among various

modulation techniques, Multicarrier alternative phase opposition disposition (APOD) PWM technique is commonly used in single phase inverter system. This PWM scheme is used in SMLHB MLI system for the generation of gating signals. There are two major categories in multi-carrier based PWM techniques. They are based on phase shifted PWM technique and the other is level shifted PWM technique. Level based PWM technique is used for switching gates pulses for the circuit which is based on number of levels.

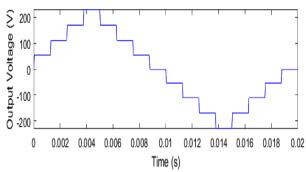

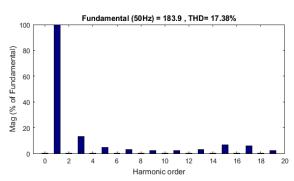

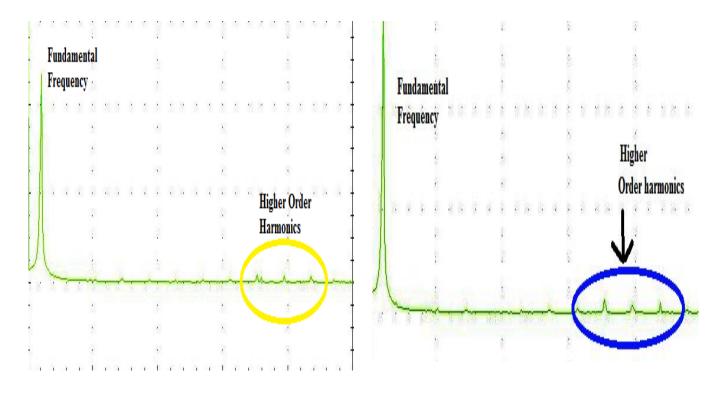

The selection of the symmetrical configuration uses identical value of DC sources ( $V_1 = V_2 = 100V$ ). Therefore, the total DC voltage value is 200V. The Reference frequency is set as 50 Hz and carrier frequency used for both R and RL load is 4000 Hz. The primary focus of the proposed SMLHB -MLI topology is to find out the percentage of THD present in the system. In order to reduce the THD value, reduction of switching components is necessary. Table II shows the comparative analysis of different conventional topologies compared with the proposed topology based on the number of components used. The simulation results of unfiltered Output voltage and THD for resistive load [R= 50  $\Omega$ ] is analyzed using Fast Fourier Transform (FFT) window in MATLAB simulation for 9level SMLHB which is shown in Fig. 4 and Fig. 5. The simulated THD value obtained from resistive load of the SMLHB topology is 17.38%. The RMS voltage (V<sub>rms</sub>) is 183.9V for resistive load. When the system is connected to RL load of value R= 50  $\Omega$  and L= 100 mH. The simulated THD value obtained from resistive- inductive load of the SMLHB topology is 5.17%. The results produced in the proposed system doesn't have any filter added to it.

Fig. 4. Simulation results for SMLHB -MLI Simulation Circuit

Fig. 5. 9- Level simulated output voltage and corresponding THD using resistive load

Retrieval Number: A2074109119/2019©BEIESP DOI: 10.35940/ijeat.A2074.109119 Journal Website: www.ijeat.org Published By: Blue Eyes Intelligence Engineering & Sciences Publication

In order to eliminate harmonics in the system, better design of filter is required. There are many filters with eliminates harmonics such as L, C and LC filters. Usually LC filter is preferred for single phase inverters because L and LCL performance adds complexity which in turn increases the cost.

The secondary focus is to reduce the losses in the system. These losses are caused by two major components. One is conduction losses and the other is switching losses. These losses play a vital role in deciding the efficiency of the inverter. Conduction losses are nothing but operational losses in the switches such as IGBTs/MOSFETs and the presence of freewheeling diodes present in the conduction path. Switching losses are produced due to turning ON and turning OFF of the switches (IGBTs/MOSFETs). In order to show the feasibility in reduction of losses in the proposed system, the following values  $R_{\rm switch}=0.3\Omega,\,R_{\rm diode}=0.15\,\Omega,\,V_{\rm switch}=2V,\,V_{\rm diode}=0.9V,\,\beta=1,$  and ton = toff = 1 $\mu s$  were taken to find out the conduction losses and switching losses in the system.

$$\begin{split} Total \ loss \left(P_{loss}\right) &= \left(P_{cond}\right) + \left(P_{SW}\right) \\ \left(P_{loss}\right) &= \left(P_{Switch}(t) + P_{diode}(t)\right) + \left(P_{turn-on} + P_{turn-off}\right) \end{aligned} \tag{5}$$

Total power loss needs to be minimised in order to get maximum efficiency of the inverter.

The efficiency of the proposed SMLHB-MLI after using Multi-carrier PWM technique is 98.7%. This can be improved by using better implementation of different PWM techniques.

#### IV. EXPERIMENTAL RESULTS OF SMLHB-MLI

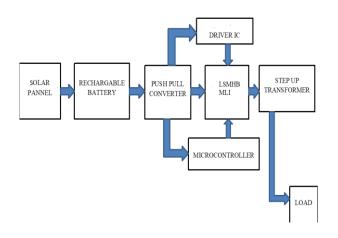

The proposed SMLHB -MLI system has been simulated for R and RL load. Simulation results has to be verified and tested in hardware also in order to prove its feasibility in both simulation and hardware. The hardware implementation of the proposed system is done using C2000 real time control MCU interfaced with MATLAB platform. The hardware implementation is done for 9- level multilevel inverter which is controlled by C2000 microcontroller.

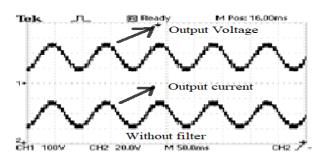

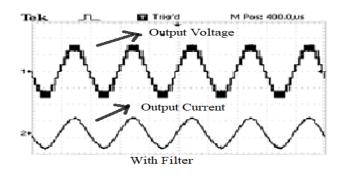

Based on the experimental analysis for 9- level inverter, various factors need to calculated to find the better solution for inverter analysis. This system is performed for modulation index M of 0.9 for both R load. The values of R load are 50  $\Omega$  taken from the simulation results. The peak voltage from the hardware results is 200 V and the RMS voltage of magnitude is 164.2V. Fig. 6 shows the hardware configuration of SMLHB MLI. Fig. 7 indicates the output voltage and current waveform and its corresponding THD analysis is performed for R load for unity power factor without filter and with filter circuit.

Fig. 6. Hardware configuration and implementation of SMLHB MLI

(a) Without filter

(b) With filter

Fig. 7. Hardware results for output end and THD for R load (without and with filter)

Table- II: Comparative analysis of different conventional topologies with SMLHB -MLI

| Inverter Type                  | Flying<br>Capacitor [12] | Neutral<br>Point<br>Clamped<br>(NPC) [3] | Reverse<br>Voltage<br>Topology | Cascaded<br>H-bridge | Switch<br>Ladder Modified<br>(SLMHB) [10] | Proposed<br>Topology<br>(SMLHB) |

|--------------------------------|--------------------------|------------------------------------------|--------------------------------|----------------------|-------------------------------------------|---------------------------------|

| MOSFETs/IGBTs                  | 6 (N-1)                  | 6 (N-1)                                  | 3((N-1) +4)                    | 6 (N-1)              | (N-1)/2                                   | (N+9)/2                         |

| Diode across MOSFETs/<br>IGBTs | 6 (N-1)                  | 6 (N-1)                                  | 3((N-1) +4)                    | 6 (N-1)              | (N+11)/2                                  | (N-1)                           |

| Clamping diodes                | 0                        | 3 (N-1) (N-2)                            | 0                              | 0                    | 0                                         | 0                               |

| Isolated DC sources            | (N-1)                    | (N-1)                                    | (N-1)/2                        | 3(N-1)/2             | (N+3)/10                                  | (N-1)/4                         |

| Flying Capacitors              | 3/2 (N-1) (N-2)          | 0                                        | 0                              | 0                    | 0                                         | 0                               |

| Total Number of Components     | ½(N-1) (3N+20)           | (N-1) (3N+7)                             | (13N+35)/2                     | 27(N-1)/2            | 11(N+54/11)/10                            | (7N+13)/4                       |

#### V. CONCLUSION

This paper focuses on the basic analysis of Symmetrically Modified Laddered H-Bridge Multi-level Inverter (*SMLHB* -*MLI*) and their modes of operation are presented. The proposed system is used to generate output voltage based on number of levels with minimum number of switches and power electronic components used. Comparative analysis for various existing topologies were compared with the proposed system based on the number of DC sources, active switches and gate driver circuits. Lesser the switching frequency, lesser is the switching losses. This can be achieved by using Multi-carrier PWM technique as the novel method which is suitable for single phase inverter applications. The Simulation results and experimental results of the proposed Symmetrically Modified Laddered H-Bridge MLI has been carried and matched with results to prove its feasibility.

#### REFERENCES

J. Rodriguez, J. S. Lai and F. Z. Peng. "Multilevel inverters: a survey of topologies controls and applications". IEEE Transactions on Industrial Electronics, Vol. 49, No. 4, pp.724-738, Aug. 2002.

- K. Corzine and Y. Familiant. "A new cascaded multilevel h bridge drive".

IEEE Transactions on Power Electronics, Vol. 77, No. 1, pp.125-131, Jan.2002.

- A. Nabae, I. Takahashi and H. Akagi. "A new neural point clamped PWM Inverter". IEEE Transactions on Industrial Electronics, Vol. IA- 17, No. 5, pp.518-523, Oct.1981.

- Gupta, K.K.; Jain, S., "Multilevel inverter topology based on series connected switched sources," Power Electronics, IET, vol.6, no.1, pp.164-174, Jan. 2013.

- Shyam D, Premkumar K., "Review of inverter and multilevel inverter: features, techniques, topology and latest developments", International Journal of Pure and Applied Mathematics, Volume 118, No. 24 2018. Available: https://acadpubl.eu/hub/2018-118-24/3/474.pdf

- S. Ganapathy, M. Balasingh Moses, J Barsana Banu "An Asymmetrical Multilevel Inverter Model with minimum power electronic components" International Journal of Research in Advent Technology, Vol.7, No.5, May 2019

- E. Babaei and S. H. Hosseini. "New cascaded multilevel inverter topology with the reduced number of switches". Journal of Energy Conversion and Management, Vol. 50, No. 11, pp.2761-2767, Nov.2009.

- 8. E. Babaei. "A cascaded multilevel converter topology with the reduced number of switches". IEEE Transaction on Power electronics Vol. 23, No. 6, pp. 2657-2664, Nov.2008.

Retrieval Number: A2074109119/2019©BEIESP DOI: 10.35940/ijeat.A2074.109119 Journal Website: www.ijeat.org

Blue Eyes Intelligence Engineering & Sciences Publication

Published Ry:

- J. Ebrahimi, E. Babaei and G. B. Gharehpetian. "A new topology of cascaded multilevel converters with the reduced number of components for high voltage applications" *IEEE Transaction on Power Electronics*, Vol. 26, No.11, pp. 3109-3118, Nov.2011.

- 10.Malik Muhammad Zaid, Jong-Suk Ro. "Switch Ladder Modified H-Bridge Multilevel Inverter with Novel Pulse Width Modulation Technique", IEEE Access, 2019

- 11.R. S. Alishah, S. H. Hosseini, E. Babaei, and M. Sabahi, "Optimal design of new cascaded switch-ladder multilevel inverter structure," IEEE Trans. Ind. Electron., vol. 64, no. 3, pp. 2072–2080, Mar. 2017.

- 12.R. S. Alishah, S. H. Hosseini, E. Babaei, and M. Sabahi, "Optimization assessment of a new extended multilevel converter topology," IEEE Trans. Ind. Electron., vol. 64, no. 6, pp. 4530–4538, Jun. 2017.

- 13.R. Barzegarkhoo, M. Moradzadeh, E. Zamiri, H. Madadi Kojabadi and F. Blaabjerg, "A New Boost Switched-Capacitor Multilevel Converter with Reduced Circuit Devices," in IEEE Transactions on Power Electronics, vol. 33, no. 8, pp. 6738-6754, Aug. 2018.

- 14.E. Samadaei, A. Sheikholeslami, S. A. Gholamian, and J. Adabi, "A square T-type (ST-Type) module for asymmetrical multilevel inverters," IEEE Trans. Power Electron., vol. 33, no. 2, pp. 987–996, Feb. 2018.

- 15.A. Kshirsagar et al., "17-level inverter with low component count for open-end induction motor drives," in IET Power Electronics, vol. 11, no. 5, pp. 922-929, 1 5 2018.

- 16.S. P. Gautam, L. Kumar and S. Gupta, "Single-phase multilevel inverter topologies with self-voltage balancing capabilities," in IET Power Electronics, vol. 11, no. 5, pp. 844-855, 1 5 2018.

- 17.C. Dhanamjayulu and S. Meikandasivam, "Implementation and Comparison of Symmetric and Asymmetric Multilevel Inverters for Dynamic Loads," in IEEE Access, vol. 6, pp. 738-746, 2018.

- 18.V. Nair R, K. Gopakumar and L. G. Franquelo, "A Very High Resolution Stacked Multilevel Inverter Topology for Adjustable Speed Drives," in IEEE Transactions on Industrial Electronics, vol. 65, no. 3, pp. 2049-2056, March 2018.

- 19.B. Ngo, M. Nguyen, J. Kim and F. Zare, "Single-phase multilevel inverter based on switched-capacitor structure," in IET Power Electronics, vol. 11, no. 11, pp. 1858-1865, 18 9 2018.

- 20.M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal and M. A. Memon, "A New Multilevel Inverter Topology with Reduce Switch Count," in IEEE Access, vol. 7, pp. 58584-58594, 2019.

- 21.M. D. Siddique, S. Mekhilef, N. M. Shah and M. A. Memon, "Optimal Design of a New Cascaded Multilevel Inverter Topology with Reduced Switch Count," in IEEE Access, vol. 7, pp. 24498-24510, 2019.

- 22.M. D. Siddique et al., "Low Switching Frequency based Asymmetrical Multilevel Inverter Topology with Reduced Switch Count," in IEEE Access. doi: 10.1109/ACCESS.2019.2925277

- K. Premkumar and B.V. Manikandan, "Stability and Performance Analysis of ANFIS Tuned PID Based Speed Controller for Brushless DC Motor," in Current Signal Transduction Therapy, vol.13, no.1, 2018, pp. 19-30

- 24. Premkumar Kamaraj, Manikandan, Bairavan Veerayan, Kumar, and Chellappan Agees, "Antlion Algorithm Optimized Fuzzy PID Supervised On-line Recurrent Fuzzy Neural Network Based Controller for Brushless DC Motor," Electric Power Components and Systems, vol.45, no.20, 2018, pp.2304-2317.

- 25.A. Taheri and H. Samsami, "New topology of a switched-capacitor based multilevel inverter with a single DC power supply," in IET Power Electronics, vol. 12, no. 6, pp. 1571-1584, 29 5 2019.

- 26.Rao, S. N., D. V. A. Kumar, and C. S. Babu. "New multilevel inverter topology with reduced number of switches using advanced modulation strategies", 2013 International Conference on Power Energy and Control (ICPEC), 2013.

- 27. M. John Prabu, P. Poongodi, and K. Premkumar, "Fuzzy supervised online coactive neuro-fuzzy inference system-based rotor position control of brushless DC motor," in IET Power Electronics, vol.9, no.11, September 2016, pp.2229 2239.

- K. Premkumar, and B.V. Manikandan, "Fuzzy PID supervised online ANFIS based speed controller for brushless dc motor," Neurocomputing, vol.157, 2015, pp.76-90.

- 29.Dewangan, Niraj Kumar, Vivek Gurjar, Syed Uvaid Ullah, and Sameena Zafar. "A level-doubling network (LDN) for cross-connected sources based multilevel inverter (CCSMLI)", 2014 IEEE International Conference on Power Electronics Drives and Energy Systems (PEDES), 2014

- 30.Aparna Prayag, Sanjay Bodkhe. "A comparative analysis of classical three phase multilevel (five level) inverter topologies", 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), 2016

- 31.Kuppuswamy Compala Lakshmiah, T. A. Raghavendiran. "A New Modified H-Bridge Multilevel Inverter with Multi Carrier PWM

- Technique for Speed Control of Induction Motor", International Review of Electrical Engineering (IREE), 2018

- K. Premkumar and B.V. Manikandan, "GA-PSO optimized online ANFIS based speed controller for Brushless DC motor," in **Journal** of Intelligent & Fuzzy Systems, vol. 28, no. 6, 2015, pp. 2839-2850.

- K. Premkumar and B.V. Manikandan, "Online Fuzzy Supervised Learning of Radial Basis Function Neural Network Based Speed Controller for Brushless DC Motor," in Lecture Notes in Electrical Engineering, vol.326, 2015, pp.1397-1405.

- 34.Farhadi Kangarlu, M., and E. Babaei. "A Generalized Cascaded Multilevel Inverter Using Series Connection of Sub-multilevel Inverters", IEEE Transactions on Power Electronics, 2012.

- 35.Ahmed, R A, S Mekhilef, and Hew Wooi Ping. "New multilevel inverter topology with minimum number of switches", TENCON 2010 2010 IEEE Region 10 Conference, 2010.

- 36.K. Premkumar and B.V. Manikandan, "Novel bacterial foraging-based ANFIS for speed control of matrix converter-fed industrial BLDC motors operated under low speed and high torque," in Neural Computing and Applications, vol. 29, No.12, June 2018, pp.1411–1434.

- K. Premkumar, and B.V. Manikandan, "Speed control of Brushless DC motor using bat algorithm optimized Adaptive Neuro-Fuzzy Inference System," in Applied Soft Computing, vol.32, 2015, pp.403-419.

- 38. K. Premkumar, and B.V. Manikandan, "Bat algorithm optimized fuzzy PD based speed controller for brushless direct current motor," in Engineering Science and Technology, an International Journal, vol. 19, no.2, 2016, pp.818-840.

- 39.B Rajesh, Manjesh. "Comparison of harmonics and THD suppression with three and 5 level multilevel inverter-cascaded H-bridge", 2016 International Conference on Circuit, Power and Computing Technologies (ICCPCT), 2016.

- 40.A. Kshirsagar, R. S. Kaarthik, K. Gopakumar, L. Umanand, and K. Rajashekara, "Low switch count nine-level inverter topology for open-end induction motor drives," IEEE Trans. Ind. Electron., vol. 64, no. 2, pp. 1009–1017, Feb. 2017.

#### **AUTHORS PROFILE**

**Mr. Shyam D** received the B.E. degree from Anna University Chennai in 2009, and M.E. Degree in Electrical Drives and Embedded Control from Anna University Coimbatore in 2011, all in faculty of Electrical and Electronics Engineering. Presently, he is working as an Assistant Professor in the Department of Electrical and

Electronics Engineering at Rajalakshmi Engineering College, Chennai. He has 8 years of teaching and research experience in the field of Power Electronics and Drives, Signal Processing and Renewable Energy Systems.

**Dr. Premkumar K** received the B.E. degree from Anna University Chennai in 2005, and M.E. Degree from Anna University Chennai in 2007, all in faculty of Electrical and Electronics Engineering. He obtained his Ph.D. degree from Anna University, Chennai, in the year 2015. Presently, he is working as an Associate Professor in the

Department of Electrical and Electronics Engineering at Rajalakshmi Engineering College, Chennai, Tamil Nadu, India. His current research interests include designing of speed and current controllers based on PID controller, fuzzy logic controller, ANFIS controller, and CANFIS controller for the special electrical machines. He is also an ISTE Life member and IEEE senior member.

**Dr. Thamizhselvan T** received his B.E. from Meenakshi college of Engineering in 2005 and M.E in Power Electronics & Drives from SSN Engineering college in 2007 and Ph.D from Anna University, Chennai in 2018. Presently, he is working as an Associate Professor in the Department of Electrical and Electronics

Engineering at Rajalakshmi Engineering College, Chennai, Tamil Nadu. He has 12 years of teaching and research experience including 6 years of research experience in the field of Power Electronics and Renewable Energy Systems.

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

### Symmetrically Modified Laddered H-Bridge Multilevel Inverter with Reduced Configurational Parameters

Dr. Nazar ali A received the B.E degree in Electrical and Electronics Engineering in 2003, M.Tech. in Power Electronics & Drives in 2009 and Ph.D in Electrical Engineering in 2017. Presently, he is working as Associate Professor in Electrical and Electronics Engineering department at Rajalakshmi Engineering

College, Chennai. He has 15 years experience in teaching and published 21 papers in International Jounals. His research interests include Power Electronic Converters, Renewable Energy sources and Soft Computing. He is also an ISTE Life member and IEEE senior member.

Mrs. Vishnu Priya M is an Assistant Professor in the faculty of Electronics and Communication Engineering in Saveetha School of Engineering, Chennai Tamil Nadu, India. she got her Masters and Bachelor's degree from Anna University, India. Her research area includes solar energy, power electronics, soft computing, and electrical

machines. She is currently pursuing her Ph.D in the area of multilevel inverter at Saveetha University.

Retrieval Number: A2074109119/2019©BEIESP DOI: 10.35940/ijeat.A2074.109119 Journal Website: www.ijeat.org