Hindawi International Journal of Photoenergy Volume 2022, Article ID 1648474, 23 pages https://doi.org/10.1155/2022/1648474

# Research Article

# Design of Boosted Multilevel DC-DC Converter for Solar Photovoltaic System

R. Uthirasamy, V. Kumar Chinnaiyan, S. Vishnukumar, Alagar Karthick, V. Mohanavel, Umashankar Subramaniam, and M. Muhibbullah

Correspondence should be addressed to M. Muhibbullah; m.muhibbullah@bu.edu.bd

Received 13 October 2021; Revised 11 November 2021; Accepted 15 November 2021; Published 5 January 2022

Academic Editor: Abdullrahman Alshammaa

Copyright © 2022 R. Uthirasamy et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Integration of renewable energy sources to the grid-connected system has influenced scholarly research in recent times to evolve solutions for power electronic conversion. Particularly, solar photovoltaic (SPV), being a resource available throughout the year, demands needful research to meet the demand for industrial applications. To facilitate SPV, multilevel inverters (MLIs) and cascaded H-bridge inverters (CHBIs) are proposed in the literature to meet the power requirement. However, these circuits suffer from efficiency loss, economic aspects of DC sources usage, and switching losses. Hence, in this research, a new power converter topology is projected to improve the overall efficiency of SPV systems. Further, a three-level approach involving (i) SPV Panel-Temperature Reduction (SPV-PTR) Setup, (ii) Boost Multilevel Direct Current Link Converter (BMLDCLC), and (iii) use of effective snubber modules (SM) are effectively handled to promote the industry readiness of the proposed system. From a detailed system investigation, it is seen that the proposed arrangement has minimized the power loss to ensure better quality in output. Furthermore, the software-based results and hardware setup of the planned comprehensive converter have shown promising results in terms of (i) reduced voltage stress, (ii) reduced total harmonic distortion (THD) without filter component, and (iii) reduced power loss. It is observed that the experimental setup has reported a 12.9% of excess heat removal, 5% decrease in harmonics, and 33% switch reduction than the existing MLI schemes. In addition, the proposed setup is suggested to apply for industrial purposes indicate its efficacy to be a solution in real time.

#### 1. Introduction

Alarming environmental concerns and exhaustion of fossil fuels have invoked the necessity of eco-friendly power generation via renewable energy resources [1]. Having the superiority to reduce greenhouse emissions, renewable energy is considered as one of the essential tools to avoid energy import. In particular, SPV systems have gained monumental recognition to emerge as a resource of the decade. Zero

maintenance, harmless operation, abundant availability, and easy portability are its inherent merits over other renewable energy resources.

In general, SPV modules are constant voltage sources fed to a load via power conditioning circuits. However, fabricating an efficient and cost-effective converter prototype model is really challenging. Since the power conditioning circuitries are implemented over two or three-level converters, interfacing PV panels for high power application become complex

<sup>&</sup>lt;sup>1</sup>Renewable Energy Lab, Department of Electrical and Electronics Engineering, KPR Institute of Engineering and Technology, 641407, Coimbatore, Tamilnadu, India

<sup>&</sup>lt;sup>2</sup>Department of Electronics and Communication Engineering Vel Tech Rangarajan Dr. Saguthala R&D Institute of Science and Technology, 600062, Chennai, Tamilnadu, India

<sup>&</sup>lt;sup>3</sup>Centre for Materials Engineering and Regenerative Medicine, Bharath Institute of Higher Education and Research, 600073 Chennai, Tamilnadu, India

<sup>&</sup>lt;sup>4</sup>Department of Communications and Networks, Renewable Energy Laboratory, College of Engineering, Prince Sultan University, Riyadh 11586, Saudi Arabia

<sup>&</sup>lt;sup>5</sup>Department of Electrical and Electronic Engineering, Bangladesh University, Dhaka 1207, Bangladesh

and uncertain. More importantly, sequential power electronic switching with three-level converters renders excessive voltage stress across the converter. This results in stressed transmission. Therefore, a supplementary snubber circuit at the output is mandated to reduce the transient power loss [2]. In addition, bulky filter components are also used to tap the hassle-free sinusoidal output. However, the system cost is increased beside the additional usage of transformers on the output side [3].

As an alternative to three-level converters, researchers have used multiple topologies with multilevel inverters (MLIs). It is important to note here that the advent of MLIs has enabled the efficient interface with multiple electrical applications such as (i) uninterrupted power supply (UPS) systems, (ii) motor drives, (iii) integration of renewable energy systems, (iv) static compensator, and (v) renewable energy sources [4-8]. Though MLIs have exhibited their significant merits from the end-user side, they are penalized with the necessity of high (i) power-switching components, (ii) regulator units, (iii) power supply units, (iv) gate driver circuits, (v) protection units, and (vi) DC sources to reduce its popularity [9-16]. This certainly increases the manufacturing cost of the system. Out of many configurations in MLI, a few important works in literature are presented as the review in the following. A typical nine-level multilevel inverter for induction motor application is presented in [9]. Also, the importance of high-frequency switches to control uncertainty and voltage diversity factor is critically analyzed in this research. With an objective to reduce power electronic switches, a seven-level MLI with three sources is presented in [10]. Alternatively, a nine-level MLI design with four DC sources is presented in [11]. Notably, usage of limited (twelve) Metal Oxide Semiconductor Field Effective Transistor (MOSFET) switch has gained research interest to reduce THD. However, all the aforementioned works have the drawbacks of (i) design of control circuit, (ii) elimination of lower-order harmonics, and (iii) requirement of high switching devices. Hence, a novel H-bridge-based MLI system has been proposed in [12]. But then, the research necessitates an additional DC source which remains an important downside of the topology. Sequentially to limit the source count with MLI, a seven-level MLI with only three DC sources is proposed in [13]. However, twelve controlled semiconductor switches are used. With a motive to reduce power electronic switches, a similar MLI design with eight controlled semiconductor switches is proposed in [14]. Using only three sources, the same seven-level MLI topologies are presented in [15, 16]. Nevertheless, usage of power semiconductor switches was found high compared to [14].

At the outset, in comparison to various topologies discussed in [13–20], it is seen that the output voltage is achieved either by a series connection of DC sources or using a transformer at the inverter side. Thus, it becomes a nonviable solution for grid-connected systems economically. Note that power losses are also increased due to the usage of the bulky transformer. This invokes a power converter system to maintain the nominal voltage at the DC link, and it is achieved by using appropriate DC to DC power converters. Alternatively, cascaded H-bridge inverters among MLI are also proposed in the literature. Owing to the simpler

and lucid circuitry, few research works are reported by using cascaded H-bridge inverters (CHBIs) in [17–20]. In comparison over two or three-level inverters, the use of CHBI offers multiple salient features such as (i) meagre transient across the inverter, (ii) reduced total harmonic distortion (THD) without filter component, and (iii) less significant filter components.

Commencing from the extensive review survey, it is seen that there exist a wide gap in formulating an MLI with the following advantages: (i) limited DC sources, (ii) less stress on the converter, (iii) less THD, and (iv) limited use of power electronic switches. Therefore, a new and novel seven-level stepped DC-link converter is proposed in this research. In addition, the converter is integrated with the PV source to check its viability for industry applications. In order to appreciate the panel temperature within limits, an exclusive prototype testing of PV with an aluminum sheet supported by a DC fan for cooling arrangement is performed. It is important to note here that PV panels are provided with a hydrophobic nano coating (HNC) solution to avoid dust accumulation and stagnant water droplets on PV panels. This helps the PV to shield itself from corrosion, thus increasing the lifetime for its continued quality of operation. The distinguished merits of the proposed research are summarized in the following.

- (i) A new seven-level stepped DC-link MLI with reduced stress on the converter is proposed for the first time

- (ii) The seven-level stepped DC-link converters are interfaced with the PV module, and their industrial viability is studied

- (iii) To subside the panel temperature in real time, the cooling arrangement is provided via aluminum sheet and DC fans

- (iv) To enable durability and long sustainability with PV, hydrophobic nano coating (HNC) is used

- (v) The use of two PV sources at the input side per phase eliminates the unnecessary stress on the converter

The entire paper is ordered as follows. In Section 2, PV modelling and design of DC-DC boost converter is detailed. In Section 3, the proposed converter design and its design constraints are given. Software-based results and hardware realization are given in Sections 4 and 5, respectively. To contribute to a fair comparative study, the usage of power electronic components and their losses are analyzed and compared in Section 6. Conclusions are addressed as the summary in Section 7.

### 2. PV Modelling

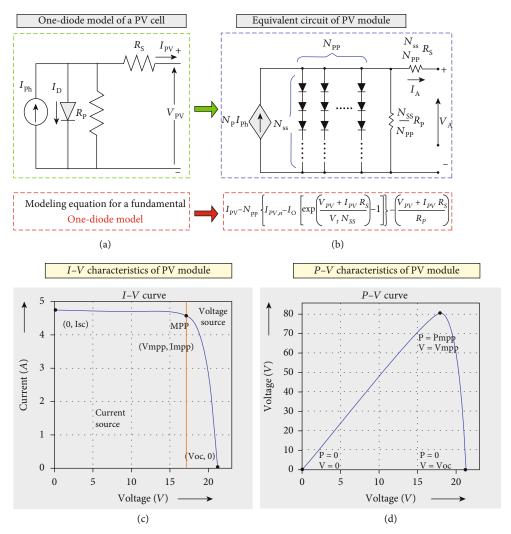

One-diode PV models are prevalently popular to use for simulation investigations. The representation of the corresponding electrical circuit of one diode PV model is represented in Figure 1 [21–23], and for better understanding,

FIGURE 1: One-diode PV model and its characteristics.

the I-V and P-V distinctiveness of a PV module are also presented in the same figure. From the characteristics, it is seen that PV operates at a unique operating point where maximum power can be extracted. In addition, PV demands a power electronic interface to enable its smoother operation. The PV output current [23] by applying KCL is given by

$$I_{\rm PV} = I_{Ph} - I_D - \frac{V + I_{\rm PV} Rs}{Rp}.$$

(1)

The ideal diode current equation is mathematically given in Equation (2).

$$I_D = I_O(e^{V_D/\alpha V_T} - 1),$$

(2)

where " $I_o$ " is the reverse saturation current, "a" is the diode ideality factor, and " $V_T$ " is the thermal voltage proportional to temperature changes which is given by

$$V_T = \frac{N_S KT}{q},\tag{3}$$

where " $N_s$ " is the number of cells connected in series, "K" is the Boltzmann constant, "T" is the temperature at STC, and "Q" is the charge of the electron  $1.9*10^{-19}$ C. On incorporating " $I_D$ " in " $I_{\rm PV}$ ," then the output current equation (24) becomes

$$I_{PV} = N_{pp} \left\{ I_{Ph} - I_O \left[ \exp \left( \frac{V_{PV} + I_{PV} R_S}{V_t N_{ss}} \right) - 1 \right] \right\} - \left( \frac{V_{PV} + I_{PV} R_S}{R_P} \right), \tag{4}$$

where " $N_{SS}$ " and " $N_{PP}$ " are the numbers of cells connected in series and parallel [24, 25].

# 3. Multilevel Stepped DC-Link Converter

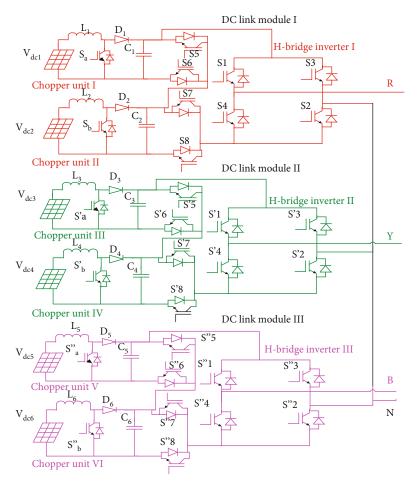

Further, synthesizing sinusoidal voltage with less harmonic using multiple DC sources is its unique characteristic. Note that three-phase multilevel inverters gain more attention since each individual phase requires an "N" number of DC sources to obtain a " $2\,N$  +" voltage output level. However, MLI greatly suffers due to the requirement for an increased

FIGURE 2: Equivalent circuit of three-phase seven-level BMLDCLC.

number of power electronic components, and this is reduced by using Boosted Multilevel DC Line Converter design. One such configuration with PV as the source is proposed in this research. The operating modes and their analysis on output voltage are discussed in the following.

3.1. Design of Boosted Multilevel DC-Link Converter (BMLDCLC). The schematic of the projected seven-level BMLDCLC circuit is represented in Figure 2. For understanding, each phase is highlighted in different colors and named in the convention as R phase, Y phase, and B phase. Note that each phase is provided with a provision to switch on and off to maintain the output voltage in limits. Further, the boost converter is interfaced among the MLI and PV sources. This eliminates the necessity of a transformer and thus improving the cost efficiency of the converter. Further, the equivalent circuit of BMLDCLC clearly shows that boost chopper takes responsibility to uphold DC-link voltage across each phase. In addition, two power sources are used in each phase reduces the stress on converter is a notable merit of proposed converter. The generalized equations (12-14) to estimate the power components, sources, and level of single-phase BMLDCLC are presented in Equations (5)–(7).

$$N_{\text{switch}} = 2s + 4H + b,\tag{5}$$

$$n = 2(H+1)^{s} - 1, (6)$$

$$H = n - (n - 1), \tag{7}$$

where "s" is the DC source count, "n" is the number of levels, "H" is the number of converter topology at load end, and "b" represents boost converter.

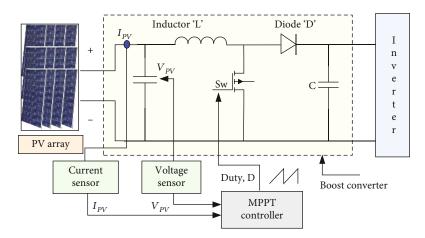

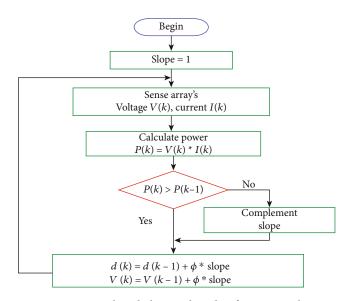

3.2. Design of Boosted Multilevel DC-Link Converter (BMLDCLC). The DC-DC boost converter is an integral part of the proposed converter design. Further, it is connected to the inverter via switching circuitry to generate AC waveforms. The schematic of the DC-DC boost converter is presented in Figure 3. Since PV is a constant voltage source, the task of boosting converter becomes much easier to maintain constant DC-link voltage across the inverter. As a known fact that PV is a nonlinear DC source, the system demands a maximum power point controller to track the MPP. To achieve this, each PV panel is provided with a current and voltage sensor to track the unique operating point where the highest accessible power is able to be pulled out. Note that a simple perturb and observe (P&O) algorithm is employed to appreciate simplicity. Besides, the necessity of a metaheuristic algorithm is not required since only one module is used as a DC source [26-30]. For brevity, the flowchart of the P&O algorithm is presented in Figure 4.

FIGURE 3: Representation of DC-DC boost converter.

In general, P&O works on the standard that repeated perturbation in voltage is made until the MPP is tracked. Based on the power values, the duty cycle of the boost chopper is altered [11]. Duty cycle equation of the boost chopper is given in the following.

$$D = \frac{V_o - V_s}{V_o},\tag{8}$$

where " $V_o$ " and " $V_s$ " are the voltage across the load and source voltage, respectively, and "D" is the duty cycle. Further, the design considerations of boost chopper are given in the following. It is always ensured that the boost chopper is worked in continuous conduction mode, and the design of inductor "L" is made by following the equation given in (9).

$$L = \frac{V_o(1-D)}{\Delta i_L f_s},\tag{9}$$

where " $\Delta i_L$ " is the inductor current  $(i_2 - i_1)$  and " $f_s$ " is the switching frequency. For better output quality, 3% current ripple is considered for designing the inductor. Capacitor design is made by following the equation given in (10).

$$C = \frac{1 - D}{8L(\Delta V_o/V_o)f_s^2},\tag{10}$$

where  $f_s = 1/T$  is the switching frequency and " $\Delta V_o/V_o$ " is the voltage ripple, and it is approximately considered as 3%.

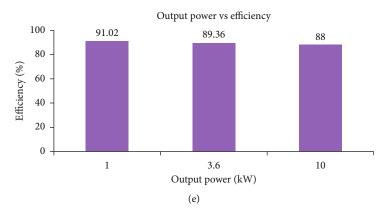

3.2.1. Modes of Operation of Boosted Multilevel DC-Link Converter (BMLDCLC). The proposed Boosted Multilevel DC-Link Converter (BMLDCLC) is designed for 3-phase load, and each phase constitutes six different operating modes. A detailed discussion on its working is given in the following.

(1) Modes of Operations in "R" Phase. During the first and fourth modes of operation, the source voltage " $V_{\rm dc1}$ " is boosted by turning on the switch  $S_a$ . The mathematical expression for " $V_{\rm dc1}$ " is given.

FIGURE 4: Perturb and observe algorithm for MPP tracking.

In Equations (8) and (9), further, the switches  $S_6$  and  $S_7$  are made to behaviour to attain the voltage level " $V_{ob1}$ " at the inverter side.

$$V_{\rm dc1} = L_1 \frac{I_2 - I_1}{T_{\rm on1}},\tag{11}$$

$$V_{\rm dc1} = L_1 \frac{dI_1}{dt}.$$

(12)

The energy stored in the inductor " $E_{i1}$ " can be calculated by using Equation (6).

$$E_{i1} = V_{dc1}.I_{s1}.T_{on1}. (13)$$

At the time,  $t = T_{\text{off}1}$ , switch  $S_a$  is made to switch off, and hence, source current flows through L from  $I_2$

FIGURE 5: Continued.

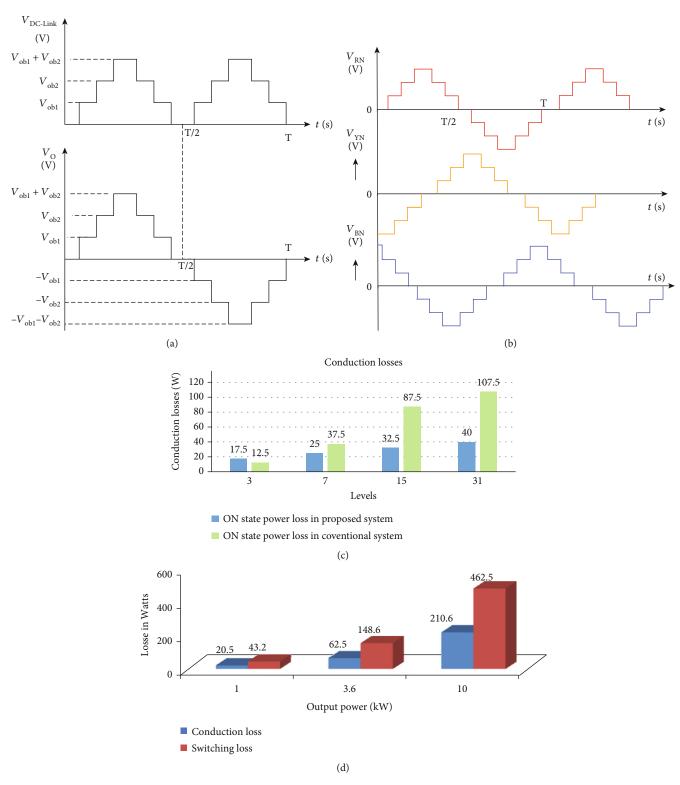

FIGURE 5: (a) Distinctive voltage waveform of  $1\Phi$  seven-level BMLDCLC. (b) Characteristic output voltage waveform of  $3\Phi$  BMLDCLC. (c) Analysis of conduction loss of BMLDCLC. (e) Losses and efficiency.

to  $I_1$ . Therefore, the average output voltage at DC to DC boost converter I can be expressed as Equation (14)

$$V_{ob1} = V_{dc1} + L_1 \frac{dI_{s1}}{T_{off1}}. (14)$$

The energy release  $E_{o1}$  at this instant can be calculated using Equation (15).

$$E_{o1} = (V_{ob1} - V_{dc1})I_{s1}.T_{off1}.$$

(15)

The output voltage of boost converter I of R phase is thus attained as in Equation (16).

$$V_{ob1} = \frac{V_{dc1}}{1 - K_1}. (16)$$

The change in capacitor voltage can be calculated by using Equation (17).

$$\Delta V_{C1} = I_{o1} * \left[ \frac{V_{ob1} - L_1(I_2 - I_1)}{V_{ob1} * f * C_1} \right]. \tag{17}$$

In the second and fifth switching schemes of the chopper unit, the PV source voltage  $V_{\rm dc2}$  is boosted to  $V_{ob2}$  by turning on the switch  $S_b$  in the boost chopper, while  $S_5$  and  $S_8$  are used as a snubber. At this time period,  $t=T_{\rm on2}$ ; switch  $S_b$  of chopper unit-II is turned on to raise the inductor current  $I_3$  and  $I_4$  linearly. The voltage and energy equation corresponding to inductor  $L_2$  is equated in Equations (18) and (19).

$$V_{dc2} = L_2 \frac{I_4 - I_3}{T_{on2}},\tag{18}$$

$$E_{i2} = V_{dc2}.I_{s2}.T_{on2}, (19)$$

where  $I_3$  is the current flowing through the inductor during boost operation in boost chopper unit-II and  $I_2$  is the current flowing through the inductor due to  $S_b$  in boost chopper unit-II. During  $t = T_{\rm off2}$ , switch  $S_b$  of the chopper-II unit gets turned off, because of which,

the current through  $L_2$  linearly falls from  $I_4$  to  $I_3$ . The expression pertaining to the average output voltage and energy stored in the boost chopper IV is given in the following equations:

$$V_{ob2} = V_{dc2} + L_2 \frac{dI_{s2}}{T_{off2}},$$

(20)

$$E_{o2} = (V_{ob2} - V_{dc2})I_{s2}.T_{off2}.$$

(21)

For schemes 3 and 6, the source voltage  $V_{\rm dc1}$  and  $V_{\rm dc2}$  are stepped up to obtain  $V_{ob1}$  and  $V_{ob2}$  by turning on switches  $S_a$  and  $S_b$  of DC-to-DC boost converter. During conduction,  $S_6$  and  $S_8$  act as a snubber to protect the boost converter switches. During the turn-on period  $(t=T_{\rm on3})$ , switches  $S_a$  and  $S_b$  remain conducting to linearly rise the inductor current  $L_1$  and  $L_2$  from  $I_1$  to  $I_2$  and from  $I_3$  to  $I_4$  respectively. The input energy of inductor  $L_1$  from the source voltage  $V_{\rm dc1}$  is given in Equation (22).

$$E_{i3} = (V_{dc1} + V_{dc2}).(I_{s1} + I_{s2}).T_{on3},$$

(22)

The output phase voltage  $(V_{\it RN})$  of BMLDCLC is given as

$$V_{RN} = (V_{ob1} + V_{ob2}) \sin \omega t. \tag{23}$$

(2) Modes of Operations in Y Phase. Similar to the modes of operation of R phase, Y phase DC-link switches  $(S_5', S_6', S_7', \text{ and } S_8')$ , boost chopper switches  $(S_a' \text{ and } S_b')$ , and converter switches  $(S_1', S_2', S_3', \text{ and } S_4')$  are triggered systematically with the phase shift of 120°. The phase voltage equation pertinent to the "Y" phase is given by  $(V_{YN})$ . For Y phase, the scheme of switching the 2<sup>nd</sup> and 5<sup>th</sup> DC-DC boost converter is followed. The PV source voltage  $V_{\text{dc4}}$  is boosted to  $V_{ob4}$  by turning on the switch  $S_b'$  in the DC-DC boost converter where  $S_5'$  and  $S_8'$  are used as snubbers. At time period  $t = T_{\text{on2}}'$ , switch  $S_b'$  of DC-DC boost converter is turned on to raise the inductor current  $I_3'$  to  $I_4'$  linearly. The voltage

FIGURE 6: Modes of operation of proposed 3-phase seven-level BMLDCLC.

and energy equation corresponding to inductor  $L_4$  is expressed as

$$V_{\rm dc4} = L_4 \frac{I'_4 - I'_3}{T'_{\rm on2}},\tag{24}$$

$$E_{i4} = V_{\text{dc4}}.I_{s4}.T'_{\text{on2}}.$$

(25)

At time  $t=T'_{\rm off2}$ , switch  $S'_b$  of the DC-DC boost converter is turned OFF where the inductor current linearly falls from  $I_4$  to  $I_3$ . The expression pertaining to the average output voltage and energy stored in the DC-DC boost converter IV is given in the following equations:

$$V_{ob4} = V_{dc4} + L_4 \frac{dI_{s4}}{T'_{off2}}, \tag{26}$$

Table 1: Specifications of three-phase BMLDLC systems.

| Parameters                                                | Range                          |

|-----------------------------------------------------------|--------------------------------|

| Source voltage unit I ( $V_{ob1}$ )                       | 24 V                           |

| Source voltage II ( $V_{ob2}$ )                           | 48 V                           |

| H-bridge inverter output voltage ( $V_{\mathrm{phmax}}$ ) | 72 V                           |

| H-bridge inverter output voltage ( $V_{L \text{ max}}$ )  | 120 V                          |

| RL load system                                            | $218\Omega$ , $197\mathrm{mH}$ |

| Rated power                                               | 100 W                          |

$$E_{o4} = (V_{ob4} - V_{dc4})I_{s4}.T'_{off2}.$$

(27)

The average output voltage of DC-DC boost converter IV

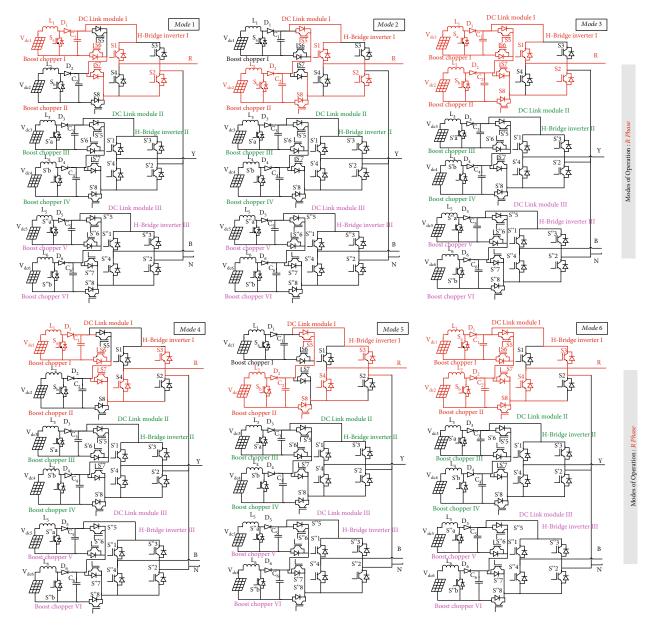

FIGURE 7: (a) Schematic diagram of BMLDCLC-based UPS system. (b) Block diagram of  $3\phi$  seven-level BMLDCLC.

under ideal conditions is expressed in Equation (28).

$$V_{ob4} = \frac{V_{dc4}}{1 - K_2'}. (28)$$

The difference in voltage across the capacitor  $C_4$  is articulated by Equation (29).

$$\Delta V_{C4} = I_{o4} * \left[ \frac{V_{ob4} - L_4 \left( I'_4 - I'_3 \right)}{V_{ob4} * f * C_4} \right], \tag{29}$$

where  $V_{\rm dc4}$  is the DC source voltage IV,  $I_{\rm s4}$  is the DC source current IV,  $K_2'$  is the duty cycle of DC-DC boost

converter IV, and  $V_{ob3}$  is the output voltage of DC-DC boost converter IV.

$$V_{YN} = (V_{ob3} + V_{ob4}) \sin(\omega t - 120^{\circ}).$$

(30)

(3) Modes of Operations in B Phase. Similar to the modes of operation of R and Y phases, B phase DC-link switches  $(S_5'', S_6'', S_7'', \text{ and } S_8'')$ , DC to DC converter II  $(S_a'' \text{ and } S_b'')$ , and inverter switches  $(S_1'', S_2'', S_3'', \text{ and } S_4'')$  are triggered systematically with the phase shift of 240°. For schemes 3 and 6, the source voltage from PV,  $V_{\text{dc3}}$ , and  $V_{\text{dc4}}$  are stepped up to obtain  $V_{ob3}$  and  $V_{ob4}$  by turning on switches  $S_a'$  and  $S_b'$  of DC-DC boost converter. During conduction,  $S_6'$  and  $S_8'$  act as a snubber to protect the boost converter switches. During the turn-on period  $(t = T_{on3}')$ , switches

| Parameter                                                          | Ref [14] | Ref [15] | Ref [17] | Ref [18] | Ref [19] | Ref [20] | Proposed converter |

|--------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|--------------------|

| Number of PV/DC sources required                                   | 3        | 4        | 3        | 3        | 3        | 3        | 2                  |

| Number of power electronic switches/phase                          | 12       | 12       | 12       | 8        | 14       | 18       | 10                 |

| Number of gate drivers                                             | 6        | 6        | 6        | 3        | 6        | 10       | 3                  |

| TSV                                                                | 176.3    | 153.4    | No data  | No data  | No data  | 162.4    | 148.6              |

| Voltage level of inverter                                          | 7        | 9        | 7        | 7        | 7        | 7        | 7                  |

| Series connected DC sources or transformer requirement at inverter | ✓        | ✓        | ✓        | ✓        | ✓        | ✓        | ×                  |

| Efficiency                                                         | 85.3     | 88.4     | 82.1     | No data  | No data  | 86.4     | 90.9               |

Table 2: Qualitative study of proposed work with other popular methods in literature.

H: high; L: low; ✓: mandatory; ×: not mandatory.

$S_a'$  and  $S_b'$  remain conducting to linearly rise the inductor current  $L_3$  and  $L_4$  from  $I_1'$  to  $I_2'$  and from  $I_3'$  to  $I_4'$  respectively. The input energy given to the inductor  $L_3$  from the PV source voltage  $V_{\rm dc3}$  is given in Equation (31).

$$E_{i5} = (V_{dc3} + V_{dc4}).(I_{s3} + I_{s4}).T'_{on3}.$$

(31)

At time instant  $t = T'_{\rm off3}$ , the switches  $S'_a$  and  $S'_b$  are turned off, and the corresponding inductor current  $L_3$  and  $L_4$  current is observed to fall linearly from  $I'_2$  to  $I'_1$  and  $I'_4$  to  $I'_3$ , respectively. The energy released from the inductors  $L_3$  and  $L_4$  to the snubber module can be estimated as follows:

$$E_{o5} = [(V_{ob3} - V_{dc3})I_{s3} + (V_{ob4} - V_{dc4})I_{s4}].T'_{off3}.$$

(32)

The difference in voltage across the capacitors  $C_3$  and  $C_4$  are articulated using Equation (33).

$$\Delta V_{C_{3}} + \Delta V_{C_{4}} = I_{o3} * \left[ \frac{V_{ob3} - L_{3} (I'_{2} - I'_{1})}{V_{ob3} * f * C_{3}} \right] + I_{o4} * \left[ \frac{V_{ob4} - L_{4} (I'_{4} - I'_{3})}{V_{ob4} * f * C_{4}} \right].$$

(33)

$$V_{BN} = (V_{ob3} + V_{ob4}) \sin(\omega t + 240).$$

(34)

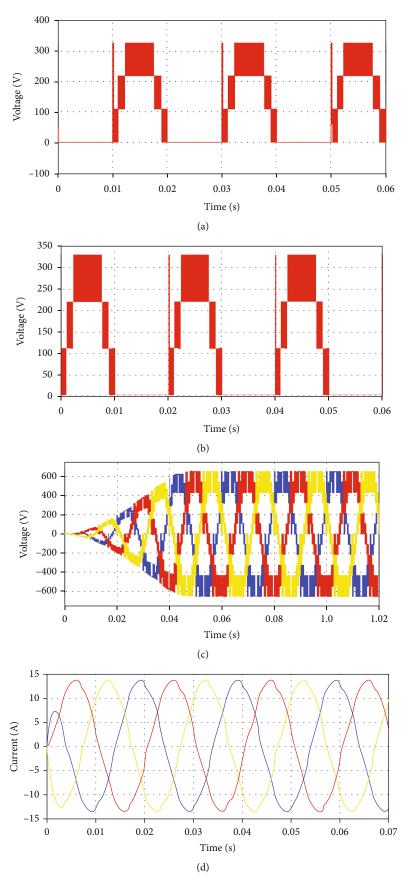

The expected output voltage waveforms for  $1\Phi$  and  $3\Phi$  inverter systems are represented in Figures 5(a) and 5(b), respectively. The equations for estimating the highest phase and line voltages of  $3\phi$  BMLDCLC are as follows.

$$V_{RY} = \sqrt{3}(V_{ob1} + V_{ob2} + V_{ob3} + V_{ob4}) \sin\left(\omega t + \frac{\pi}{6}\right),$$

(35)

$$V_{YB} = \sqrt{3}(V_{ob3} + V_{ob4} + V_{ob5} + V_{ob6}) \sin\left(\omega t - \frac{\pi}{2}\right),$$

(36)

$$V_{BR} = \sqrt{3}(V_{ob5} + V_{ob6} + V_{ob1} + V_{ob2}) \sin(\omega t + \frac{\pi}{2}).$$

(37)

TABLE 3: Load specifications of three-phase BMLDLC.

| RL load |              | Moto    | Motor drive load        |  |  |  |

|---------|--------------|---------|-------------------------|--|--|--|

| Paramet | ter          | Pa      | rameter                 |  |  |  |

| R       | $26\Omega$   | V       | 440 V                   |  |  |  |

| L       | 30 mH        | I       | 12 A                    |  |  |  |

| Z       | $27.6\Omega$ | P       | 5 HP                    |  |  |  |

|         |              | R       | $26\Omega$              |  |  |  |

|         |              | L       | 30 mH                   |  |  |  |

|         |              | Z       | $27.6\Omega$            |  |  |  |

|         |              | Inertia | $0.0146\mathrm{kg.m}^2$ |  |  |  |

For a better understanding of modes of operation with the proposed BMLDCLC system, six different modes of each phase are presented in Figure 6. Further, the equivalent circuit gives a detailed understanding of the on and off states of the power electronic switch to brief current flow in the proposed converter.

3.2.2. Estimation of Power Losses in BMLDCLC. In general, it is important to estimate the total losses that incur in a MLI. Hence, the mathematical formulations pertinent to various category to calculate losses in the proposed BMLDCLC are given in the following: (i) conduction losses, (ii) switching losses, and (iii) overall standing voltage.

# (i) Conduction losses

Conduction losses, in general, are associated with the power electronic switch. Nor the proposed BMLDCLC, it is seen that the conduction loss should be calculated for (i) chopper module, (ii) snubber circuit, and (iii) H-bridge inverters at the output. The mathematical equation to estimate the conduction losses of the chopper unit are premeditated in (38).

$$P_B = 3 * \sum_{k=1}^{N \text{switch}} V_{T,k}.i_{sw,k}.$$

(38)

Conduction losses of snubber module and H-bridge

Figure 8: Continued.

FIGURE 8: (a) Voltage across H-bridge switches  $S_1$  and  $S_2$ . (b) Voltage across H-bridge switches  $S_3$  and  $S_4$ . (c) Output line voltage of  $3\phi$  BMLDCLC. (d) Load current 3-phase BMLDCLC—RL load. (e) Load current 3-phase BMLDCLC—motor drive. (f) Blocking voltage of DC-link switches.

DC to AC converter switches are analyzed as represented in Figure 2(c) and expressed by Equations (39) and (40).

$$P_{\rm DCLM} = \frac{3}{\pi \int_0^{\pi} p_{\rm DCLM}(t) d\omega t},$$

(39)

$$P_H = \frac{3}{\pi \int_0^{\pi} p_h(t) d\omega t}.$$

(40)

The power losses of the suggested system are given by

$$P_{\text{BMLDCLC}} = P_B + P_{\text{DCLM}} + P_H. \tag{41}$$

### (ii) Switching losses

Similar to conduction losses, switching losses of a power electronic switch are also estimated for (i) boost converter and (ii) snubber module. Switching loss pertinent to the DC-DC boost converter is estimated for both on and off time of the power electronic switch, and it is mathematically given in Equations (42) and (43).

$$E_{\text{on},B} = 3 * \sum_{k=1}^{N \text{switch}} V_{sw,k} \cdot i_{sw,k} \cdot t_{\text{on}},$$

(42)

$$E_{\text{off},B} = 3 * \sum_{k=1}^{N \text{switch}} V_{sw,k} \cdot i'_{sw,k} \cdot t_{\text{off}}.$$

(43)

The on state and off state loss of a "k<sup>th</sup>" switch are estimated by using the formulation given in (44) and (45).

$$E_{\text{on},K} = \frac{\left(V_{\text{sw,k}} \cdot i_{\text{sw,k}} \cdot t_{\text{on}}\right)}{6},\tag{44}$$

$$E_{\text{off},k} = \frac{\left(V_{sw,k} \cdot i'_{sw,k} \cdot t_{\text{off}}\right)}{6},\tag{45}$$

where  $E_{\mathrm{on}-k}$  is the energy loss during the switch on,  $E_{\mathrm{off}-k}$  is the energy loss during the switch off, and  $i_t$  is the source current flowing all the way through the power semiconductor switch subsequent to turning on. Further, on estimating the losses in a power electronic switch, the total losses in

Figure 9: Continued.

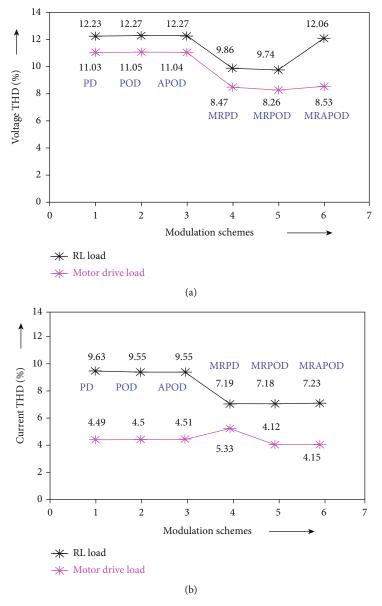

FIGURE 9: THD investigation of the output voltage of  $3\phi$  BMLDCLC. (b) THD investigation of the load current of  $3\phi$  BMLDCLC. (c) Power Signal Density analysis for the output voltage of  $3\phi$  BMLDCLC.

the DC-link module can be calculated. Mathematical formulations to estimate the loss during on and off time are given in Equations (37) and (38), respectively.

$$E_{\text{on,DCLM}} = \sum_{k=1}^{N_{\text{switch}}} E_{\text{on,K}}.$$

(46)

$$E_{\text{off,DCLM}} = \sum_{i=1}^{N_{\text{switch}}} E_{\text{off},K}.$$

(47)

(iii) Overall standing voltage (OSV)

Overall standing voltage (OSV) of the proposed unit is calculated as

$$TSV = \left(\frac{7s^2 + 5s - 2}{2}\right)V. {(48)}$$

The average voltage drop at the switching frequency is 19.53 V and 20.68 V for the rated output voltage system. Hence, the average switching loss is considered as 148.6 W. Hence, the efficiency of the proposed converter is 90.9%. Losses and efficiency analysis are represented in Figure 5(e).

3.3. A Comprehensive Analysis on the Operation of BMLDCLC System in Grid-Connected Mode: Case Study.

| Order of  | $M_a = 0.8$           |                       | $M_a$                    | = 1                   | $M_a = 1.2$              |                       |

|-----------|-----------------------|-----------------------|--------------------------|-----------------------|--------------------------|-----------------------|

| harmonics | Voltage harmonics (%) | Current harmonics (%) | Voltage<br>harmonics (%) | Current harmonics (%) | Voltage<br>harmonics (%) | Current harmonics (%) |

| 3         | 0.29                  | 0.21                  | 0.22                     | 0.09                  | 0.14                     | 0.06                  |

| 5         | 4.69                  | 3.03                  | 4.35                     | 2.92                  | 8.52                     | 4.78                  |

| 7         | 4.62                  | 2.37                  | 3.24                     | 2.15                  | 6.72                     | 2.85                  |

| 9         | 0.07                  | 0.05                  | 0.15                     | 0.05                  | 0.09                     | 0.03                  |

| 11        | 4.58                  | 1.58                  | 2.24                     | 1.06                  | 3.61                     | 1.13                  |

| 13        | 3.67                  | 1.38                  | 1.78                     | 0.8                   | 2.79                     | 1.09                  |

| 15        | 0.09                  | 0.02                  | 0.1                      | 0.02                  | 0.1                      | 0.03                  |

| 17        | 2.34                  | 1.01                  | 1.5                      | 0.25                  | 2.14                     | 0.87                  |

| 19        | 1.98                  | 0.89                  | 1.42                     | 0.21                  | 2.02                     | 0.66                  |

Table 4: Harmonic investigation of three-phase BMLDCLC fed RL load (rated voltage).

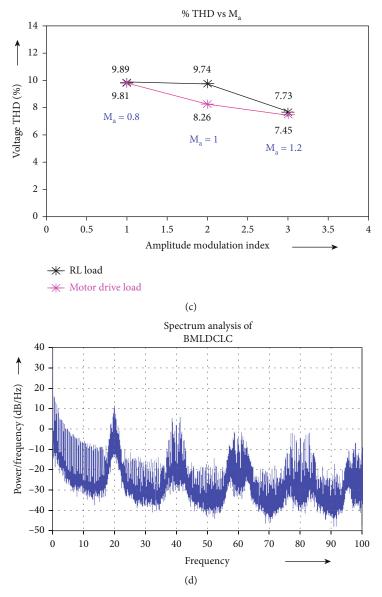

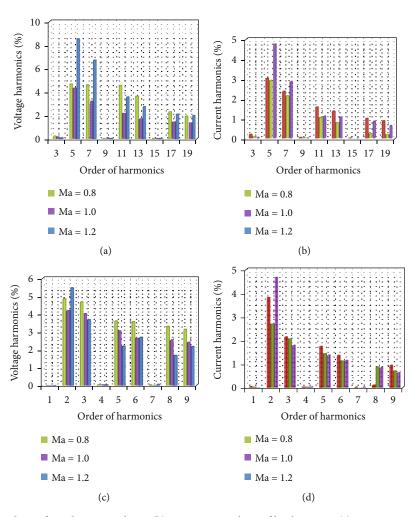

FIGURE 10: (a) Harmonic analysis of rated output voltage. (b) Harmonic analysis of load current. (c) Harmonic analysis of output voltage of 120 V. (d) Harmonic analysis of load current for 120 V output voltage system.

As the proposed converter arrangement is highly encouraged to get connected for a grid-connected mode, a quantitative case study on its operation to grid-connected modes is presented in this section. Design specifications of the rec-

ommended system and the data are related to voltage, and power ratings are represented in Table 1. Also, the schematic of the proposed converter connected to the utility is given in Figure 7(a). From the figure, it is understood that the

| Order of  | $M_a = 0.8$           |                       | $M_a = 1$                |                       | $M_a = 1.2$              |                       |

|-----------|-----------------------|-----------------------|--------------------------|-----------------------|--------------------------|-----------------------|

| harmonics | Voltage harmonics (%) | Current harmonics (%) | Voltage<br>harmonics (%) | Current harmonics (%) | Voltage<br>harmonics (%) | Current harmonics (%) |

| 3         | 0.03                  | 0.05                  | 0.04                     | 0.03                  | 0.02                     | 0.02                  |

| 5         | 4.87                  | 3.82                  | 4.21                     | 2.71                  | 5.46                     | 4.67                  |

| 7         | 4.69                  | 2.16                  | 4.06                     | 2.08                  | 3.69                     | 1.81                  |

| 9         | 0.08                  | 0.04                  | 0.08                     | 0.03                  | 0.07                     | 0.05                  |

| 11        | 3.63                  | 1.76                  | 3.08                     | 1.45                  | 2.22                     | 1.39                  |

| 13        | 3.58                  | 1.38                  | 2.67                     | 1.15                  | 2.72                     | 1.17                  |

| 15        | 0.06                  | 0.03                  | 0.04                     | 0.01                  | 0.09                     | 0.04                  |

| 17        | 3.32                  | 0.12                  | 2.57                     | 0.89                  | 1.71                     | 0.86                  |

| 19        | 3.16                  | 0.96                  | 2.46                     | 0.72                  | 2.20                     | 0.65                  |

Table 5: Harmonic investigation of three-phase BMLDCLC fed RL load (for 120 V).

proposed system has a battery bank and an isolation switch. Note that isolation is mandatory to disconnect it from the utility. Further, the proposed seven-level BMLDCLC connected to a three-phase load system offers five operating modes as follows: (i) bypass mode, (ii) off line mode, (iii) on line mode, (iv) battery-operated mode, and (v) grid-connected mode.

The operating characteristics of various modes in the grid-connected system are discussed in detail as follows:

- (i) In grid-connected mode, subpanel and isolation switches are activated, and the excess power produced by the solar PV panels is imported to the grid

- (ii) In off line mode, the load is operated through a solar fed BMLDCLC system. Note that subpanel and isolation switches are in off state during off line mode

- (iii) In on line mode, the load is operated through solar fed battery-operated BMLDCLC system, and in the same mode, the energy storage device is acquired to completely store the energy by the solar panels through the charge controller

- (iv) Battery operating mode is activated only for emergency and backup loads

In bypass mode, subpanel and isolation switches are activated, and the load is directly connected to the grid. This mode is activated only when solar power is not competent to attend to the load demand. It is noteworthy to mention here as master control manages the operation of the entire system, including the battery bank and the grid-isolation device.

From the specifications of Table 2, it is anticipated that grid-connected systems need nominal power components and PV panels compared to topologies proposed in [14, 15, 17–20]. Thus, it is confirmed that the proposed converter reduces the overall cost for grid-connected UPS applications. The inductor values of  $L_1$  and  $L_2$  pertinent of boost converters 1 and 2 are calculated using the following equations:

$$L_{1} = \frac{V_{\text{dc1}} * (V_{ob1} - V_{\text{dc1}})}{(I_{2} - I_{1}) * f * V_{ob1}}, \tag{49}$$

Table 6: Properties of various metals.

| Material | Specific heat<br>(kJ/kg°C) | Thermal conductivity (W/m°C) |

|----------|----------------------------|------------------------------|

| Aluminum | 0.99                       | 205                          |

| Iron     | 0.45                       | 79.5                         |

| Steel    | 0.46                       | 50.2                         |

| Copper   | 0.39                       | 385                          |

| Brass    | 0.38                       | 109                          |

| Zinc     | 0.38                       | 112                          |

| Water    | 4.18                       | 0.6                          |

| Glass    | 0.84                       | 0.8                          |

| Silver   | 0.23                       | 406                          |

$$L_2 = \frac{V_{\text{dc2}} * (V_{ob2} - V_{\text{dc2}})}{(I_4 - I_3) * f * V_{ob2}}.$$

(50)

To contribute to a fair comparative study, the BMLDCLC system is also presented in Figure 7(b) with a transformer and single-phase supply. However, the system is extremely complicated, and the use of transformers leads to higher costs. Detailed discussions on a transformerless MLI configuration fed UPS system related to (i) transient analysis, (ii) ripple current analysis, (iii) sliding mode controller analysis, and (iv) robustness and multiport analysis can be referred in [31–34].

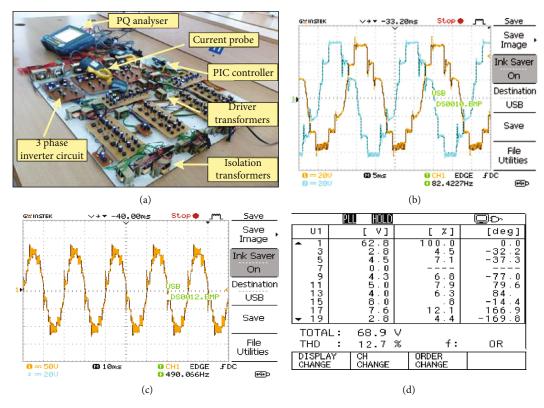

#### 4. Simulation Results and Discussion

The converter is tested with two various loads (i) RL load and (ii) motor drive load. Further, software-based system modelling is performed in a MATLAB Simulink environment with a system configuration of 4 GB RAM and an i3 processor. For simulations, SPV panels are associated in series and parallel approaches to attain the source voltage  $V_{\rm dc1}$ - $V_{\rm dc6}$ . Note that 250 watts PV sources having opencircuit voltage of 36 V and short circuit current as 8 A are used. Further, battery banks are connected in series and parallel approaches to achieve the source voltage of a stepped DC-link hybrid converter and to achieve an uninterrupted power supply for industrial applications. It is noteworthy to mention here that 12 V batteries having 85 AH capacity

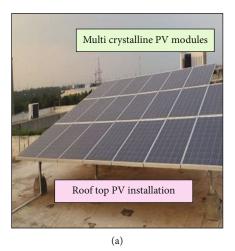

FIGURE 11: (a) Solar plant; (b) experimental analysis with aluminum metal sheet.

are used as a backup to serve in the absence of PV. BMLDCLC initiates its operation as boost chopper; source voltages of 36 V and 72 V are boosted up to 109 V and 216 V, respectively, to achieve the rated voltage of 415 ( $V_{\rm rms}$ ). Furthermore, the power electronic switches of the DC-DC boost converter are fed with a 10 kHz switching frequency to maintain the DC-link voltage. Additional grid-powered storage with an inverter system is also provided to run the backup loads for emergency purposes. The load specifications are represented in Table 3.

The simulation results of the snubber-assisted module are presented in Figures 8(a) and 8(b), respectively. From the acquired waveforms, it is incidental that four switch backend conversions are performed at the zero-crossing points for every 10 ms, as presented in Figure 8(a). Thus, ensuring that switching losses is minimal. In addition, the reproduction of three-phase voltage with definite steps in the waveform gives the judicial validation of the proposed MLI. In order to operate the converter switches efficiently, peak inverse voltage across front-end switches is considered at different levels, as presented in Figures 8(c) and 8(d). Further, the voltages measured at switches give three various DC values to confirm the seven operations of the inverter. Stability analysis has been carried out for the proposed system, and it is inferred that the system is operated in equilibrium with respect to electrical parameters only after 0.05 ms. From Figure 8(c), it is noticed that the steady-state voltage is achieved only after 0.05 ms. To measure the appropriate modulation index with the proposed system, various pulse width modulation (PWM) schemes [35-37] are investigated for both RL load and motor drive load as shown in Figures 9(a) and 9(b), respectively. Over and above, the MCMRPOD-PWM technique is found effective to have reduced THD without filter component, and the same is adopted for the proposed converter topology. Further, the system has also been examined for different modulation indexes  $(M_a)$  like 0.8, 1.0, and 1.2, as shown in Figure 9(c). From the results, it is established that the projected system fed RL load and motor drive load systems generate lower THD (without filter component) values of 7.45% and 7.73%, respectively, for  $M_a = 1.2$ . Also, it is evidenced that

hybrid converter generates 40% higher 5<sup>th</sup> and 7<sup>th</sup>-order voltage and current harmonics. In order to notice the strength of power signals, spectrum analysis has been conducted, and the results are shown in Figure 9(d).

PSD for the inverter voltage of the recommended inverter topology at 10 kHz, 20 kHz, 30 kHz, and 40 kHz is -6 dB/Hz, 12 dB/Hz, -18 dB/Hz, 8 dB/Hz, and -2 dB/Hz, 14 dB/Hz, -16 dB/Hz, and 4 dB/Hz, respectively. The ratio of output voltage in the recommended seven-level inverter fed RL and motor drive load systems at 10 kHz, 20 kHz, 30 kHz, and 40 kHz is 1.25%, 9.95%, 0.31%, 6.27%, and 1.98%, 12.5%, 0.39%, and 3.96%, respectively. Thus, the efficiency of the proposed converter is estimated as 90.9%, and the proposed three-phase stepped DC-link inverter has improved efficiency of 4.7% and 12.9%, respectively, against two-level and three-level boost chopped fed inverter configurations.

For an inverter, individual order harmonic ensures the converter efficiency. Hence, the voltage and current harmonics of the proposed converter are tested and analyzed for three various modulation index  $(M_a)$ . The values pertinent to the order of harmonics are numerically presented in Table 4. For better understanding, a bar chart to measure harmonics in output voltage and current is plotted as shown in Figures 10(a) and 10(b). From the figure, it is noticed that 5<sup>th</sup>-order harmonics get augmented for overmodulation  $(M_a=1.2)$  state. In addition, the average voltage ratio for the proposed topology fed RL and motor drive load system is 4.44% and 4.70%, respectively. The system parameters are designed for the inverter output voltage of 600 V (Vm). The average output voltage of boost chopper units are as follows:

Case 1.

$$V_{ob1} = \frac{36}{(1 - 0.67)}$$

(assuming  $K_1 = 0.67$  for  $M_a = 1$ ), (51)

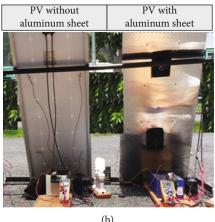

FIGURE 12: (a) Thermal characteristics of solar panel in the month of August. (b) Power generation in the month of January. (c) Power generation in the month of June. (d) Overall power generation for a year.

$$V_{ob1} = \frac{72}{(1 - 0.67)} \text{ (assuming } K_1 = 0.67 \text{ for } M_a = 1), \qquad V_{ob1} = \frac{72}{(1 - 0.73)} \text{ (assuming } K_1 = 0.73 \text{ for } M_a = 1.2),$$

$$V_{ob1} = 216 \text{V}, \qquad V_{ob1} = 280 \text{ V}.$$

(54)

Case 2.

$$V_{ob1} = \frac{36}{(1 - 0.73)}$$

(assuming  $K_1 = 0.73$  for  $M_a = 1.2$ ),

$$V_{ob1} = 140 \text{ V}, \tag{53}$$

Since the provisions to visualize hardware results for rated voltage is not possible, the hardware design is made for 120 V phase voltage. Thus, to validate the proposed system with 120 V as output voltage, the simulation trials of the proposed converter are repeated, and the results pertinent to the modulation index are shown in Figures 10(c) and 10(d). Further, the detailed investigations pertinent to numerical are given in Table 5.

FIGURE 13: (a) Hardware setup of three-phase seven-level BMLDCLC system. (b) Output phase voltage of three-phase BMLDCLC. (c) Output line voltage of three-phase BMLDCLC. (d) THD spectrum.

## 5. Hardware Experimentation

To experiment with the proposed converter, a lab-made prototype model is exclusively constructed. Further, 250 watts PV panels installed on the rooftop of the electrical engineering building of KPR Institute of Engineering and Technology is utilized as the source. In general, SPV panels are nonimmune to geographical and seasonal variations. Further, the overall efficiency gets affected negatively by a rise in temperature. Additionally, excessive heat may significantly increase the output current, which may account for power loss up to 10-22 percentage, hence an attempt to cool PV panels with the help of temperature coefficient. In general, PV panel manufacturers provide a "temperature coefficient" (TC) value for each SPV panel, whose value varies based on manufacturing technology and materials used. This parameter can be used to determine the amount of power loss for each one degree Celsius of temperature rise.

5.1. Design of Thin Aluminum Sheet-Based Cooling System. The panel's temperature is one of the key components to drag the overall power; hence, a new method to reduce the panel temperature is explored by using thin aluminum sheet. Aluminum was chosen for its high thermal conductivity (267 watts per metre-kelvin) and low weight per square. For a fair comparative study, the thermal conductivity and specific heat of various metals are presented in Table 6. Further, the implementation cost was also found economical

with aluminum metal. The experimental setup of the PV system is shown in Figures 11(a) and 11(b), respectively. From Figure 11(b), it is seen that one of the PV panels was used as it is, while the other one was wrapped with thin aluminum sheet in the rear, and the setup was also braced with two DC-cooling fans to enhance the cooling effect. The cooling fain decreases the panel temperature and helps to extract the maximum available power.

The experimental study for cooling is extended for one year, and the instantaneous voltage and power values are recorded. Further, the measure of PV thermal characteristics (PV panel temperature) is measured for the month of August and presented as shown in Figure 12(a). From the figure, it is seen that aluminum-based cooling arrangement has always maintained the temperature in limits compared to the original. To understand the impact of power generation of PV panels with cooling, the power generated from the PV plant is recorded for the months of January and June which is shown in Figures 12(b) and 12(c), respectively. Further, the total power yield for a year is also presented as in Figure 12(d). In all the aforementioned cases, the cooling effect with PV panels had a major impact to improve the power extraction from PV systems. From Figure 12(a), it is inferred that aluminum-based cooling arrangement system has an average of 5°C to 6°C better hear absorption or removal which is equivalent to 12.9% of total heat removal. As a safety measure to protect PV from dust accumulation, panels were coated with hydrophobic nano coating (HNC)

FIGURE 14: Comparative analysis of controlled switches. (b) Comparative analysis of DC sources. (c) Comparative analysis of capacitors. (d) Comparative analysis with different seven-level hybrid converter topologies.

solution. This enabled the PV to prevent from (i) accumulation of water drops, (ii) dust, and (iii) bird droppings over SPV panel surface. In addition, the arrangement has enhanced the surface contact, and the light transfer to the SPV cells was increased, ensuring the higher amount of electricity production. It is noteworthy to mention here that the use of HNN has decreased cleaning of PV panel on average.

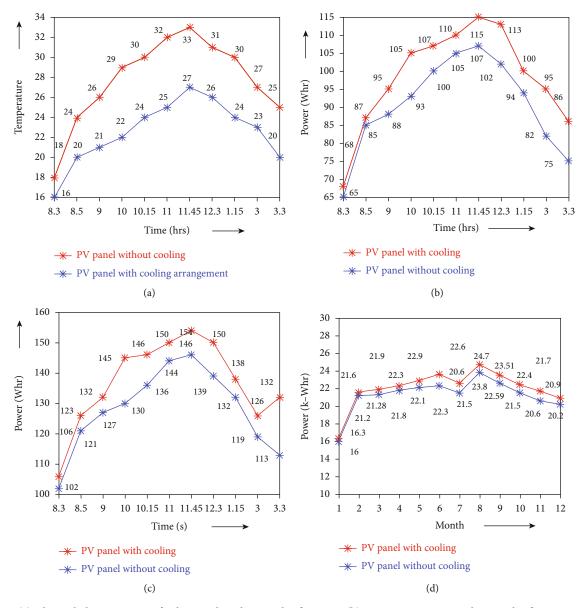

5.2. BMLDCLC Setup. The entire system is designed and implemented as prototype model as represented in Figure 13(a). PIC microcontroller is used for providing gating sequence of the converter. Hardware results (i) output phase voltage ( $V_{\rm RN}$  and  $V_{\rm YN}$ ) and (ii) line voltage of the 3 $\phi$  seven-

level BMLDCLC scheme are shown in Figures 13(b) and 13(c), respectively. To evaluate the virtues and system performance, the operation of proposed BMLDCLC is tested for diverse modulation indices and its electrical parameters are specified in Table 6. From the table, it is inferred that the individual harmonic is within the limit for the modulation index  $M_a = 1.0$ . Thus, the same is recommended for real-time operation. From the examination, it is authenticated that the  $3^{\rm rd}$ ,  $5^{\rm th}$ , and  $7^{\rm th}$ -order harmonics are mitigated through the switching schemes. Furthermore, to authenticate the simulation results, power quality analysis was conducted experimentally and the results are represented in Figure 13(d). From the investigation, the THD of the recommended system is 12.7%.

# 6. Comparative Analysis

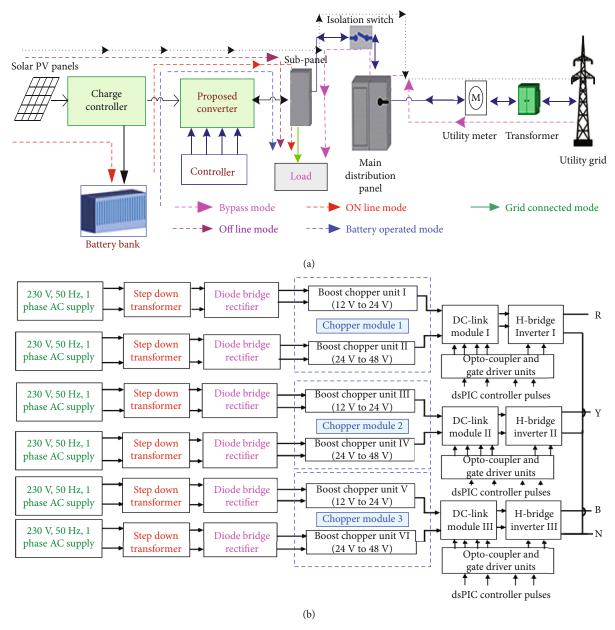

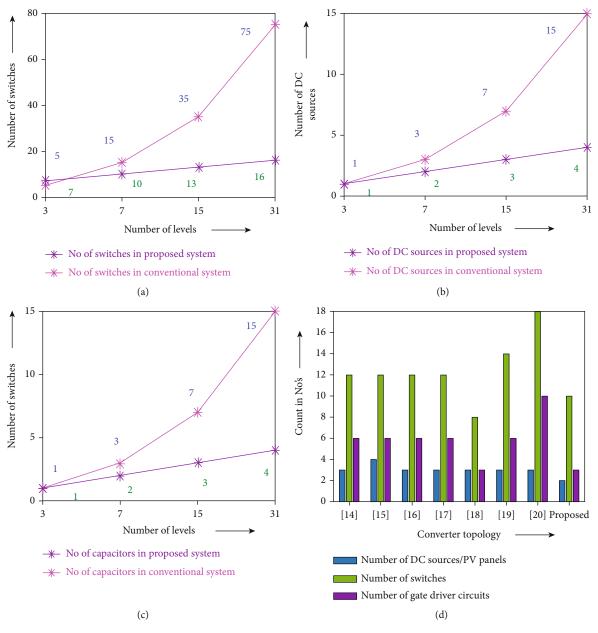

In order to compare the proposed work comprehensively in a common platform, a qualitative assessment of anticipated BMLDCLC topology is made with other literatures as represented in Table 2. Various parameters considered for comparison are as follows: (i) PV panels/DC sources required, (ii) power semiconductor switches used, (iii) gate drivers used, (iv) levels in voltage stress, (v) output voltage levels, and (vi) series connected DC sources. Also, an interesting comparison related to parameters (i) number of power electronic switches, (ii) number of DC sources, and (iii) number of capacitors are considered for conventional MLI (three, seven, fifteen, and thirteen level), and it is compared with proposed inverter topology. This comparison is benchmarked as bar chart and presented in Figures 14(a)-14(c), respectively. From the comparative study, it is inferred that the proposed seven-level BMLDCLC has comparatively utilized 66.66% less (i) switching components, (ii) DC sources, and (iii) capacitors. Further, the same analysis is extended for various literature works, and it is compared with proposed inverter topology as bar chart in Figure 14(d). Yet, the proposed system topology has emerged as one of the best alternatives for existing seven-level inverter configurations. Thus, on overall, the proposed system has greater scope for real-time implementation towards industrial applications is proved. Also, the experimental findings and simulation results confirm that BMLDCLC has conceived greater interest to be as a suitable replacement for existing three-phase seven-level MLI. It is evident from Table 2 that the proposed system requires lesser number of power switches and DC sources. Analysis on the basis of system requirements has been made for various configurations. Hence, from the abovementioned table and analysis part, the authors have given a clear picture about the cost reduction for the proposed system. The comparative study confirms that the proposed 7-level BMLDCLC system has only utilized 33.33% switches compared to other conventional MLI schemes. Hence, the proposed system has the reduced cost of 175.24 US dollars compared with conventional CMLI.

The proposed BMLDCLC configuration required at least six DC sources for synthesizing 7-level three-phase AC output, which is the main limitation of the proposed system over conventional three-phase voltage source inverter system. Also, the proposed BMLDCLC configuration required three boost chopper units for achieving 7-level three-phase AC output. In future, the above constraints can overcome by integrating all the submultilevel modules with a common H-bridge inverter module.

#### 7. Conclusion

A new BMLDCLC topology is proposed in this research work for industrial applications. Further, effectiveness of converter in real-time operating conditions is analyzed using a prototype model, and the following conclusions are arrived.

(i) The BMLDCLC is effective to reduce stress on the primary DC-DC converter since two DC sources are used to serve the DC-link voltage

- (ii) The case study on grid-connected systems reveals the importance of proposed design to serve as a solution for energy management system

- (iii) The comparative study confirms that the proposed 7-level BMLDCLC system has only utilized 33.33% switches compared to other conventional MLI schemes

- (iv) From the power frequency spectrum analysis and perceived output waveforms, the recommended power converter is proved to reduce 41% voltage stress

- (v) From the circuit analysis, it is confirmed that the output voltage is achieved without any series connected DC sources and inverter and transformer. This certainly proves the cost-effectiveness of BMLDCLC compared to conventional MLIs

- (vi) A converter efficiency of 90% is recorded in realtime investigation

#### **Abbreviations**

APOD: Alternate phase opposition disposition

AC: Alternating current

*M<sub>a</sub>*: Amplitude modulation indexBCMLI: Boost cascaded multilevel inverter

CLSPWM: Carrier level shifted pulse width modulation

CDCLHBI: Cascaded DC-link H-bridge inverter

CMLI: Cascaded multilevel inverter CSI: Current source inverter

dsPIC: Digital signal peripheral interface controller

DC: Direct current

FCMLI: Flying capacitor multilevel inverter  $M_f$ : Frequency modulation index IGBT: Insulated gate bipolar transistor

MOSFET: Metal Oxide Semiconductor Field Effect

Transistor

MRAPOD: Modified reference alternate phase opposition

disposition

MRPD: Modified reference phase disposition MRPOD: Modified reference phase opposition

disposition

MLI: Multilevel inverter PD: Phase disposition

POD: Phase opposition disposition PSD: Power spectral density PWM: Pulse width modulation

SPWM: Sinusoidal pulse width modulation

SVM: Space vector modulation

SVPWM: Space vector pulse width modulation

THD: Total harmonic distortion

UPS: Uninterrupted power supply

VSI: Voltage source inverter

ZVS: Zero voltage switching.

# **Data Availability**

The data used to support the findings of this study are included in the article.

#### **Conflicts of Interest**

The authors declare that there is no conflict of interest regarding the publication of this article.

#### References

- [1] J. P. Benner and L. Kazmerski, "Photovoltaics gaining greater visibility," *IEEE spectrum*, vol. 36, no. 9, pp. 34–42, 1999.

- [2] Jie Chang and Jun Hu, "Modular design of soft-switching circuits for two-level and three-level inverters," *IEEE Transactions on Power Electronics*, vol. 21, no. 1, pp. 131–139, 2006.

- [3] N. A. Rahim and J. Selvaraj, "Multistring five-level inverter with novel PWM control scheme for PV application," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 6, pp. 2111–2123, 2010.

- [4] D. Singh, R. Chaudhary, and A. Karthick, "Review on the progress of building-applied/integrated photovoltaic system," *Environmental Science and Pollution Research*, vol. 28, no. 35, pp. 47689–47724, 2021.

- [5] R. Kabilan, V. Chandran, J. Yogapriya, A. Karthick, P. P. Gandhi, and V. Mohanavel, "Short-Term Power Prediction of Building Integrated Photovoltaic (BIPV) System Based on Machine Learning Algorithms," *International Journal of Photoenergy*, vol. 2021, 2021.

- [6] A. Karthick, V. K. Chinnaiyan, J. Karpagam, V. S. Chandrika, and P. R. Kumar, "Optimization of PV-wind hybrid renewable energy system for health care buildings in Smart City," in *Hybrid Renewable Energy Systems*, pp. 213–228, Wiley, 2021.

- [7] A. Ahmed, M. Sundar Manoharan, and J. Park, "An efficient single-sourced asymmetrical cascaded multilevel inverter with reduced leakage current suitable for single-stage PV systems," *IEEE Transactions on Energy Conversion*, vol. 34, no. 1, pp. 211–220, 2019.

- [8] V. Sonti, S. Dhara, P. Kukade, S. Jain, and V. Agarwal, "Analysis for the minimization of leakage and common mode currents in cascaded half-bridge PV fed multilevel inverter," *IEEE Journal of Emerging and Selected Topics in Power Elec*tronics, vol. 7, no. 4, pp. 2443–2452, 2018.

- [9] P. P. Rajeevan, K. Sivakumar, K. Gopakumar, C. Patel, and H. Abu-Rub, "A nine-level inverter topology for mediumvoltage induction motor drive with open-end stator winding," *IEEE Transactions On Industrial Electronics*, vol. 60, no. 9, pp. 3627–3636, 2012.

- [10] E. Babaei, "A Cascade Multilevel Converter Topology With Reduced Number of Switches," *IEEE Transactions On Power Electronics*, vol. 23, no. 6, pp. 2657–2664, 2008.

- [11] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A New Multilevel Converter Topology With Reduced Number of Power Electronic Components," *IEEE Transactions on Industrial Electronics*, vol. 59, no. 2, pp. 655–667, 2011.

- [12] E. Babaei, S. Alilu, and S. Laali, "A New General Topology for Cascaded Multilevel Inverters With Reduced Number of Components Based on Developed H-Bridge," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 8, pp. 3932–3939, 2013.

- [13] E. Villanueva, P. Correa, J. Rodríguez, and M. Pacas, "Control of a single-phase cascaded H-bridge multilevel inverter for grid-connected photovoltaic systems," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 11, pp. 4399–4406, 2009.

- [14] A. Karthick, K. K. Murugavel, and P. Ramanan, "Performance enhancement of a building-integrated photovoltaic module

- using phase change material," *Energy*, vol. 142, pp. 803-812, 2018.

- [15] C. Rech and J. R. Pinheiro, "Hybrid multilevel converters: unified analysis and design considerations," *IEEE Transactions on Industrial Electronics*, vol. 54, no. 2, pp. 1092–1104, 2007.

- [16] A. Karthick, K. Kalidasa Murugavel, L. Kalaivani, and U. Saravana Babu, "Performance study of building integrated photovoltaic modules," *Advances in Building Energy Research*, vol. 12, no. 2, pp. 178–194, 2018.

- [17] S. Kouro, M. Malinowski, K. Gopakumar et al., "Recent advances and industrial applications of multilevel converters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2553–2580, 2010.

- [18] P. Reddy, M. V. N. Gupta, S. Nundy, A. Karthick, and A. Ghosh, "Status of BIPV and BAPV system for less energyhungry building in India—a review," *Applied Sciences*, vol. 10, no. 7, p. 2337, 2020.

- [19] A. Karthick, K. Kalidasa Murugavel, A. Ghosh, K. Sudhakar, and P. Ramanan, "Investigation of a binary eutectic mixture of phase change material for building integrated photovoltaic (BIPV) system," Solar Energy Materials and Solar Cells, vol. 207, 2020.

- [20] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium-voltage multilevel converters—state of the art, challenges, and requirements in industrial applications," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2581–2596, 2010.

- [21] D. S. Pillai, J. P. Ram, V. Shabunko, and Y. J. Kim, "A new shade dispersion technique compatible for symmetrical and unsymmetrical photovoltaic (PV) arrays," *Energy*, vol. 225, article 120241, 2021.

- [22] J. P. Ram and N. Rajasekar, "Investigation of Bacterial Foraging Algorithm Applied for PV Parameter Estimation, Selective Harmonic Elimination in Inverters and Optimal Power Flow for Stability," in *Nature-Inspired Methods for Metaheuristics Optimization*, pp. 135–167, Springer, Cham, 2020.

- [23] T. S. Babu, J. P. Ram, K. Sangeetha, A. Laudani, and N. Rajasekar, "Parameter extraction of two diode solar PV model using fireworks algorithm," *Solar Energy*, vol. 140, pp. 265–276, 2016.

- [24] J. P. Ram, T. S. Babu, T. Dragicevic, and N. Rajasekar, "A new hybrid bee pollinator flower pollination algorithm for solar PV parameter estimation," *Energy Conversion and Management*, vol. 135, pp. 463–476, 2017.

- [25] D. S. Pillai, J. P. Ram, M. S. S. Nihanth, and N. Rajasekar, "A simple, sensorless and fixed reconfiguration scheme for maximum power enhancement in PV systems," *Energy Conversion* and Management, vol. 172, pp. 402–417, 2018.

- [26] R. Uthirasamy, U. S. Ragupathy, and V. Kumar Chinnaiyan, "Structure of boost DC-link cascaded multilevel inverter for uninterrupted power supply applications," *IET Power Electronics*, vol. 8, no. 11, pp. 2085–2096, 2015.

- [27] E. Babaei, H. M. Maheri, and M. Sabahi, "A Transformer-Less DC-DC Converter with High Voltage Conversion Ratio Adopting Inverting Voltage Lift Cell," in *IET Circuits, Devices* & Systems, Wiley, 2021.

- [28] Q. Wang, H. Xi, F. Deng, M. Cheng, and G. Buja, "Design and analysis of genetic algorithm and BP neural network based PID control for boost converter applied in renewable power generations," *IET Renewable Power Generation*, pp. 1–9, 2021.

- [29] I. Poonahela, S. Bayhan, H. Abu-Rub, M. M. Begovic, and M. B. Shadmand, "An effective finite control set-model predictive control method for grid integrated solar PV," *IEEE Access*, vol. 9, pp. 144481–144492, 2021.

- [30] H. Wang, W. Wu, J. Zhu, E. Koutroulis, H. S.-H. Chung, and F. Blaabjerg, "A Novel Dual Buck & Boost Transformer-Less Single-Phase Grid-Tied Inverter," *IEEE Transactions on Power Electronics*, 2021.

- [31] J. K. Park, J. M. Kwon, E. H. Kim, and B. H. Kwon, "High-Performance Transformerless online UPS," *IEEE Transactions* on *Industrial Electronics*, vol. 55, no. 8, pp. 2943–2953, 2008.

- [32] R. P. Torrico-Bascope, D. S. Oliveira, C. G. C. Branco, and F. L. M. Antunes, "A UPS with 110-V/220-V input voltage and high-frequency transformer isolation," *IEEE Transactions on Industrial Electronics*, vol. 55, no. 8, pp. 2984–2996, 2008.

- [33] S. Jiang, D. Cao, Y. Li, J. F. Liu, and F. Z. Peng, "Low-THD, fast transient, and cost-effective synchronous-frame repetitive controller for three-phase UPS inverters," *IEEE Transactions on Power Electronics*, vol. 27, no. 6, pp. 2819–2826, 2012.

- [34] H. Komurcugil, "Rotating-sliding-line-based sliding-mode control for single-phase UPS inverters," *IEEE Transactions* on *Industrial Electronics*, vol. 59, no. 10, pp. 3719–3726, 2012.

- [35] S. Vazquez, J. Rodriguez, M. Rivera, L. G. Franquelo, and M. Norambuena, "Model predictive control for power converters and drives: advances and trends," *IEEE Transactions* on *Industrial Electronics*, vol. 64, no. 2, pp. 935–947, 2017.

- [36] F. Carnielutti, H. Pinheiro, and C. Rech, "Generalized carrier-based modulation strategy for cascaded multilevel converters operating under fault conditions," *IEEE Transactions on Industrial Electronics*, vol. 59, no. 2, pp. 679–689, 2012.

- [37] B. Radadiya, M. Mantani, and T. Trivedi, "Analysis and comparison of PD, POD, APOD PWM techniques for symmetrical multilevel inverters," *International Journal of Advanced Engineering and Research Development*, vol. 4, no. 4, pp. 943–948, 2014.

- [38] M. A. Hosseinzadeh, M. Sarebanzadeh, E. Babaei, M. Rivera, and P. Wheeler, "A Switched-DC Source Sub-Module Multilevel Inverter Topology for Renewable Energy Source Applications," *IEEE Access*, vol. 9, pp. 135964–135982, 2021.