Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.DOI

# An Exhaustive Survey on P4 Programmable Data Plane Switches: Taxonomy, Applications, Challenges, and Future Trends

# ELIE F. KFOURY<sup>1</sup>, (Student Member, IEEE), JORGE CRICHIGNO<sup>1</sup>, (Member, IEEE) AND ELIAS BOU-HARB<sup>2</sup>, (Member, IEEE)

<sup>1</sup>College of Engineering and Computing, University of South Carolina, Columbia, SC 29201 USA (e-mail: ekfoury@email.sc.edu, jcrichigno@ece.sc.edu) <sup>2</sup>The Cyber Center For Security and Analytics, University of Texas at San Antonio, TX 78249 USA, CO 80523 USA (e-mail: elias.bouharb@utsa.edu)

Corresponding author: Elie F. Kfoury (e-mail: ekfoury@email.sc.edu).

This material is based upon work supported by the National Science Foundation under grant numbers 1925484 and 1829698, funded by the Office of Advanced Cyberinfrastructure (OAC).

**ABSTRACT** Traditionally, the data plane has been designed with fixed functions to forward packets using a small set of protocols. This closed-design paradigm has limited the capability of the switches to proprietary implementations which are hard-coded by vendors, inducing a lengthy, costly, and inflexible process. Recently, data plane programmability has attracted significant attention from both the research community and the industry, permitting operators and programmers in general to run customized packet processing functions. This open-design paradigm is paving the way for an unprecedented wave of innovation and experimentation by reducing the time of designing, testing, and adopting new protocols; enabling a customized, top-down approach to develop network applications; providing granular visibility of packet events defined by the programmer; reducing complexity and enhancing resource utilization of the programmable switches; and drastically improving the performance of applications that are offloaded to the data plane. Despite the impressive advantages of programmable data plane switches and their importance in modern networks, the literature has been missing a comprehensive survey. To this end, this paper provides a background encompassing an overview of the evolution of networks from legacy to programmable, describing the essentials of programmable switches, and summarizing their advantages over Softwaredefined Networking (SDN) and legacy devices. The paper then presents a unique, comprehensive taxonomy of applications developed with P4 language; surveying, classifying, and analyzing more than 200 articles; discussing challenges and considerations; and presenting future perspectives and open research issues.

**INDEX TERMS** Programmable switches, P4 language, Software-defined Networking, data plane, custom packet processing, taxonomy.

## I. INTRODUCTION

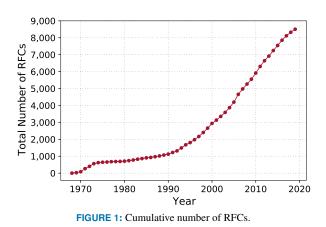

**S** INCE the emergence of the world wide web and the explosive growth of the Internet in the 1990s, the networking industry has been dominated by closed and proprietary hardware and software. Consider the observations made by McKeown [1] and the illustration in Fig. 1, which shows the cumulative number of Request For Comments (RFCs) [2]. While at first an increase in RFCs may appear encouraging, it has actually represented an entry barrier to the network market. The progressive reduction in the flexibility of protocol design caused by standardized requirements, which

cannot be easily removed to enable protocol changes, has perpetuated the status quo. This protocol ossification [3, 4] has been characterized by a slow innovation pace at the hand of few network vendors. As an example, after being initially conceived by Cisco and VMware [5], the Application Specific Integrated Circuit (ASIC) implementation of the Virtual Extensible LAN (VXLAN) [6], a simple frame encapsulation protocol, took several years, a process that could have been reduced to weeks by software implementations<sup>1</sup>

Protocol ossification has been challenged first by Software-defined Networking (SDN) [7, 8] and then by the

recent advent of programmable switches. SDN fostered major advances by explicitly separating the control and data planes, and by implementing the control plane intelligence as a software outside of the switches. While SDN reduced network complexity and spurred control plane innovation at the speed of software development, it did not wrest control of the actual packet processing functions away from network vendors. Traditionally, the data plane has been designed with fixed functions to forward packets using a small set of protocols (e.g., IP, Ethernet). The design cycle of switch ASICs has been characterized by a lengthy, closed, and proprietary process that usually takes years. Such process contrasts with the agility of the software industry.

The programmable forwarding can be viewed as a natural evolution of SDN, where the software that describes the behavior of how packets are processed can be conceived, tested, and deployed in a much shorter time span by operators, engineers, researchers, and practitioners in general. The de-facto standard for defining the forwarding behavior is the P4 language [9], which stands for Programming Protocol-independent Packet Processors. Essentially, P4 programmable switches have removed the entry barrier to network design, previously reserved to network vendors.

The momentum of programmable switches is reflected in the global ecosystem around P4. Operators such as ATT [10], Comcast [11], NTT [12], KPN [13], Turk Telekom [14], Deutsche Telekom [15], and China Unicom [14], are now using P4-based platforms and applications to optimize their networks. Companies with large data centers such as Facebook [16], Alibaba [17], and Google [18] operate on programmable platforms running customized software, a contrast from the fully proprietary implementations of just a few years ago [19]. Switch manufacturers such as Edgecore [20], Stordis [21], Cisco [22], Arista [23], Juniper [24], and Interface Masters [25] are now manufacturing P4 programmable switches with multiple deployment models, from fully programmable or white boxes to hybrid schemes. Chip manufactures such as Barefoot Networks (Intel) [26], Xilinx [27], Pensando [28], Mellanox [29], and Innovium [30] have

<sup>1</sup>The RFC and VXLAN observations are extracted from Dr. McKeown's presentation in [1].

embraced programmable data planes without compromising performance. The availability of tools and the agility of software development have opened an unprecedented possibility of experimentation and innovation by enabling network owners to build custom protocols and process them using protocol-independent primitives, reprogram the data plane in the field, and run P4 codes on diverse platforms. Main agencies supporting engineering research and education worldwide are investing in programmable networks as well. For example, the U.S. National Science Foundation (NSF) has funded FABRIC [31, 32], a national research backbone based on P4 programmable switches. Another project funded by the NSF operates an international Software Defined Exchange (SDX) which includes a P4 testbed that enables international research and education institutions to share P4 resources [33]. Similarly, an European consortium has recently built 2STiC [34], a P4 programmable network that interconnects universities and research centers.

#### A. CONTRIBUTION

Despite the increasing interest on P4 switches, previous work has only partially covered this technology. As shown in Table 1, currently, there is no updated and comprehensive material. Thus, this paper addresses this gap by providing an overview of the evolution of networks from legacy to programmable; describing the essentials of programmable switches and P4; and summarizing the advantages of programmable switches over SDN and legacy devices. The paper continues by presenting a taxonomy of applications developed with P4; surveying, classifying, and analyzing and comparing more than 200 articles; discussing challenges and considerations; and putting forward future perspectives and open research issues.

## **B. PAPER ORGANIZATION**

The road-map of this survey is illustrated in Fig. 2. Section II studies and compares existing surveys on various P4related topics and demonstrates the added value of the offered work. Section III describes the traditional and SDN devices, and the evolution toward programmable data planes. Section IV introduces programmable switches and their features and explains the Protocol Independent Switch Architecture (PISA), a pipeline forwarding model. Section V describes the survey methodology and the proposed taxonomy. Subsequent sections (from Section VI to Section XII) explore the works pertaining to various categories proposed in the taxonomy, and compare the P4 approaches in each category, as well as with the legacy-enabled solutions. Section XIII outlines challenges and considerations extracted and induced from the literature, and pinpoints directions that can be explored in the future to ameliorate the state-of-the-art solutions. Finally, Section XIV concludes the survey. The abbreviations used in this article are summarized in Table 36, at the end of the article.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2021.3086704, IEEE Access

|                                                                                                                        | ı                                                                                                              |                                                                                                                             |                                                                                                              |                                                                                                                                                                               |                                                                                                                    |                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Section I:<br>Introduction                                                                                             | Section II:<br>Related Surveys                                                                                 | Section III:<br>Traditional Control<br>Plane and SDN                                                                        | Section IV:<br>Programmable<br>Switches                                                                      | Section V:<br>Methodology and<br>Taxonomy                                                                                                                                     | Sections VI-XII:<br>Surveyed Work                                                                                  | Section XIII:<br>Challenges and<br>Future Trends                                                                                  |

| Protocol ossification     Evolution of SDN     Rise of P4 and     programmable data     planes     Paper contributions | Comparison of<br>aspects covered in<br>previous surveys     Analysis and<br>limitations of<br>existing surveys | Comparison between<br>traditional, SDN, and<br>programmable devices     Analogy with other<br>domain specific<br>processors | <ul> <li>PISA-based<br/>data plane</li> <li>Programmable<br/>switch features</li> <li>P4 language</li> </ul> | <ul> <li>Survey methodology</li> <li>Proposed taxonomy</li> <li>Year-based distribution<br/>of the surveyed work</li> <li>Implementation<br/>platform distribution</li> </ul> | Background and<br>literature review     Intra-category<br>comparison and<br>discussions     Comparison with legacy | General challenges and<br>Future trends     Memory availability     Arithmetic computations     Network-wide<br>cooperation, etc. |

FIGURE 2: Paper roadmap.

#### **II. RELATED SURVEYS**

The advantages of programmable switches attracted considerable attention from the research community. They were described in previous surveys.

Stubbe et al. [35] discussed various P4 compilers and interpreters in a short survey. This work provided a short background on the P4 language and demonstrated the main building blocks that describe packet processing in a programmable switch. It outlined reference hardware and software programmable switch implementations. The survey lacks critical discussions on the evolution of programmable switches, the features of P4 language, the existing applications, challenges, and the potential future work.

Dargahi et al. [36] focused on stateful data planes and their security implications. There are two main objectives of this survey. First, it introduces the reader to recent trends and technologies pertaining to stateful data planes. Second, it discusses relevant security issues by analyzing selected use cases. The scope of the survey is not limited to P4 for programming the data plane. Instead, it describes other schemes such as OpenState [44], Flow-level State Transitions (FAST) [45], etc. When reviewing the security properties of stateful data planes, the authors described a mapping between potential attacks and corresponding vulnerabilities. The survey lacks critical discussions on the P4 language and its features, the existing applications beyond security, the challenges, and the potential future work.

Cordeiro et al. [37] discussed the evolution of SDN from

OpenFlow to data plane programmability. The survey briefly explained the layout of a P4 program and how it is mapped to the abstract forwarding model. It then listed various compilers, tools, simulators, and frameworks for P4 development. The authors categorized the literature into two categories: 1) programmable security and dependability management; 2) enhanced accounting and performance management. In the first category, the authors listed works pertaining to policy modeling, analysis, and verification, as well as intrusion detection and prevention, and network survivability. In the second category, the authors focused on network monitoring, traffic engineering, and load balancing. The survey only lists a limited set of papers without providing much details or how papers differ from each other. Moreover, the survey was published in 2017, and since then, a significant percentage of P4-related works are missing.

Satapathy et al. [38] presented a limited description about the pitfalls of traditional networks and the evolution of SDN. The report briefly described elements of the P4 language. The authors then discussed the control plane and P4Runtime [46], and enumerated three use cases of P4 applications. The report concludes with potential future work. This work lacks critical discussions on the P4 language and its features, the existing applications, and challenges.

The short survey presented by Bifulco et al. [39] reviews the trends and issues of abstractions and architectures that realize programmable networks. The authors discussed the motivation of packet processing devices in the networking

| Paper | Programma | able switches an | d P4 language |            | Ta         |                              | Discus                    | sions      |                      |

|-------|-----------|------------------|---------------|------------|------------|------------------------------|---------------------------|------------|----------------------|

|       | Evolution | Description      | Features      | Background | Literature | Intra-category<br>comparison | Comparison<br>with legacy | Challenges | Future<br>directions |

| [35]  | ۲         | ۲                | ۲             | 0          | 0          | 0                            | 0                         | 0          | 0                    |

| [36]  | •         | ۲                | ۲             | ۲          | ۲          | 0                            | 0                         | 0          | ۲                    |

| [37]  | •         | ۲                | ۲             | ۲          | •          | 0                            | 0                         | ۲          | ۲                    |

| [38]  | ۲         | ۲                | ۲             | 0          | 0          | 0                            | 0                         | 0          | 0                    |

| [39]  | •         | 0                | 0             | ۲          | ۲          | 0                            | 0                         | ۲          | ۲                    |

| [40]  | •         | 0                | ۲             | 0          | ۲          | 0                            | 0                         | 0          | 0                    |

| [41]  | •         | 0                | 0             | •          | ۲          | 0                            | 0                         | 0          | 0                    |

| [42]  | ۲         | ۲                | 0             | ۲          | ۲          | ۲                            | 0                         | ۲          | ۲                    |

| [43]  | •         | ۲                | ۲             | ۲          | ۲          | 0                            | 0                         | ۲          | ۲                    |

| This  |           |                  |               |            | •          | •                            | •                         | •          |                      |

| paper | -         | J                | J             | Ŧ          | -          | J                            | J                         | -          | -                    |

TABLE 1: Comparison with related surveys.

● Covered in this survey ○ Not covered in this survey ⊙ Partially covered in this survey

VOLUME 4, 2016

field and described the anatomy of a programmable switch. The proposed taxonomy categorizes the literature as statebased, abstraction-based, implementation-based, and layerbased. The layer-based consists of control/intent layer and data plane layer; the implementation-based encompasses software and hardware switches; the abstraction-based includes data flow graph and match-action pipelines; and the state-based differentiates between stateful and stateless data planes. This short survey lacks critical discussions on the existing P4 applications.

Kaljic et al. [40] presented a survey on data plane flexibility and programmability in SDN networks. The authors evaluated data plane architectures through several definitions of flexibility and programmability. In general, flexibility in SDN refers to the ability of the network to adapt its resources (e.g., changes in the topology or the network requirements). Afterwards, the authors identified key factors that influence the deviation from the original data plane given with Open-Flow. The survey concludes with future research directions.

Kannan et al. [41] presented a short survey related to the evolution of programmable networks. This work described the pre-SDN model and the evolution to SDN and programmable data plane. The authors highlighted some features of programmable switches such as stateful processing, accurate timing information, and flexible packet cloning and recirculation. The survey categorized data plane applications into two categories, namely, network monitoring and in-network computing. While this survey listed a considerable number of papers belonging to these categories, it barely explained the operation and main ideas of each paper. Also it lacks many other categories that are relevant in the programmable data plane context.

Tan et al. [42] presented a survey describing In-band Network Telemetry (INT). The survey explained the development stages and classifications of network measurement (traditional, SDN-based, and P4-based). It also outlined some existing applications that leverage INT such as congestion control, troubleshooting, etc. The survey concludes with discussions and potential future work related to INT.

Zhang et al. [43] presented a survey that focuses on stateful data plane. The survey starts with an overview of stateless and stateful data planes, then overviews and compares some stateful platforms (e.g., OpenState, FAST, FlowBlaze, etc.). The paper reviews a handful of stateful data plane applications and discusses challenges and future perspectives.

Table 1 summarizes the topics and the features described in the related surveys. It also highlights how this paper differs from the existing surveys. All previous surveys lack a microscopic comparison between the intra-category works. Also, none of them compare switch-based schemes against legacy server-based schemes. To the best of the authors' knowledge, this work is the first to exhaustively explore the whole programmable data plane ecosystem. Specifically, the paper describes P4 switches and provides a detailed taxonomy of applications using P4 switches. It categorizes and compares the applications within each category as well as with legacy approaches, and provides challenges and future perspectives.

# **III. TRADITIONAL CONTROL PLANE AND SDN**

#### A. TRADITIONAL AND SDN DEVICES

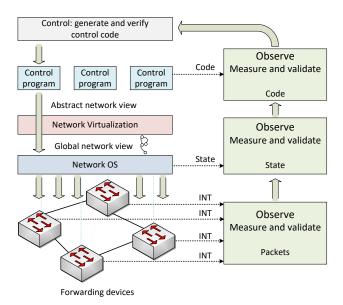

With traditional devices, networks are connected using protocols such as Open Shortest Path First (OSPF) and Border Gateway Protocol (BGP) [47]) running in the control plane at each device. Both control and data planes are under full control of vendors. On the other hand, SDN delineates a clear separation between the control plane and the data plane, and consolidates the control plane so that a single centralized con-

| Feature                                                  | Traditional                        | SDN                                                                                                                        | P4 programmable                                                           |

|----------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Control - data plane separation                          | No clear separation                | Well-defined separation                                                                                                    | Well-defined separation                                                   |

| Control and data plane interface                         | Proprietary                        | Standardized APIs (e.g. OpenFlow)                                                                                          | Standardized (e.g., OpenFlow,<br>P4Runtine) and program-dependent<br>APIs |

| Control and data plane program-<br>dependent APIs        | NA/Proprietary                     | NA/Proprietary                                                                                                             | Target independent                                                        |

| Functionality separation at control plane                | No modular separation of functions | Modular separation: (1) functions<br>to build topology view (state) and<br>(2) algorithms to operate on net-<br>work state | Same as SDN networks                                                      |

| Customization of control plane                           | No                                 | Yes                                                                                                                        | Yes                                                                       |

| Visibility of events at data plane                       | Low                                | Low                                                                                                                        | High                                                                      |

| Flexibility to define and parse new fields and protocols | No flexible, fixed                 | Subject to OpenFlow extensions                                                                                             | Easy, programmable by user                                                |

| Customization of data plane                              | No                                 | No                                                                                                                         | Yes                                                                       |

| ASIC packet processing complexity                        | High, hard-coded                   | High, hard-coded                                                                                                           | Low, defined by user's source code                                        |

| Data plane match-action stages                           | Proprietary                        | OpenFlow assumes in series match-<br>action stages                                                                         | In series and/or in parallel                                              |

| Data plane actions                                       | Protocol-dependent primitives      | Protocol-dependent primitives                                                                                              | Protocol-independent primitives                                           |

| Infield runtime reprogrammability                        | No                                 | No                                                                                                                         | Yes                                                                       |

| Customer support                                         | High                               | Medium                                                                                                                     | Low                                                                       |

| Technology maturity                                      | High                               | Medium                                                                                                                     | Low                                                                       |

TABLE 2: Features, traditional, SDN, and P4 programmable devices.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2021.3086704, IEEE Access

troller can control multiple remote data planes. The controller is implemented in software, under the control of the network owner. The controller computes the tables used by each switch and distributes them via a well-defined Application Programming Interface (API), such as Openflow [48]. While SDN allows for the customization of the control plane, it is limited to the OpenFlow specifications and the fixed-function data plane.

# B. COMPARISON OF TRADITIONAL, SDN, AND PROGRAMMABLE DATA PLANE DEVICES

Table 2 contrasts the main characteristics of traditional, SDN, and P4 programmable devices. In the latter, the forwarding behavior is defined by the user's code. Other advantages include the program-dependent APIs, where the same P4 program running on different targets requires no modifications in the runtime applications (i.e., the control plane and the interface between control and data planes are target agnostic); the protocol-independent primitives used to process packets; the more powerful computation model where the matchaction stages can not only be in series but also in parallel; and the infield reprogrammability at runtime. On the other hand, the technology maturity and support for P4 devices can still be considered low in contrast to traditional and SDN devices.

# C. NETWORK EVOLUTION AND ANALOGY WITH OTHER DOMAIN SPECIFIC PROCESSORS

The introduction of the general-purpose computers in the early 1970s enabled programmers to develop applications running on CPUs. The use of high-level languages accelerated innovation by hiding the target hardware (e.g., x86). In signal processing, Digital Signal Processors (DSPs) were developed in the late 1970s and early 1980s with instruction sets optimized for digital signal processing. Matlab is used for developing DSP applications. In graphics, Graphics Processing Units (GPUs) were developed in the late 1990s and early 2000s with instruction sets for graphics. Open Computing Language (OpenCL) is one of the main languages for developing graphic applications. In machine learning, Tensor Processor Units (TPUs) and TensorFlow were developed in mid 2010s with instruction sets optimized for machine learning.

The programmable forwarding is part of the larger information technology evolution observed above. Specifically, over the last few years, a group of researchers developed a machine model for networking, namely the Protocol Independent Switch Architecture (PISA) [49]. PISA was designed with instruction sets optimized for network operations. The high-level language for programming PISA devices is P4.

#### **IV. PROGRAMMABLE SWITCHES**

#### A. PISA ARCHITECTURE

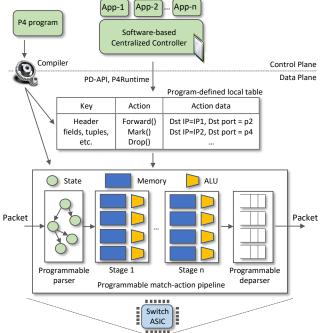

PISA is a packet processing model that includes the following elements: programmable parser, programmable matchaction pipeline, and programmable deparser, see Fig. 3.

VOLUME 4, 2016

FIGURE 3: A PISA-based data plane and its interaction with the control plane.

The programmable parser permits the programmer to define the headers (according to custom or standard protocols) and to parse them. The parser can be represented as a state machine. The programmable match-action pipeline executes the operations over the packet headers and intermediate results. A single match-action stage has multiple memory blocks (tables, registers) and Arithmetic Logic Units (ALUs), which allow for simultaneous lookups and actions. Since some action results may be needed for further processing (e.g., data dependencies), stages are arranged sequentially. The programmable deparser assembles the packet headers back and serializes them for transmission. A PISA device is protocol-independent.

In Fig. 3, the P4 program defines the format of the keys used for lookup operations. Keys can be formed using packet header's information. The control plane populates table entries with keys and action data. Keys are used for matching packet information (e.g., destination IP address) and action data is used for operations (e.g., output port).

## **B. PROGRAMMABLE SWITCH FEATURES**

The main features of programmable switches are [51]:

- Agility: the programmer can design, test, and adopt new protocols and features in significantly shorter times (i.e., weeks or months rather than years).

- Top-down design: for decades, the networking industry operated in a bottom-up approach. Fixed-function ASICs are at the bottom and enforce available protocols and features to the programmer at the top. With programmable switches, the programmer describes protocols and features in the ASICs. Note that the physical layer and parts of the

**TABLE 3:** Comparison between a P4 programmable switch and a fixed-function switch [50].

| Characteristic           | Programmable       | Fixed-function  |  |

|--------------------------|--------------------|-----------------|--|

| Throughput               | 6.4Tb/s            | 6.4Tb/s         |  |

| Number of 100G ports     | 64                 | 64              |  |

| Max forwarding rate      | 4.8B pps           | 4.2B pps        |  |

| Max 25G/10G ports        | 256/258            | 128/130         |  |

| Programmable             | Yes (P4)           | No              |  |

| Power draw               | 4.2W per port      | 4.9W per port   |  |

| Large scale NAT          | Yes (100k)         | No              |  |

| Large scale stateful ACL | Yes (100k)         | No              |  |

| Large scale tunnels      | Yes (192k)         | No              |  |

| Packet buffers           | Unified            | Segmented       |  |

| LAG/ECMP                 | Full entropy, pro- | Hash seed,      |  |

|                          | grammable          | reduced entropy |  |

| ECMP                     | 256-way            | 128-way         |  |

| Telemetry                | Line-rate per flow | SFlow (sampled) |  |

|                          | stats              |                 |  |

| Latency                  | Under 400 ns       | Under 450ns     |  |

MAC layer may not be programmable.

- Visibility: programmable switches provide greater visibility into the behavior of the network. INT is an example of a framework to collect and retrieve information from the data plane, without intervention of the control plane.

- Reduced complexity: fixed-function switches incorporate a large superset of protocols. These protocols consume resources and add complexity to the processing logic, which is hard-coded in silicon. With programmable switches, the programmer has the option to implement only those protocols that are needed.

- Differentiation: the customized protocol or feature implemented by the programmer needs not to be shared with the chip manufacturer.

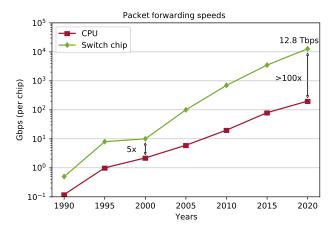

- Enhanced performance: programmable switches do not introduce performance penalty. On the contrary, they may produce better performance than fixed-function switches. Table 3 shows a comparison between a programmable switch and a fixed-function switch, reproduced from [50]. Note the enhanced performance of the former (e.g., maximum forwarding rate, latency, power draw). When compared with general purpose CPUs, ASICs remain faster at switching, and the gap is only increasing as shown in Fig. 4.

The performance gain of switches relies on the multiple dimensions of parallelism, as described next.

- Parallelism on different stages: each stage of the pipeline processes one packet at a time [49]. In Fig. 3, the number of stages is *n*. Implementations may have more than 10 stages on the ingress and egress pipelines. While adding more stages increases parallelism, they consume more area on the chip and increase power consumption and latency.

- Parallelism within a stage: the ASIC contains multiple match-action units per stage. During the match phase, tables can be used for parallel lookups. In Fig. 3, there are four matches (in blue) on each stage that can occur at the same time. An ALU executes one operation over the header field, enabling parallel actions on all fields. Hundreds of

**FIGURE 4:** Evolution of the packet forwarding speeds of the general-purpose CPU and the switch chip (reproduced from [53]).

match-action units exist per stage and thousands in an entire pipeline [49]. Since ALUs execute simple operations and use a simple Reduced Instruction Set Computer (RISC)-type instruction set, they can be implemented in the silicon at a minimal cost.

- Very Long Instruction Words: the set of instructions issued in a given clock cycle can be seen as one large instruction with multiple operations, referred to as Very Long Instruction Word (VLIW). A VLIW is formed from the output of the match tables. A stage executes one VLIW per packet, and each action unit within the stage executes one operation. Thus, for a given packet, one operation per field per stage is applied [52].

- Parallelism on pipelines: the switch chip may contain multiple pipelines per chip, also referred to as pipes. Pipes on a PSA device are analogous to cores on a general purpose CPU. Examples include chips containing two and four pipes [20, 49]. Each pipe is isolated from the other and processes packets independently. Pipes may implement the same functionality or different functionalities.

# C. P4 LANGUAGE

P4 has a reduced instruction set and has the following goals:

• Reconfigurability: the parser and the processing logic can be redefined in the field.

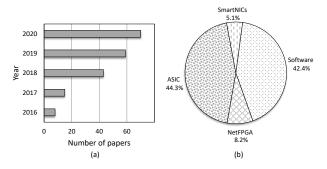

**FIGURE 5:** (a) Distribution of surveyed data plane research works per year. (b) Implementation platform distribution. The shares are calculated based on the studied papers in this survey.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2021.3086704, IEEE Access

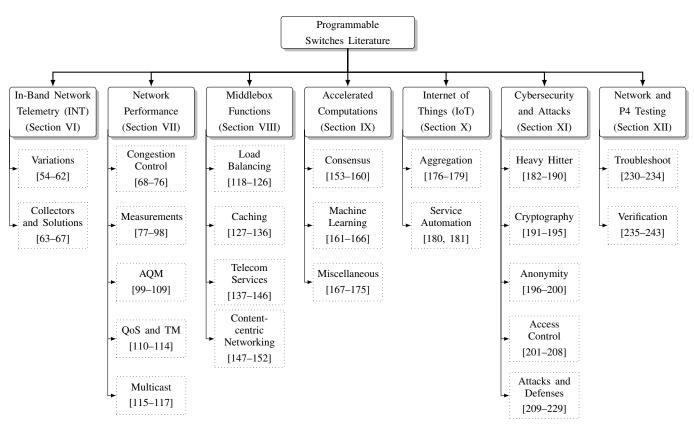

FIGURE 6: Taxonomy of programmable switches literature based upon relevant, explored research areas.

- Protocol independence: the switch is protocol-agnostic. The programmer defines the protocols, the parser, and the operations to process the headers.

- Target independence: the underlying ASIC is hidden from the programmer. The compiler takes the switch's capabilities into account when turning a target-independent P4 program into a target-dependent binary.

The original specification of the P4 language was released in 2014, and is referred to as  $P4_{14}$ . In 2016, a new version of the language was drafted, which is referred to as  $P4_{16}$ .  $P4_{16}$ is a more mature language which extended the P4 language to broader underlying targets: ASICs, Field-Programmable Gate Arrays (FPGAs), Network Interface Cards (NICs), etc.

#### V. METHODOLOGY AND TAXONOMY

This section describes the systematic methodology that was adopted to generate the proposed taxonomy. The results of this literature survey represent derived findings by thoroughly exploring more than 200 data plane-related research works starting from 2016 up to 2020. The distribution of which is summarized in Fig. 5 (a). Note that the survey additionally includes the important works of the first quarter of 2021.

Fig. 5 (b) depicts the share of each implementation platform used in the surveyed papers, grouped by software (e.g., BMv2, PISCES), ASIC (e.g., Tofino, Cavium), NetFPGA (e.g., NetFPGA SUME), and SmartNICs (e.g., Netronome NFP). The graph shows that the vast majority of the works were implemented on software and hardware switches. Note that behavioral software switches (e.g., BMv2 [244]) are not suitable indicators of whether the program could run on a hardware target; they are typically used for prototyping ideas and to foster innovation. On the other hand, non-behavioral software switches (e.g., PICSES [245], derived from Open vSwitch (OVS) [246]) are production-grade and can be deployed in data centers.

It is worth noting that the majority of works implemented on hardware switches are recent; this demonstrates the increase in the adoption of programmable switches by the industry and academia. Currently, to acquire a switch equipped with Tofino chip (e.g., Edgecore Wedge100BF-32 [20]), and to get the development environment and the customer support, a Non-Disclosure Agreement (NDA) with Barefoot Networks (Intel) should be signed. Additionally, the client should attend a training course (e.g., [247]) to understand the architecture and the specifics of the platform. This process is somewhat lengthy and costly, and not every institution is capable of affording it.

The proposed taxonomy is demonstrated in Fig. 6. The taxonomy was meticulously designed to cover the most significant works related to data plane programmability and P4. The aim is to categorize the surveyed works based on various high-level disciplines. The taxonomy provides a clear separation of categories so that a reader interested in a specific discipline. plane can only read the works pertaining to the said discipline.

FIGURE 7: In-band Network Telemetry (INT).

The correctness of the taxonomy was verified by carefully examining the related work of each paper to correlate them into high-level categories. Each high-level category is further divided into sub-categories. For instance, various measurements works belong to the sub-category "Measurements" under the high-level category "Network Performance".

Further, the survey compares the results and the features offered by programmable data plane approaches (intracategory), as well as with those of the contemporary and legacy ones. This detailed comparison is elaborated upon for each sub-category, giving the interested reader a comprehensive view of the state-of-the-art findings of that sub-category. Additionally, the survey presents various challenges and considerations, as well as some current and future trends that could be explored as future work.

#### VI. IN-BAND NETWORK TELEMETRY (INT)

Conventional monitoring and collecting tools and protocols (e.g., ping, traceroute, Simple Network Management Protocol (SNMP), NetFlow, sFlow) are by no means sufficiently accurate to troubleshoot the network, especially with the presence of congestion. These methods provide milliseconds accuracy at best and cannot capture events that happen on microseconds magnitude. Moreover, they cannot provide perpacket visibility across the network.

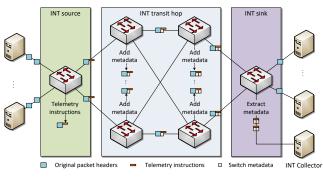

In-band Network Telemetry (INT) [248] is one of the earliest key applications of programmable data plane switches. It enables querying the internal state of the switch and provides fine-grained and precise telemetry measurements (e.g., queue occupancy, link utilization, queuing latency, etc.). INT handles events that occur on microseconds scale, also known as microbursts. Collecting and reporting the network state is performed entirely by the data plane, without any intervention from the control plane. Due to the increased visibility achieved with INT, network operators are able to troubleshoot problems more efficiently. Additionally, it is possible to perform instant processing in the data plane after measuring telemetry data (e.g., reroute flows when a link is congested), without having to interact with the control plane. Fig. 7 shows an INT-enabled network. INT enables network administrators to determine the following:

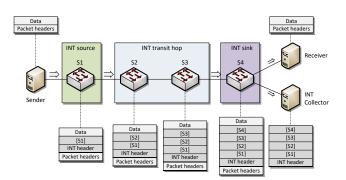

• The path a packet took when traversing the network (see Fig. 8). Such information is difficult to learn using exist-

**FIGURE 8:** Example of how INT can be used to provide the path traversed by a packet in the network. The INT source inserts its label (S1) as well as the INT headers to instruct subsequent switches about the required operations (i.e., push their labels). Finally, switch S4 strips the INT headers from the packet and forwards them to a collector, while forwarding the original packet to the receiver.

ing technologies when multi-path routing strategies (e.g., Equal-cost Multi-Path Routing (ECMP) [249], flowlet switching [250]) are used.

- The matched rules that forwarded the packets (e.g., ACL entry, routing lookup).

- The time a packet spent in the queue of each switch.

- The flows that shared the queue with a certain packet.

The P4 Applications Working Group developed the INT telemetry specifications [251] with contributions from key enablers of the P4 language such as Barefoot Networks, VMware, Alibaba, and others. INT allows instrumenting the metadata to be monitored without modifying the application layer. The metadata to be inserted depends on the use case; for example, if congestion was the main concern to monitor, the programmer inserts queue metadata and transit latency. An INT-enabled network has the following entities: 1) INT source: a trusted entity that instruments with the initial instruction set what metadata should be added into the packet by other INT-capable devices; 2) INT transit hop: a device adding its own metadata to an INT packet after examining the INT instructions inserted by the INT source; 3) INT sink: a trusted entity that extracts the INT headers in order to keep the INT operation transparent for upper-layer applications; and 4) INT collector: a device that receives and processes INT packets.

The location of an INT header in the packet is intentionally not enforced in the specifications document. For example, it

FIGURE 9: Postcard-based Telemetry (PBT).

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2021.3086704. IEEE Access

can be inserted as a payload on top of TCP, UDP, and NSH, as a Geneve option on top of Geneve, and as a VXLAN payload on top of VXLAN.

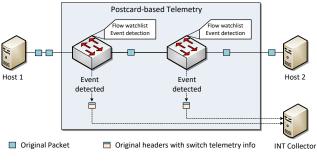

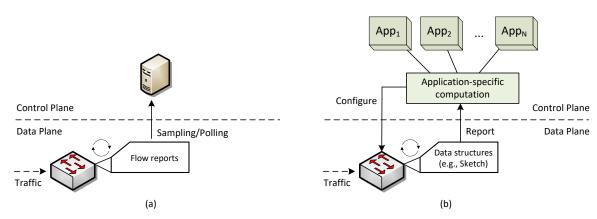

# A. POSTCARD-BASED TELEMETRY (PBT)

INT provides the exact forwarding path, the timestamp and latency at each network node, and other information. Such detailed information is derived by augmenting user packets with data collected by each switch. Postcard-based Telemetry (PBT) is an alternative to INT which does not modify user packets. Fig. 9 shows an example of PBT. As a user packet traverses the network, each switch generates a postcard and sends it to the monitor. The event that triggers the generation of the postcard is defined by the programmer, according to the application's need. Examples include start and/or end of a flow, sampling (e.g., one report per second), packet dropped by the switch, queue congestion, etc.

## **B. INT VARIATIONS**

# 1) Background

Despite the improvements that INT brings compared to legacy monitoring schemes, it introduces bandwidth overhead when enabled unconditionally by network operators. In such scenarios, INT headers are added to every packet traversing the switch, increasing bandwidth overhead which decreases the overall network throughput. To mitigate such limitation, conditional statements are included in the P4 program to send reports only when certain events occur (e.g., queue utilization exceeds a threshold). Such solution requires network operators to adjust thresholds and parameters manually based on the usual network traffic patterns. Consequently, several variations of INT have been developed, aiming at customizing its functionalities and addressing its limitations. Mainly, recent works focus on minimizing the bandwidth overhead of INT by adjusting thresholds and parameters automatically, based on measured traffic patterns and the desired application type.

## 2) Active Network Telemetry

Network telemetry can be actively collected by generating and sending probes to a selected network path. Probes are typically used for minimizing the traffic overhead imposed by regular INT. Liu et al. [54] proposed NetVision, a probing-based telemetry system that actively sends the rightful amount and format of probe packets depending on the telemetry application (e.g., traffic engineering, network visualization). INT-path [57] is another probing-based approach that was the first to achieve network-wide telemetry. Network-wide telemetry provides a global view of the network, which simplifies the management and the control decisions. INT-Path uses Euler trail-based path planning policy to generate probe paths. This mechanism allows achieving non-overlapped probe paths. The idea is to transform network troubleshooting into pattern recognition problems after encoding the traffic status into a series of bitmap images. A subsequent work by Lin et al. [62] that extends NetVision, referred to as NetView [62], was proposed. The objective of NetView is to achieve on-demand network-wide telemetry. NetView considers various telemetry applications, has full coverage, and achieves scalable telemetry.

#### 3) Passive Network Telemetry

Instead of actively sending probes through the network, INT can determine telemetry information passively [252]. The standardized INT [251], which writes telemetry information along the path in packets, is an example of passive network telemetry.

Kim et al. [56] proposed selective INT (sINT), a scheme that dynamically adjusts the insertion frequency of INT headers. A monitoring engine observes changes in consecutive INT metadata and applies a heuristic algorithm to compute the insertion ratio. Marques et al. [58] described the orchestration problem in INT, which is associated with the optimal use of network resources for collecting the state and behavior of forwarding devices through INT. Niu at al. [59] proposed multilayer INT (ML-INT), a system that visualizes

|         | Ref      | Name      | Overhead reduction strategy                            | Network-wide | Operator Intervention                    | Implementation                           |

|---------|----------|-----------|--------------------------------------------------------|--------------|------------------------------------------|------------------------------------------|

|         | [54]     | NetVision | On-demand probing                                      | ×            | High; telemetry through queries          | Mininet                                  |

| Active  | [57]     | INT-Path  | Non-overlapped probe paths generation                  | $\checkmark$ | High; telemetry through queries          | Software (BMv2)                          |

| ¥       | [62]     | NetView   | Application-dependent<br>probing frequency tuning      | $\checkmark$ | High; telemetry through queries          | ASIC (Tofino)                            |

|         | [55] N/A |           | Flow subset selection by the knowledge plan            | ×            | Low; closed-loop network                 | Software (BMv2)<br>w/ ONOS controller    |

|         | [56]     | sINT      | Monitoring ratio adjustment<br>based on network change | ×            | Low; telemetry based on network behavior | Software (BMv2)                          |

| sive    | [58]     | INTO      | Telemetry orchestration<br>based on heuristics         | $\checkmark$ | High; telemetry specified by operators   | N/A                                      |

| Passive | [59]     | ML-INT    | Per-flow packet subset selection through sampling      | ×            | High; telemetry specified by operators   | ASIC (Tofino) and<br>SmartNIC (NFP-4000) |

|         | [61]     | PINT      | Telemetry encoding on<br>multiple packets              | ×            | High; telemetry through queries          | ASIC (Tofino)                            |

|         | [60]     | N/A       | N/A                                                    | $\checkmark$ | High; telemetry through queries          | Wireless Sensor<br>Networks              |

TABLE 4: INT variations comparison.

VOLUME 4, 2016

IP-over-optical networks in realtime. The proposed system encodes INT headers in a subset of packets pertaining to an IP flow. The encoded headers contain metadata that describes statistics of electrical and optical network elements on the flow's routing path. Ben et al. [61] proposed Probabilistic INT (PINT), an approach that probabilistically adds telemetry information into a collection of packets to minimize the per-packet overhead associated with regular INT. Hyun et al. [55] proposed an architecture for self-driving networks that uses INT to collect packet-level network telemetry, and Knowledge-Defined Networking (KDN) to create intelligence to the network management, considering the collected telemetry data. KDN accepts the network information as input and generates policies to improve the network performance. Karaagac et al. [60] extended INT from wired network to wireless network.

#### 4) INT Variations, Comparison, and Discussions

Table 4 compares the aforementioned INT variations solutions. The main motivation behind these solutions is that the majority of applications that leverage INT (e.g., congestion control, fast reroute) only require approximations of the telemetry data and therefore, do not need to gather perpacket per-hop INT information. NetVision, NetView, and INT-Path use probing to reduce the overhead of INT. The main limitation of such approaches is that probing might result in poor accuracy and timeliness as the probes might experience different network conditions than actual packets. All other works collect INT information passively. [55] and sINT select flows based on current network conditions, ML-INT uses a fixed sampling scheme to select a small portion of packets in a flow, and PINT uses a probabilistic approach to encode telemetry on multiple packets. Note that sampling and anomaly-based monitoring might lead to information loss since not all packets are being reported.

Some solutions require manual intervention from the operators to configure the telemetry process. The simplicity of the configuration interface is vital to make the solution easily deployable. Furthermore, some solutions (e.g., NetView, INT-Path) achieve network-wide telemetry. Note that network-wide traffic monitoring incurs additional overhead since multiple switches are being monitored at the same time. Finally, some solutions were implemented on software switches, while other were implemented on hardware. It is important to note that not all software implementations can fit into the pipeline of the hardware.

#### 5) INT, PBT, and Traditional Telemetry Comparison

Table 5 compares INT, PBT, and traditional telemetry. INT has higher potential vulnerabilities than PBT, such as eavesdropping and tampering. Adding extra protective measures (e.g., encryption) is difficult on the fast data path. On the other hand, PBT packets tolerate additional processing to enhance security. The flow tracking process is simpler with INT than with PBT. The latter requires the server receiving INT reports (i.e., INT collector, explained in Section VI-C) to correlate multiple postcards of a single flow packet passing through the network, to form the packet history at the monitor. This process also adds delay in reporting and tracking. Legacy schemes that rely on sampling and polling suffer from accuracy issues, especially when links are congested. INT on the other hand is push-based, has better accuracy, and is more granular (microseconds scale). Reports sent by an INT-capable device contain rich information (e.g., the path a packet took) that can aid in troubleshooting the network. Such visibility is minimal in legacy monitoring schemes. Programmable switches permit reporting telemetry after the occurrence of specific events (e.g., congestion). Moreover, they provide flexibility in programming reactive logic that executes promptly in the data plane. One drawback of INT is

| TABLE 5: In-band, postcard-based, and traditional network | ork telemetry. |

|-----------------------------------------------------------|----------------|

|-----------------------------------------------------------|----------------|

| Feature                | INT                                     | PBT                | Traditional                                            |

|------------------------|-----------------------------------------|--------------------|--------------------------------------------------------|

| User packet modifica-  | Yes                                     | No                 | No                                                     |

| tion                   |                                         |                    |                                                        |

| User packet overhead   | Yes                                     | No                 | No                                                     |

| Potential vulnerabili- | Higher                                  | Lower              | Lower                                                  |

| ties                   |                                         |                    |                                                        |

| Flow tracking process  | Simpler                                 | More complex       | More complex                                           |

| Delay in reporting,    | Lowest                                  | Low                | High                                                   |

| tracking               |                                         |                    |                                                        |

| Microbursts detection  | Yes                                     | Yes                | No                                                     |

| Accuracy               | Higher                                  | Higher             | Lower; especially with congested links                 |

| Reporting type         | Push-based, initiated by the data plane | Push-based         | Polling (e.g., SNMP), initiated by the control plane;  |

|                        |                                         |                    | sampling (e.g., NetFlow), initiated by the data plane  |

| Troubleshoot           | Easier and cheaper                      | Easier and cheaper | Harder and more expensive                              |

| problems               |                                         |                    |                                                        |

| Granularity            | Higher; microseconds scale              | Higher             | Lower; milliseconds scale at best                      |

| Event-based monitor-   | Customizable based on conditions and    | Customizable       | Not possible                                           |

| ing                    | thresholds                              |                    |                                                        |

| Reactive processing    | Faster; reactive processing is executed | Faster             | Slower; reactive processing is executed in the control |

|                        | in the data plane                       |                    | plane                                                  |

| Bandwidth overhead     | High when all packets are reported, low | Higher than INT    | Lowest                                                 |

|                        | when reported based on events           |                    |                                                        |

|                   | Ref  | Name                       | Rate      | Event<br>detection | Processing<br>acceleration | Historical data<br>availability | Analytics | Implementation notes                     |

|-------------------|------|----------------------------|-----------|--------------------|----------------------------|---------------------------------|-----------|------------------------------------------|

|                   | [63] | IntMon                     | 0.1Kpps   | ×                  | ×                          | ×                               | Low       | ONOS-BMv2 subsystem (ONOS 1.6)           |

| Open-<br>source   | [64] | Prometheus<br>INT exporter | 6.4Kpps   | ×                  | ×                          | ×                               | Low       | ONOS P4 Brigade project                  |

| 0 80              | [65] | IntCollector               | 154.8Kpps | $\checkmark$       | Yes; fast path<br>with XDP | $\checkmark$                    | Medium    | C language, XDP for in-kernel processing |

| -be               | [66] | DeepInsight                | N/A       | $\checkmark$       | N/A                        | $\checkmark$                    | High      | SPRINT data plane telemetry (INT.p4)     |

| Closed-<br>source | [67] | BroadView<br>Analytics     | N/A       | ×                  | N/A                        | $\checkmark$                    | High      | Trident 3's in-band telemetry            |

TABLE 6: INT collectors comparison.

that it imposes bandwidth overhead if configured to report for every packet; however, when event-based reports are considered, the bandwidth overhead significantly decreases.

# C. INT COLLECTORS

# 1) Background

An INT collector is a component in the network that processes telemetry reports produced by INT devices. It parses and filters metrics from the collected reports, then optionally stores the results persistently into a database. Since a large number of reports is typically produced in INT, having a high-performance collector is essential to avoid missing important network events. To this end, a number of research works focus on developing and enhancing the performance of INT collectors running on commodity servers. Both open source and closed source INT collectors are proposed in the literature.

#### 2) Open-source

IntMon [63] is an ONOS-based collector application for INT reports. It includes a web-based interface that allows controlling which flows to monitor and the specific metadata to collect. Another INT collector is the Prometheus INT exporter [64], which extracts information from every INT packet and pushes them to a gateway. A database server then periodically pulls information from the gateway. INTCollector [65] is a collector that extracts *events*, which are important network information, from INT raw data. It uses in-kernel processing to further improve the performance. INTCollector has two processing flows; the *fast path*, which processes INT reports and needs to execute quickly, and the *normal path* which processes events sent from the fast path, and stores information in the database.

## 3) Closed-source

Deep Insight [66] is a proprietary solution provided by Barefoot Networks that leverages INT capabilities to provide services such as real-time anomaly detection, congestion analysis, packet-drop analysis, etc. It follows a pay-as-yougrow business model, where customers pay based on the volume of collected telemetry. Another proprietary solution is BroadView Analytics used on Broadcom Trident 3 devices by Broadcom [67]. This solution enables real-time network

VOLUME 4, 2016

latency analysis and facilitates Service Level Agreement (SLA) compliance.

4) INT Collectors Comparison, Discussions, and Limitations

Table 6 compare the aforementioned INT collectors. IntMon and Prometheus INT exporter were among the earliest collectors. Both have low processing rates since they are implemented without kernel nor hardware acceleration. Also, they are very limited with respect to the features they provide (e.g., lack of event detection, limited analytics, historical data unavailability, etc.). Prometheus INT exporter also suffers from increased overhead of sending the data for every INT packet to the gateway, and the potential loss of network events as the database only stores the latest data pulled from the gateway. INTCollector on the other hand has higher rate and uses the eXpress Data Path (XDP) [253] to accelerate the packet processing in the kernel space. It filters the data to be published based on significant changes in the network through its event detection mechanism. DeepInsight Analytics has a modular architecture and runs on commodity servers. It executes the Barefoot SPRINT data plane telemetry which consists of a P4 program (INT.p4) encompassing intelligent triggers. It also provides open northbound RESTful APIs that allow customers to integrate their third-party network management solutions. DeepInsight Analytics is advanced with respect to the features it provides (real-time anomaly detection, congestion analysis, packet-drop analysis, etc.). However, it is a closed-source solution and lacks reports of performance benchmarks.

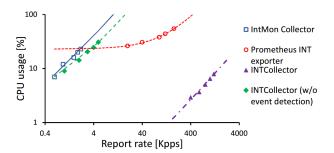

Fig. 10 demonstrates the CPU efficiency of three INT collectors (IntMon, Prometheus INT exporter, and INTCollector) [65]. IntMon has the lowest throughput, and is 57

FIGURE 10: CPU efficiency with the three INT collectors. Source: INTCollector paper [65].

times slower than Prometheus INT. INTCollector on the other hand has the highest throughput and is 27 times faster than Prometheus INT exporter.

# 5) Collectors in INT and Legacy Monitoring Schemes Comparison

Generally, collectors used with both INT and legacy monitoring schemes run on general purpose CPUs, and hence, have comparable performance. INT produces excessive amounts of reports when compared with legacy monitoring schemes (e.g., NetFlow), and therefore, requires having a collector with high processing capability. INT-based collectors are typically accelerated with in-kernel fast packet processing technologies (e.g., XDP) and hardware-based accelerators (e.g., Data Plane Development Kit (DPDK)).

#### D. SUMMARY AND LESSONS LEARNED

Legacy telemetry tools and protocols are not capable of capturing microbursts nor providing fine-grained telemetry measurements. INT was developed to address these challenges; it enables the data plane developer to query with high-precision the internal state of switches. Telemetry data are then embedded into packets and forwarded to a high-performance collector. The collector typically performs analysis and applies actions accordingly (e.g., informs the control plane to update table entries). Current research efforts mainly focus on developing variations of INT to decrease its telemetry traffic overhead, considering the overhead-accuracy tradeoff. Other works aim at accelerating INT collectors to handle large volumes of traffic (in the scale of Kpps). Future work could possibly investigate further improvements for INT such as compressing packets' headers, broadening coverage and visibility, enriching the telemetry information, and simplifying the deployment.

#### **VII. NETWORK PERFORMANCE**

Measuring and improving network performance is critical in nowadays' infrastructures. Low latency and high bandwidth are key requirements to operate modern applications that continuously generate enormous amounts of data [254]. Congestion control (CC), which aims at avoiding network overload, is critical to meet these requirements. Another important concept for expediting these applications is managing the queues that form in routers and switches through Active Queuing Management (AQM) algorithms. This section explores the literature related to measuring and improving the performance of programmable networks.

# A. CONGESTION CONTROL (CC)

#### 1) Background

One of the most challenging tasks in the Internet today is congestion control and collapse avoidance [255]. The difficulty in controlling the congestion is increasing due to factors such as high-speed links, traffic diversity and burstiness, and buffer sizes [68]. Today's CC algorithms aim at shortening delays, maximizing throughput, and improving the fairness and utilization of network resources.

Tremendous amount of research work has been done on congestion control, including end hosts algorithms such as loss-based CC algorithms (e.g., CUBIC [256], Hamilton TCP (HTCP) [257], etc.), model-based algorithms (e.g., Bottleneck Bandwidth and Round-trip Time (BBR) [258, 259]), congestion-signalling mechanisms (e.g., Explicit Congestion Notification (ECN) [260]), data-center specific schemes (e.g., TIMELY [261], Data Center Quantized Congestion Notification (DCQCN) [262], Data Center TCP (DCTCP) [263], pFabric [264], Performance-oriented Congestion Control (PCC) [265], etc.), and application-specific schemes (e.g., QUIC [266]).

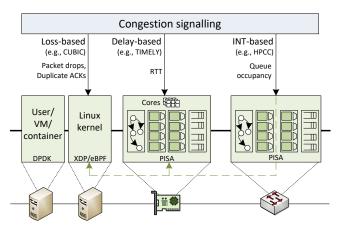

With the advent of programmable data plane switches, researchers are investigating new methods for managing congestion. Such methods can be classified as 1) hybrid CC, where network-assisted congestion feedback is provided for end-hosts; and 2) in-network CC, where the switch performs traffic rerouting, steering, or other congestion control techniques, without modifications on end hosts.

#### 2) Hybrid CC

Handley et al. [68] proposed NDP, a novel protocol architecture for datacenters that aims at achieving low completion latency for short flows and high throughput for longer flows. NDP avoids core network congestion by applying perpacket multipath load balancing, which comes at the cost of reordering. It also trims the payloads of packets, similar to what is done in Cut Payload (CP) [267], whenever the queues of the switches become saturated. Once the payload is trimmed, the headers are forwarded using high-priority queues. Consequently, a Negative ACK (NACK) is generated and sent through high-priority queues so that a retransmission is sent before draining the low priority queue. Similarly, Feldmann et al. [69] proposed a method that uses networkassisted congestion feedback (NCF) in the form of NACKs generated entirely in the data plane. NACKs are sent to throttle elephant-flow senders in case of congestion. The method maintains three separate queues for mice flows, elephant flows, and control packets to ensure fair sharing of resources.

Li et al. [70] proposed High Precision Congestion Control (HPCC), a new CC mechanism that leverages INT-based data added by P4 switches to obtain precise link load information. HPCC computes accurate flow rate by using only one rate update, as opposed to legacy approaches that require a large number of iterations to determine the rate. HPCC provides near-zero queueing, while being almost parameterless. Fig. 11 shows the mechanism of HPCC. The switches add INT

FIGURE 11: HPCC: INT-based high precision congestion control.

|                  | Ref  | Name  | Strategy                                                   | Feedback<br>information | Rerouting    | Traffic<br>separation | End-device<br>modification | Implementation  |

|------------------|------|-------|------------------------------------------------------------|-------------------------|--------------|-----------------------|----------------------------|-----------------|

|                  | [68] | NDP   | Trim packets to headers<br>and priority forward            | NACKs                   | $\checkmark$ | $\checkmark$          | $\checkmark$               | NetFPGA<br>SUME |

| CC               | [70] | HPCC  | Use INT data to compute sending rate                       | INT                     | ×            | ×                     | $\checkmark$               | Tofino          |

| Hybrid           | [69] | NCF   | Throttle elephant flows<br>with NACKs                      | NACKs                   | ×            | $\checkmark$          | ×                          | N/A             |

| Hy               | [71] | N/A   | Pace TCP traffic of<br>elephant flows to safe targets      | Flow count<br>and BW    | ×            | ×                     | $\checkmark$               | BMv2            |

|                  | [72] | EECN  | Remove the receiver from the regular ECN mechanism         | ECN                     | ×            | ×                     | ECN must be activated      | BMv2            |

| ork              | [74] | P4Air | Separate flows according to their congestion control group | N/A                     | ×            | $\checkmark$          | ×                          | Tofino          |

| In-network<br>CC | [73] | N/A   | Monitor queue latency to reroute traffic on congestion     | N/A                     | $\checkmark$ | ×                     | ×                          | BMv2            |

| μ̈               | [76] | P4QCN | Implementation and extension of QCN using P4               | QCN Fb<br>value         | ×            | ×                     | $\checkmark$               | BMv2            |

TABLE 7: Congestion control schemes comparison.

headers to every packet, and then the INT information is piggybacked into the TCP/RDMA Acknowledgement (ACK) packet. The end-hosts then use this information to adjust the sending rate through their smart Network Interface Controllers (NICs).

Kfoury et al. [71] proposed a P4-based method to automate end-hosts' TCP pacing. It supplies the bottleneck bandwidths and the number of elephants flows to senders so that they can pace their rates to safe targets, avoiding filling routers' buffers. Shahzad et al. [72] proposed EECN, a system that uses ECN to signal the occurrence of congestion to the sender without involving the receiver. This is especially useful for networks with high bandwidth-delay product (BDP).

## 3) In-network CC

Turkovic et al. [73] proposed a P4-based method that reroutes flows to backup paths during congestion. The system detects congestion by continuously monitoring the queueing delays of latency-critical flows. The same authors [74] proposed a method that separates the senders based on their congestion control algorithm. Each congestion control uses a separate queue in order to enforce the fairness among its competing flows. Apostolaki et al. [75] proposed FAB, a flow-aware and device-wide buffer sharing scheme. FAB prioritizes flows from port-level to the device-level. The goal of FAB is to minimize the flow completion time for short flows in specific workloads. Geng et al. [76] proposed P4QCN, a flow-level, rate-based congestion control mechanism that improves the Quantized Congestion Notification (QCN). P4QCN improves QCN by alleviating the problems of PFC within a lossless network. Furthermore, P4QCN extends the QCN protocol to IP-routed networks.

# 4) CC Schemes Comparison, Discussions, and Limitations

Table 7 compares the aforementioned CC schemes. NDP and NCF are similar in the sense that both use NACKs as congestion feedback. NDP avoids congestion by applying per-packet multihop load balancing. This approach topologies are asymmetric (e.g., BCube, Jellyfish), especially during heavy network load. Another limitation of NDP is the excessive retransmissions produced by the server. NCF adopted the idea of packet trimming from NDP, but generates NACKs from the trimmed packet and sends it directly to the sender. Such approach removes the receiver from the feedback loop, improving the sender's reaction time. One limitation of NCF is that it requires operators to manually tune some of the predefined parameters (e.g., threshold, queue size, etc.). Additionally, NCF might disclose network congestion information, making it less attractive to operators. Finally, the authors of NCF claim that the approach works with both datacenters and Internet-wide scenarios. However, no implementation results were presented to evaluate the effectiveness of the solution.

works adequately with symmetric topologies, but fails when

HPCC leverages INT data to control network congestion. It enhances the convergence time by using a Multiplicative-Increase Multiplicative-Decrease (MIMD) scheme. Note that previous TCP variants use the Additive-Increase Multiplicative-Decrease (AIMD), which is conservative when increasing the rate, and hence has a slow convergence time. The reason AIMD schemes are slow is that they use a single-bit congestion information (packet loss, ECN). With HPCC, end-hosts can perform aggressive increase as INT metadata encompasses precise link utilization and timely queue statistics. HPCC demonstrated promising results with respect to latency, bandwidth, and convergence time. The authors however did not evaluate the performance of HPCC with conventional congestion control algorithms in the Internet (e.g., CUBIC, BBR). Note that achieving inter-protocol fairness is essential so that the solution is adopted by operators.

The method in [71] uses TCP pacing. Pacing decreases throughput variations and traffic burstiness, and hence, minimizes queuing delays. However, this method works well only in networks where the number of large flows senders is small (e.g., in science Demilitarized Zone (DMZ) [254]).

| Characteristic         | Programmable switch                                                        | <b>End-hosts</b>                                    | Legacy network-assisted (ECN)                                     |

|------------------------|----------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------|

| Accuracy               | Higher, INT-based, microbursts are                                         | Low, packet loss (e.g., CUBIC); Medium,             | Lower with classic ECN; High with                                 |

| -                      | detected and reported                                                      | estimated RTT and btlbw (e.g., BBR)                 | L4S                                                               |

| Required modifications | Switches, end-hosts                                                        | None; distributed nature of AIMD does not           | Minimal if ECN is used (most                                      |

|                        |                                                                            | require storing state of flows                      | equipment have classic ECN imple-<br>mented); High if L4S is used |

| Convergence            | Faster (MIMD)                                                              | Slower (AIMD)                                       | Adequate with ECN; Fast with L4S ECN                              |

| Queue utilization      | Near-zero                                                                  | High; possibility of Bufferbloat (e.g., CU-<br>BIC) | Low                                                               |

| Parameterization       | Few                                                                        | None                                                | Few (e.g., thresholds)                                            |

| Congestion information | Several fields (e.g., queue occupancy, link utilization, flow share, etc.) | Packets drop                                        | 1-bit ECN mark                                                    |

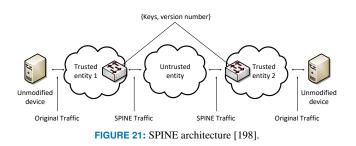

TABLE 8: Congestion control schemes. 1) Programmable Switches (HPCC); 2) end-hosts; and 3) legacy network-assisted (ECN).