# **State of the Art and Future Perspectives in Advanced CMOS Technology**

Henry H. Radamson <sup>1,2,3,4,\*,†</sup>, Huilong Zhu <sup>1,†</sup>, Zhenhua Wu <sup>1,†</sup>, Xiaobin He <sup>1,†</sup>, Hongxiao Lin <sup>1,2,†</sup>, Jinbiao Liu <sup>1,†</sup>, Jinjuan Xiang <sup>1,†</sup>, Zhenzhen Kong <sup>1,†</sup>, Wenjuan Xiong <sup>1,3,†</sup>, Junjie Li <sup>1,3,†</sup>, Hushan Cui <sup>5,†</sup>, Jianfeng Gao <sup>1,†</sup>, Hong Yang <sup>1,†</sup>, Yong Du <sup>1,3,†</sup>, Buqing Xu <sup>1,3,†</sup>, Ben Li <sup>2,†</sup>, Xuewei Zhao <sup>1,6,†</sup>, Jiahan Yu <sup>1,†</sup>, Yan Dong <sup>1,†</sup> and Guilei Wang <sup>1,2,3,\*,†</sup>

- Key Laboratory of Microelectronics Devices & Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China; zhuhuilong@ime.ac.cn (H.Z.); wuzhenhua@ime.ac.cn (Z.W.); hexiaobin@ime.ac.cn (X.H.); linhongxiao@ime.ac.cn (H.L.); liujinbiao@ime.ac.cn (J.L.); xiangjinjuan@ime.ac.cn (J.X.); kongzhenzhen@ime.ac.cn (Z.K.); xiongwenjuan@ime.ac.cn (W.X.); lijunjie@ime.ac.cn (J.L.); gaojianfeng@ime.ac.cn (J.G.); yanghong@ime.ac.cn (H.Y.); duyong@ime.ac.cn (Y.D.); xubuqing@ime.ac.cn (B.X.); zhaoxuewei@ime.ac.cn (X.Z.); yujiahan@ime.ac.cn (J.Y.); dongyan2019@ime.ac.cn (Y.D.)

- <sup>2</sup> Research and Development Center of Optoelectronic Hybrid IC, Guangdong Greater Bay Area Institute of Integrated Circuit and System, Guangzhou 510535, China; liben@giics.com.cn

- <sup>3</sup> Institute of Microelectronics, University of Chinese Academy of Sciences, Beijing 100049, China

- <sup>4</sup> Department of Electronics Design, Mid Sweden University, Holmgatan 10, 85170 Sundsvall, Sweden

- <sup>5</sup> Jiangsu Leuven Instruments, Xuzhou 221300, China; hushan.cui@gmail.com

- <sup>6</sup> School of Cyberscience, University of Science and Technology of China, Hefei 230026, China

- \* Correspondence: rad@ime.ac.cn (H.H.R.); wangguilei@ime.ac.cn (G.W.); Tel.: +86-010-8299-5793 (G.W.)

- + The authors have equally contributed in this article.

Received: 19 June 2020; Accepted: 28 July 2020; Published: 7 August 2020

**Abstract:** The international technology roadmap of semiconductors (ITRS) is approaching the historical end point and we observe that the semiconductor industry is driving complementary metal oxide semiconductor (CMOS) further towards unknown zones. Today's transistors with 3D structure and integrated advanced strain engineering differ radically from the original planar 2D ones due to the scaling down of the gate and source/drain regions according to Moore's law. This article presents a review of new architectures, simulation methods, and process technology for nano-scale transistors on the approach to the end of ITRS technology. The discussions cover innovative methods, challenges and difficulties in device processing, as well as new metrology techniques that may appear in the near future.

Keywords: CMOS; process integration; nano-scale transistors; epitaxy

# 1. Introduction

The down-scaling of complementary metal oxide semiconductor (CMOS) has followed Moore's law for decades, where different parts of the transistor's structure were shrank down by a constant factor in order to obtain lower power consumption [1]. However, the miniaturization trend of CMOS goes very differently nowadays as guided by an international roadmap for devices and systems (IRDS) [2]. By entering the data-centric era [3], the CMOS scaling is focusing more and more on low voltages, cost-effective processes, and high performance to meet the requirements of high-end mobile applications. Thus, several "new techniques" were introduced into the modern devices e.g., channel strain, stress boosters, high- $\kappa$  metal gate, various silicides, etc. Beyond those inventions, the shape of CMOS has already been changed from planar to 3D by overcoming a lot of integration issues [4].

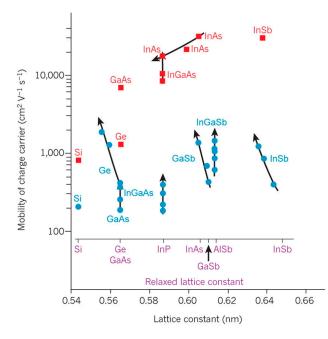

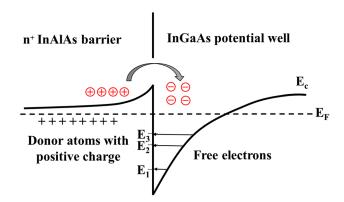

By entering the 10 nm technology node, pure silicon-based channel is being gradually replaced with silicon-germanium (SiGe) or germanium (Ge), and III-V materials, because they have better mobility of- 40,000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for InGaAs (for electrons) and 1900 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for Ge (for holes) compared to 1400 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for electrons and 450 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for holes of silicon [5,6]. Not only are the channel materials changing, but so is device shape, from simple fin-like to fully depleted on insulator or nanowire ones [7].

As a result, the most promising transistor architectures may be fin-on-insulator (FOI) Fin Field-Effect Transistor (FinFET) [8–11], scalloped fin FinFET [12], and NW field effect transistors (FETs) [13–15]. These new transistor designs have shown better control of short channel effects (SCEs), low leakage junctions, and high carrier mobility. One interesting property of FOI FinFET is the advantage that bulk FinFET and SOI technologies are merged in these transistors for a better platform in the technology roadmap. Moreover, a recent report from IMECAS has demonstrated a simple and cost effective fully metallic source and drain (MSD) process for FOI FinFETs with a gate length of 20 nm where I<sub>on</sub> reaches up to 547  $\mu$ A/ $\mu$ m and 486  $\mu$ A/ $\mu$ m for NMOS and PMOS, respectively [9]. These results give an excellent potential solution for future nano-scale transistors. The scalloped fin FinFET including all previous HKMG technology also has a large control area and provides a great improvement of SCEs.

One of the most discussed approach for nano-scale transistors is vertical or horizontal gate-all-around (vGAA or hGAA) FETs. Many reports indicate these GAA-designs as excellent candidate for 3 nm node (and beyond) due to their device characteristics e.g., steep sub-threshold slop (SS), quasi-ballistic transport, and one-dimensional channel structure [13,14].

This article presents the essential issues for design and processing of the advanced nano-scale transistors following to the end of technology roadmap and beyond Moore. The content is divided into four parts:

Part one contains the design of hGAA-FET and vGAA-FET and device simulation including advanced TCAD for nanoscale transistor development.

Part two covers process technology for nanoscale transistors. The discussions include advanced lithography for nano-scale patterning, epitaxy of SiGe as stressor material in S/D of nano-scale transistors or SiGe/Si multilayers for vGAA-FET, dopant implantation and adavanced doping technology, HKMG and metal gate using atomic layer deposition (ALD) technique, strain engineering using Si nitride films, etching of transistor structures and channel release, wet cleaning, BEOL interconnect materials, and process dependent reliability.

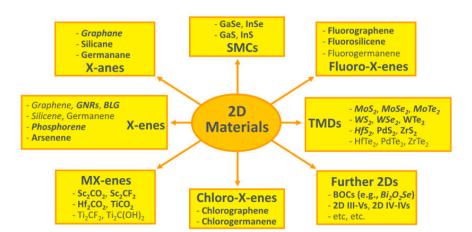

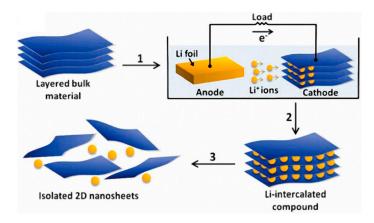

Part three presents the possible channel materials for beyond the Moore era. This part covers the growth and application of III-V materials and 2D crystal for high carrier mobility FinFETs, photodetectors, and sensors.

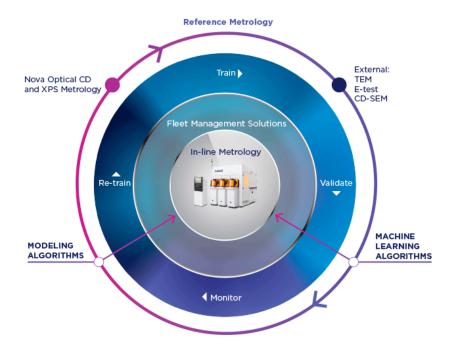

Part four contains metrology technologies, which can be used for in-line monitoring and nano-analysis including advanced electron microscopy, 3D atom force microscope techniques, 3D Atom probe tomography, X-ray techniques, optical critical dimension (CD), and hybrid metrology along with artificial intelligence.

The novelty of this review article stems from the well-organized description of scientific and technical issues of CMOS technology at the present time and in the future. The tactical approach provides unique knowledge for the readers about the challenges and difficulties to design, process, and finally to measure the nanoscale transistors.

#### Part One: Advanced Designs of Nano-Scale Transistors

# 2. This Part Covers the Transistor Designs to the End of Technology Roadmap and Beyond Moore

## 2.1. New Device Structure-Vertical Gate-All-Around FETs

Although FinFET has made enormous contributions to the IC industry since it was proposed in 1999 [16] and introduced into massive production in 2012 at the 22 nm technology node [17], it is

difficult to meet the requirements of the performance and power consumption for further scaling down of device area. Gate-all-around (GAA) FET is a strong candidate for 3 nm technology, owing to its high performance and superiority in the control of SCEs [3,18]. In general, there are two kinds of GAAFETs, namely, horizontal GAAFET (hGAAFET) and vertical GAAFET (vGAAFET), depending on channel orientations. When the channel of a GAAFET is in parallel with the wafer/substrate surface, the transistor is called hGAAFET [19–21], but when the multiple horizontal channels are vertically stacked then the architecture is considered as multiple bridge channel FET (MBCFET) [22]. If the channel of a GAAFET is along the wafer/substrate surface, the GAAFET is called vGAAFET [23].

Intensive studies for hGAAFETs have been done by several research groups [13,15,19–22,24,25]. The first hGAAFET was presented by Colinge et al. [19]. In this field, the nanowire size-effects on the electrical properties were studied in reference [26] while how to enhance single device performance for the hGAAFETs with vertically stacked nanowire/nanosheet were presented in references [13,20,21,27]. In order to reduce parasitic capacitance and improve reliability, inner spacers were introduced [28] for hGAAFETs. High mobility materials, such as strained Si, Ge, InAs, GaAs, and InGaAs, were used to enhance the performance of hGAAFETs [29–32]. Compared with hGAAFETs, vGAAFETs have fewer constraints with respect to gate length and source/drain contact area [33,34] and have great potential for increasing the integration density [19,35]. In this section, we shall mainly focus on reviewing the progress of the vGAAFETs developed to explore novel device architectures and integration schemes more/beyond Moore applications.

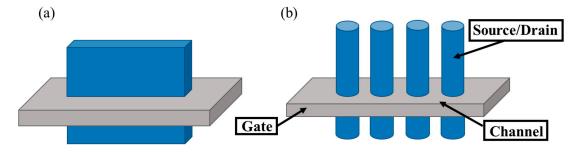

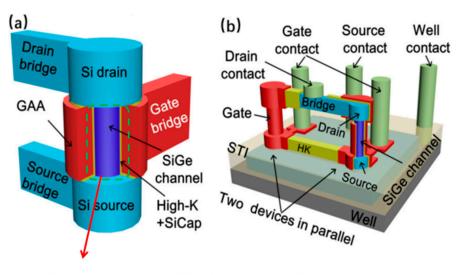

The typical structures of vertical nanosheet and nanowire GAAFETs are shown in Figure 1. The main advantage of vGAAFETs over hGAAFETs is that they have more integration freedom in the vertical direction than hGAAFETs do. The limitations of gate length, spacer width, and source/ drain contact area for hGAAFETs [36] can be relaxed for vGAAFETs and then integration density is increased [37]. It is also good for vGAAFETs to use high mobility materials for their channels, which usually have small carrier effective masses and large tunneling leakage current, since relatively long gate length could be applied.

**Figure 1.** Schematics of vertical gate-all-around field effect transistors (GAAFETs): (**a**) Vertical nanosheet GAAFET and (**b**) vertical nanowire GAAFET. Vertical nanowires—Lg and spacer dimension are decoupled from the gate pitch. Density is determined by distance between the wires. Many process challenges. [37].

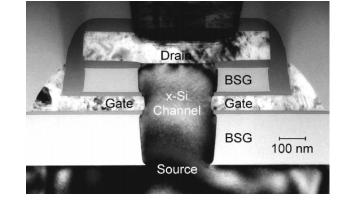

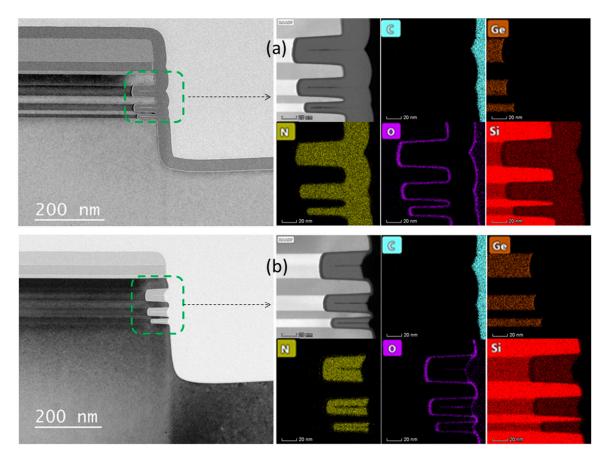

Several fabrication methods for vGAAFETs were proposed, including bottom-up [38–42] and top-down [43–46] based on the ways to form vertical device channels. TEM cross-section for a Si channel vGAAFET with channel-last bottom-up method is shown in Figure 2 [38]. The method concerns forming bottom borosilicate glass (BSG), gate layer, and top BSG layers at first, and then etching channel holes through these layers stopping on the bottom Si. A Si nanowire was formed to refill the hole by selective epitaxial growth from the bottom Si. Source/drain was then formed by an annealing treatment to drive the dopants from the BSG layers into the epitaxial Si and self-align to the gate. The gate length was well controlled by the film deposition. This process is also compatible with the scheme of replacement metal gate. However, when the diameter of the channel hole becomes smaller and the aspect ratio becomes larger, especially for vertically stacked multi-device-layer structures,

this makes it difficult to form high-quality single crystal channel, which is particularly important for high-performance logic circuits.

**Figure 2.** TEM cross-section of a Si channel vertical GAAFET (vGAAFET) with channel last or growth from bottom to top after the formation of bottom bottom borosilicate glass (BSG), gate layer, and top BSG layers [38].

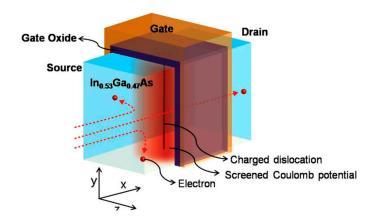

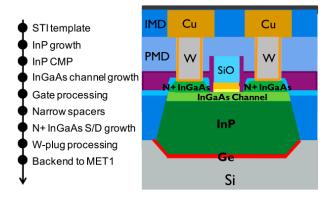

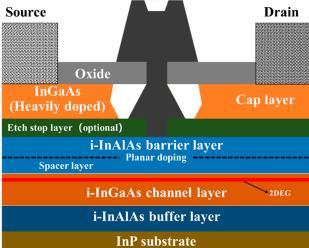

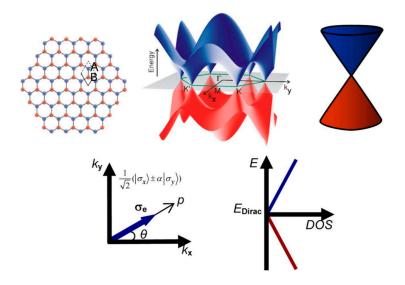

Another bottom-up method forms the channel at first, as several groups have demonstrated in III-V vGAAFET researches [41,47,48]. The vertical channel is highly relevant for III-V materials since they suffer from large off-current due to narrow band gap. The high electron mobility of III-V compounds and relaxation of gate length scaling may offer descent on-off ratio for III-V vGAAFETs. Therefore, III-V compound semiconductors have great potential to replace Si [49] as channel materials for nMOS [50] as shown in Figure 3.

**Figure 3.** Carrier mobility in inversion layers and quantum wells in Si, Ge, and III-V compounds. Red symbols represent electron mobility and blue ones are marked for hole mobility. The electron mobility in the compounds shown in the plots are much higher than that in Si and Ge [50].

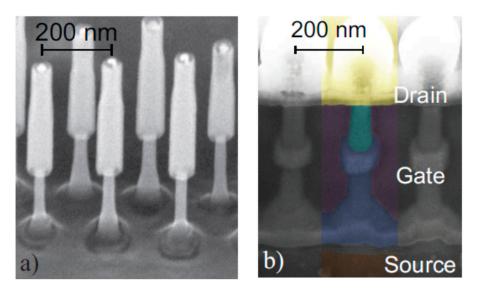

Figure 4 shows tilt views of the SEMs for InAs vGAAFETs fabricated successfully in reference [41]. The InAs vGAAFETs were fabricated on Si (111) wafer. The nanowires were grown using metal organic vapor-phase epitaxy (MOVPE) and using the vapor-liquid-solid (VLS) method from electron-beam

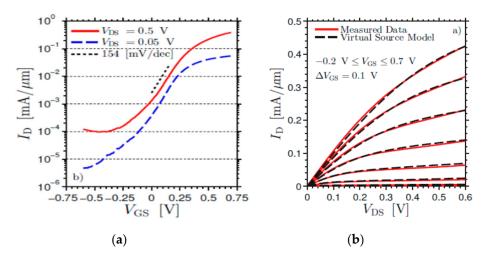

the positions and size of the Au particles as the catalyst were defined. The method of VLS has been widely used to grow nanowires with different materials, such as Si, SiGe, InAs, and InP [51–55]. The transfer and output characteristics of an InAs vGAAFET consisting of 280 nanowires in parallel with a diameter of 28 nm and a gate length of 190 nm are shown in Figure 5, indicating excellent on-and off-device-performance.

**Figure 4.** InAs vGAAFET formed by vapor-liquid-solid (VLS) bottom-up method: (**a**) Nanowires after thinning of channel regions and (**b**) final device structures with high-k metal gates [41].

**Figure 5.** For an InAs vGAAFET consisting of 280 nanowires in parallel with a diameter of 28 nm and gate length of 190 nm: (**a**) Transfer characteristics and (**b**) output characteristics [41].

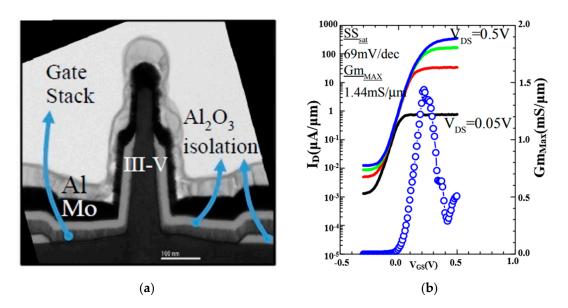

Top-down methods are employed to make vGAAFETs with the better reproducibility and less defectivity than bottom-up. For instances, the size of nanowires can be well defined by lithography while the channel can be formed on entire wafers [45] or high-quality films [31] instead of growth with small catalyst caps [41,55] or through small channel holes [38]. Figure 6a shows an InGaAs nanosheet FET made by top-down method [45]. The transfer characteristics of an In<sub>0.53</sub>Ga<sub>0.47</sub>As vGAAFET with channel length of 100 nm, diameter 35 nm, and CET 1.62 nm, are shown in Figure 6b. For these transistors, excellent *Q*-value (Gm/SS = 21) and I<sub>on</sub> (= 379 uA/um @I<sub>off</sub> = 100 nA) were achieved.

**Figure 6.** In<sub>0.53</sub>Ga<sub>0.47</sub>As nanosheet FET made by a top-down method: (**a**) TEM cross-section and (**b**) the transfer characteristics [45].

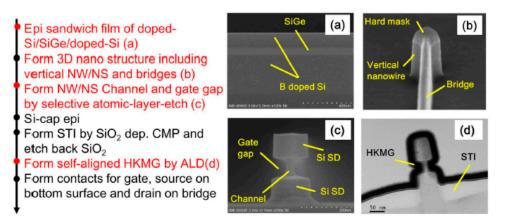

Compared with hGAAFETs, vGAAFETs have many new process issues since their fabrication process is quite different from FinFETs. A key challenge for the fabrication of vGAAFETs is to improve the precise control in vertical direction [56]. Gate length variation of vGAAFETs is a serious problem since it is usually controlled by the time of the etch process after gate metal deposition [39,45]. Although aniostropic deposition of gate metal was used to form 15 nm gate length for relatively large nanowire-pitch (NP) [57] or the deposition of HDP (high-density plasma) oxide film was utilized to determine gate length, it is still a big challenge when the NP is scaled down and the aspect ratio between nanowire height and NP is large. Another method to define gate length is that an electron-beam resist was spun on to cover nanowires and only the top part of the resist was exposed with electron-beam, where the exposed part is removed after development and the thickness of the left part of the resist and dielectric spacer is formed later on to determine the gate length [41]. Since the thickness of the resist is much thicker than gate length, the relatively large process variation, within-wafer or wafer-to-wafer, will be transferred to gate length variation. In addition, nonsymmetrical source/drain and misalignment of gate to channel may pose challenges to circuit design and cause the degradation of device performance. To address those problems, we recently reported a new integration flow to make vGAAFETs with self-aligned high-k metal gates and small effective-gate-length variation [46]. The vGAAFET is called vertical sandwich GAAFET or VSAFET. The integration flow with top-down method and the corresponding structures after key steps are shown in Figure 7.

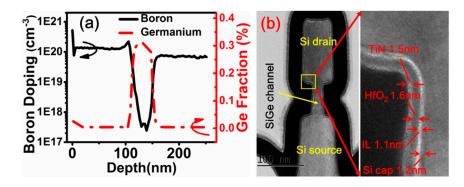

The process starts with deposition of p-Si/i-SiGe/p-Si multi-layer on blank wafers. Later, nano-pillars and arms that connect the nano-pillars are formed by electron-beam lithography and anisotropic etch. A quasi-atomic-layer-etch [58] is developed and applied to selectively etch/recess the i-SiGe layer to form vertical nanowire/nanosheet channels with precise size control but at the same time to achieve gate-position self-alignment. Gate length is well-defined by the thickness of epitaxial i-SiGe layer. SIMS profiles in the p-Si/i-SiGe/p-Si film and TEM cross-sections of an NS pVSAFET are shown in Figure 8. Excellent electrical properties of an NS device with channel thickness of 20 nm and gate length of 60 nm were obtained: Drain-induced barrier lowering (DIBL) = 40 mV, SS<sub>sat</sub> = 86 mV/dec, I<sub>on</sub> = 37.6 uA/um, I<sub>on</sub>/I<sub>off</sub> =  $1.8 \times 10^5$ , and V<sub>d</sub> = 0.65 V.

**Figure 7.** Process flow for vertical sandwich GAAFET (VSAFETs): (**a**) SEM after Si/SiGe/Si, (**b**) SEM tilt image of the 3D nanostructure after Reactive ion etching (**c**) SEM after quasi-atomic layer etching (QALE), and (**d**) TEM after high-k and metal gates (HKMG) deposition [46].

**Figure 8.** (a) Secondary ion mass spectrometry (SIMS) profiles of B and Ge in a p-Si/i-SiGe/p-Si sandwich film [31]. An abrupt B profile was achieved by in-situ doped epitaxial growth. (b) TEM cross-sections of an NS pVSAFET with an Si cap and an HKMG stack with interface layer (IL) = 1.1 nm [46].

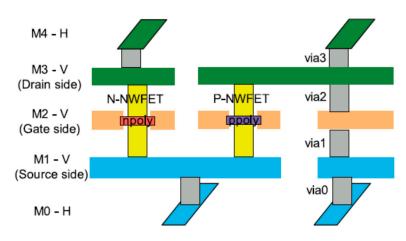

To increase integration density, it is necessary to re-design local and global 3D interconnect [56]. Interconnection delay becomes more and more of a concern for IC performance. Comparing vGAAFETs with hGAAFETs and FinFETs, it was reported that vGAAFETs achieves significant reduction of parasitic capacitance and wirelength [59]. A design of buried interconnects for vGAAFETs was proposed as shown in Figure 9 [60]. In the design, the lateral interconnects, M1-V and M3-V, for both Source and Drain sides were used. It turned out that it is necessary to use M0-H as routing as well as to use layers above M3. The proposed structure is based on the importance of the Source side (S: M1-V) as well as the Drain side (D: M3-V) in the routing perspective. Compared with hGAAFETs, averaged over 12 standard cells, the use of vGAAFETs achieves 22.5%, 14.4%, and 28.4% reductions of area, wirelength, and capacitance, respectively.

Another advantage of vGAAFETs is that it can realize multi-layer vertical stacking, thereby further reducing the area of standard cells. In the simulation of Satish Maheshwaram et al. [60], two-layer stacked vGAAFETs can reduce the area by 20% compared to single-layer CMOS.

Figure 9. A design of buried interconnects for vGAAFETs [59].

# 2.2. Tunneling Field-Effect Transistor (TFET) Approach

To reduce power consumption of metal oxide field effect transistors (MOSFETs) without degradation of device performance, it is required that MOSFETs' operating voltage ( $V_{dd}$ ) and threshold voltage ( $V_{th}$ ) are simultaneously scaled down. The leakage current or power consumption is increased due to lowering  $V_{th}$  if the sub-thresheld swing (SS) of MOSFETs can not be reduced. Therefore, it is desirable to reduce the value or to break thermal dynamic limit, 60 mV/dec, of the SS. The tunneling field-effect transistor (TFET), which is based on band-to-band quantum tunneling, is one of the most promising steep slope devices for low power applications [61].

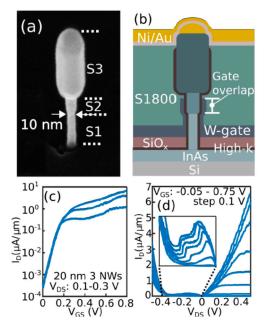

To achieve good tunneling performance, a vertical Si TFET was fabricated and tested in 2000 [62]. Different semiconductor materials (Si or III-V) have been used for TFETs [62,63]. Vertical InAs/InGaAsSb/GaSb nanowire GAA TFETs, whose channel diameters are 20, 15, and 10 nm, were made and operated with SS well below 60 mV/decade [63]. The fabricated devices and I–V characteristics are shown in Figure 10.

**Figure 10.** (**a**–**d**) Tunneling field-effect transistor (TFET) characterization: (**a**) SEM of a nanowire (NW) with a diameter of 10 nm when the layers are S1 = InAs, S2 = InGaAsSb, and S3 = GaSb, and (**b**) schematic of TFET structure in (**a**,**c**) transfer characteristics of a TFET with diameter of 20 nm, and (**d**) output characteristics of the same transistor in (**c**) [63].

#### 3. Advanced TCAD for Nanoscale Transistor Development

Technology computer-aided design (TCAD) takes advantages of physical models and modern high-performance computing powers to provide predictive perspective in semiconductor technology research and manufacturing. TCAD effectively bridges the underlying physics and the realistic device merits, presenting guidelines for process and device development. Advanced TCAD technology with enough accuracy and affordable simulation burden is crucial both in academy and industry so as to address the device physics, shorten the technology development cycle, and reduce the fabrication cost. Furthermore, the industry highly demands the application of TCAD beyond the integration phase into manufacturing, as well as to yield optimization as well. A standard TCAD sequence involves process simulation, device simulation, and circuit simulation. Since this section cannot cover the complete TCAD technologies and their application spaces, it will only focus on typical device models in a hierarchy based on different levels of precision and complexity.

TCAD Device simulation calculates the behavior of electronic devices, e.g., the current–voltage  $(I_d-V_g, I_d-V_d)$  characteristics and frequency response  $(C_{gg}-V_g)$  of a device in general. The devices are defined and characterized mathematically in terms of geometries, materials, connected electrodes, doping, stress profiles, and other relevant physical parameters, all of which may be obtained from measurement, process simulation, or simply manual definition.

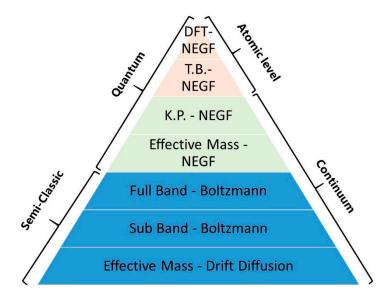

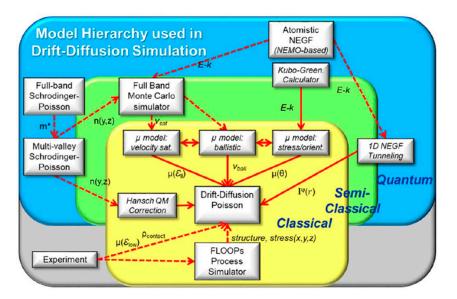

There are two main kernels in TCAD solvers for all levels of the model hierarchy, i.e., (1) the transport equations solver coupled with electrostatic solver, and (2) the Maxwell's equations (Poisson equations) solver for fields (the quasi-static electric fields). The two kernels are coupled strongly and should be solved iteratively and simultaneously. The second kernel is fixed and transferable in versatile applications. Hence, in the following, we focus on the first kernel, which adopts different levels of approximations to leverage the model precision and complexity. V. Moroz from Synopsys Inc. summarized the typical electrostatic and transport models concisely into a pyramid [64], covering industry TCAD to state-of-the-art academical TCAD as shown in the Figure 11. We refer interested readers to the literature for more detailed hierarchy of TCAD device models [65]. Specifically, as the modern transistor dimensions approach atomic scale, the need to calculate quantum effect has impacted electrostatic and transport and evaluating the atomic-scale defects has motivated TCAD from engineering at the bottom in Figure 11 towards research at the top. Rigorous solutions to Schrodinger's equations based on nonequilibrium Green's function (NEGF) and density functional theory (DFT), semi-classical solutions of the BTE and continuum models such as drift-diffusion (DD) are elaborated to a multi-scale TCAD Framework [66].

Figure 11. Illustration of the hierarchy of technology computer-aided design (TCAD) device models [64].

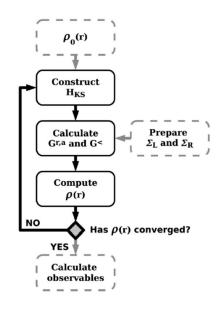

The most accurate but complex TCAD solution is the DFT within the NEGF formalism (DFT-NEGF) method. In addition, the incorporation of DFT enables parameter free simulations, which is suitable for path-finding research of emerging technologies. The basic idea of the DFT-NEGF method is firstly proposed by H. Guo's group [67], i.e., using the DFT to calculate the Hamiltonian and electrostatic properties of the device; using NEGF to determine non-equilibrium statistics for constructing density matrix; and using real Space numerical methods to calculate transport properties and the boundary conditions for open device structures (see Figure 12). It has been used as the standard approach to model nonequilibrium quantum transport in atomic nanostructures. High precision can be achieved by using DFT-NEGF, but at the expense of computational issues in speed and memory limits.

**Figure 12.** Illustration of the density functional theory (DFT)-nonequilibrium Green's function (NEGF) self-consistent simulation flow [67].

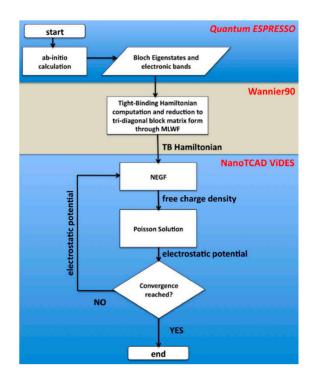

As a compromise, one may apply semi-empirical k.p (KP) or tight-binding (TB) models in combination with NEGF. Excellent transport results can be obtained if the KP/TB parameters are properly chosen. Many KP/TB-NEGF codes with various capabilities and accuracies have been developed [68,69]. A standard open source TB-NEGF framework is proposed as shown in Figure 13 [70]. Several open commercial tools are also available [71,72]. Such schemes are able to solve quantum transport problems involving extended number atoms rather than DFT-NEGF method. Such KP/TB/DFT-NEGF models have been widely implemented in simulating the quantum transport phenomena in ultral scaled MOSFET as well as in studying the tunneling field effect transistors.

Despite high accuracy in rigorous atomistic techniques such as the aforementioned DFT-NEGF and KP/TB-NEGF, they remain too computationally expensive for massive TCAD support in applications of industry development. Drift-diffusion (DD) is still preferred if the empirical parameters are obtained from advanced calibration scheme. In practice, for a given node, the optimized geometry is almost reached and only small variation in device dimension is needed. Thus, the design window is relatively narrow, in which calibrated DD model can give enough predictive results even for sub 10 nm node transistors. Moreover, the DD solution in well established in industry TCAD. It can handle realistic device geometries and is smoothly connected with the process and topographical simulations data. Due to the above reasons, the DD model still plays the most import role in engineering and continues to be infused with more rigorous models by advanced calibrations, affording the fast and massive data for industry technology development. For example, Figure 14 shows the DD TCAD solution proposed by Intel [73].

Figure 13. Illustration of the tight-binding (TB)-NEGF self-consistent simulation flow [70].

Figure 14. Ilustration of the advanced drift-diffusion (DD) calibration and applications [73].

In brief, with shrinking device dimensions, the demand for accurate solvers of the coupled NEGF transport equations and atomistic-based electrostatic calculations has grown significantly. TCAD device models of different complexity, precision, and accuracy are developed in many academic groups or offered in various commercial tools. Depending on specific device scales, a quantum-mechanical model or a semi-classical model has to be adopted properly. Once the computational issues of speed and memory limits are relieved, the application domain of quantum transport modes can be further extended.

# Part Two: Process Technology for Nano-Scale Transistors

#### 4. Advanced Lithography Process

The most important goals for advanced lithography technology are to create more clear patterns and high reproducibility at the same time. For 20-nm and 14-nm node technologies, 193 nm ArF immersion with multiple patterns has been mainly used in manufacturing of FinFETs [74]. Further, 193 nm immersion with self-aligned double pattern (SADP) and self-aligned quadruple pattern (SAQP) technology aim for 7 nm technology nodes and below. For the advanced technology node, quadruple patterning needs to be further developed as it will increase the cost and process variation.

Extreme ultraviolet (EUV) lithography has been recognized as a promising candidate for the manufacturing of semiconductor devices as line space (LS) and contact hole (CH) patterns for 7 nm node and beyond. EUV lithography enables the use of single mask exposure instead of double or quadruple exposure. It will replace some key process steps in the flow for multiple patterning.

EUV lithography is ready for introduction and running in volume for technology development, but it still faces several challenges. EUV is used for metal layers at 7 nm node, but it still requires double patterning with traditional immersion steppers for some metal layers. Single-patterning process production cost is greatly lower than that of "multi-patterning" of repeated pattern circuits.

# 4.1. EUV Source

EUV light source power is critical for high-volume manufacture (HVM) and it can limit the large-scale use of EUV technique. To increase the throughput in HVM, the resist sensitivity to the 13.54-nm wavelength radiation of EUV needs to be improved while the line-width roughness (LWR) specification has to be kept to a few nanometers. In principle, an EUV stepper using a 250 W source and 25 mJ/cm<sup>2</sup> resist, sensitivity should be able to process at least 100 wafer-per-hour (wph), which makes it an affordable price to match with the other lithography techniques. In fact, it is the light source that enables economical production capacity of the exposure tools. The latest ASML NXE3400B system can generate 250 W EUV light source [75]. This enables wafer throughput up to 140 wph where it is already acceptable for HVM [76]. In any way, the source power subsystems toward 500 W will be a huge challenge, but its wph will be about twice the current value [77,78].

# 4.2. EUV Resist

For mass production of integrated circuit transistors, EUV resist requires significantly increased sensitivity and improved line edge roughness (LWR) and local critical CD uniformity (LCDU). The main challenge of EUV resist is to simultaneously require ultra-high resolution (R), low line edge roughness (LER), and high dose sensitivity (S) [79]. EUV photoresist materials need to be improved with better resolution and simpler chemistry to reduce photon shot noise and chemical fluctuations. The placement of individual molecules of chemical amplification material starts to be important at 10 nm node. Resolution, line edge roughness, and sensitivity are the critical technical issues of EUV lithography, and they are correlated with each other as shown in Figure 15. For example, when the LER increases, high dose is needed and, consequently, the resolution becomes low. The higher absorption requires the use of thinner resist, which mitigates the issue of line collapse.

Figure 15. Resolution, dose sensitivity, and their relationship to low line edge roughness (LER).

Another critical challenge is to develop suitable EUV photoresists at high resolution with high sensitivity and low line-width roughness (LWR) for the reduced film thickness needed for high-NA by its reduced depth of focus ( $\sim 1/NA^2$ ) [80].

# 4.3. EUV Mask

The EUV mask infrastructure requires the manufacture of defect-free photomasks, where the ability to inspect photochemical masks is a key success factor [81,82]. Since protective films cannot currently be used in EUV lithography, other measures need to be taken to deal with the contamination that may be introduced during mask transportation and when they are being used. The defects caused by this contamination will significantly reduce the yield in the manufacturing of semiconductor devices [83].

In EUV system, the masks operate in reflective mode. In order to obtain maximum reflection, we need to improve material for the EUV absorber on the mask (which is mirror-like).

The multilayer Mo/Si are used as high-reflectance mirrors. The key properties include the roughness and inter-diffusion depth at the Mo-Si interfaces [84]. TaBN is the current standard absorber, but for low-*k1* imaging, the three-dimensional effect of the mask results in degradation of image contrast and edge placement errors. Mitigation of 3D-mask effects is a requirement for high-NA (0.55) EUV lithography [85]. Both the absorber and the reflective multilayer parts of the EUV mask contribute to the 3D-mask effects. 3D-mask effects are more predominant for wafer image quality. EUV pellicle is a thin membrane and it has been enabled to prevent reticle from contamination and particles, both inside and outside the scanner environment. However, it will cause reduction in throughput because of the absorption of EUV photons in the pellicle [86]. Therefore, throughput will be reduced when EUV mask pellicle is used.

# 4.4. Change to High-NA

A 3nm EUV single-patterning process was available through a next-generation "high-NA" lithographsssssy system, which increases the numerical aperture (NA) of the EUV projection optics, from 0.33 to 0.55 [87]. As shown in Figure 16, ASML and IMEC were able to pattern 24 nm pitch lines using 3 nm process and the current EUV lithography system by adjusting an incident angle of EUV light source [88]. However, the high-NA will reduce the depth of focus, which leads to improve the focus control possibility.

**Figure 16.** An image of 24 nm pitch lines which are successfully implemented through extreme ultraviolet (EUV) single-patterning process [88].

## 5. Epitaxy of Nano-Scaled Transistors

# 5.1. SiGe Selective Epitaxy Growth (SEG) for Source and Drain (S/D)

In the 90 nm technology node, selective epitaxy growth (SEG) of SiGe was integrated in the recessed S/D areas as stressor material to induce uniaxial compressive strain to enhance the carrier

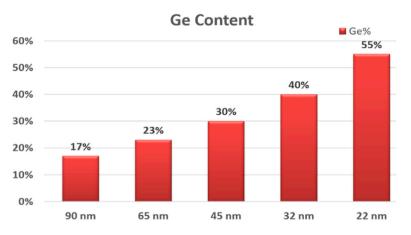

mobility in the channel region [89]. The Ge content in the SiGe in S/D areas has been increased from 19% to 45% while the critical dimension (CD) of the transistors were scaled down from 90-nm (2D: planar transistors) to 22-nm (3D: FinFET) nodes [89–91]. It has been reported that the Ge content in the SiGe S/D will be further increased to more than 50% in the 10 nm Fin structure [92]. A summary of the Ge contents in S/D areas for different technology nodes is shown in Figure 17.

Figure 17. Ge contents in source and drain (S/D) regions in different technology nodes [92].

In order to induce more strain in the channel area, the original round shape of recess (or trenches) in S/D regions was changed to sigma (" $\Sigma$ ") shape in the 45-nm node. It is because that the SiGe layers could be placed closer to the channel area [93,94].

The SEG process of SiGe on Si Fins and Si nanowires suffers from different challenges and problems: Defects due to strain relaxation [95], facet formation [96,97], non-uniform strain distribution [98,99], and the pattern dependency effects [100–103].

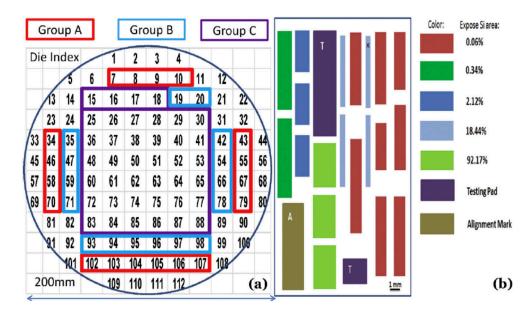

Figure 18a,b shows three groups of chips (A, B, and C) in terms of transistor performances (poor, good, and excellent for A, B, and C group, respectively) over the wafer. The X-ray results show the Ge content, layer thickness, and strain relaxation for transistors in these groups, which could be a result of the pattern dependency of selective growth [94].

**Figure 18.** (a) The image of the processed chips on an 200 mm wafer where three groups were distinguished according to the transistor performance and (b) illustrates the pattern of one 112 manufactured chips where the different exposed Si areas are shown in different colors [94].

The reason for the pattern dependency over a wafer (global effect) or inside a chip (local effect) is rooted from non-uniform consumption of reactant gases when the layout is changed. In a more specific way, pattern dependency of SEG occurs when the exposed Si area or opening size of the S/D regions are altered in a chip or when the neighboring chips have different layouts. A remedy to this problem is modeling the growth for a specific layout to find out the layer profile in advance and then change the chip layer out to create a uniform gas consumption over the chip [100–103].

The quality of the epitaxial layer and the strain induced by SiGe S/D to the channel is very sensitive to the quality of initial Si surface. This means that surface cleaning and treatment of Si-fins prior to the epitaxy are very important issues that determine the defect density of the SiGe layers. A standard cleaning method using chemicals—sulfuric acid and hydrogen peroxide mix (SPM) followed by Ammonium hydroxide and hydrogen peroxide mix (APM) with diluted hydrofluoric acid (DHF)—are widely used in semiconductor labs. Then, the in-situ treatment is another key step to remove any native oxide or residual impurities on the Si fin surface. To choose an appropriate temperature that does not damage the Si fins' shape is an important point.

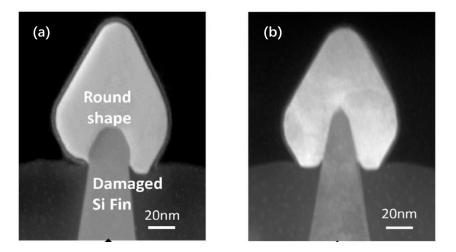

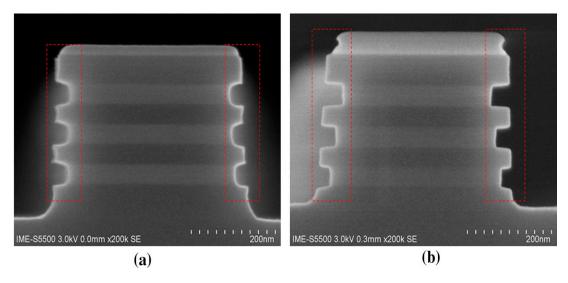

As an example, Figure 19a,b shows how the symmetric shape of Si fin can be damaged after pre-baking at 825 °C (Figure 19a) and 800 °C (Figure 19b). It shows that serious damage occurred to Si fins and as a result, the height of the fin is shrunk. However, the samples with pre-baking at 800 °C in Figure 19b demonstrate high quality Si fin surface after SiGe epitaxy. The symmetrical morphology of SiGe shows more strain induced [104].

**Figure 19.** HRTEM cross-section micrographs of the Si-fins with different prebaking temperatures as follows: (**a**) at 825 °C and (**b**) 800 °C [104].

#### 5.2. SiGe, Ge Epitaxy Growth for Channel Region

Strain engineering in nano-scale transistors and devices is an effective method to deal with SCEs, involving high-mobility materials e.g., strained Si [105], SiGe [105,106], Ge [107], and GeSn [108] in the channel areas. The integration of high-mobility materials mainly has two trends:

- (1) To grow the high-mobility materials as the channel first. In order to avoid strain relaxation in the channel, low thermal budget is demanded in device fabrication.

- (2) To have Si channel for example in FinFET but later replace it with high-mobility materials (SiGe, Ge, and GeSn) with a high aspect ratio (AR). These channel materials can be deposited selectively in the transistor structures. In this way, the defects are formed and trap close to the fins' sidewall (oxide) during epitaxial growth process. Finally, high-quality material is filled in the vertical direction inside the trench.

For the removing of Si Fin in the trenches, wet etch using diluted Tetramethylammonium hydroxide (TMAH) and the vapor etch using HCl inside the chemical vapor deposition (CVD) chamber

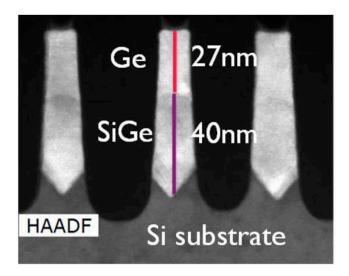

are applied [109]. After filling the empty trenches, chemical mechanical polish (CMP) technique is performed to polish and planarize any existing overgrown film. Figure 20 shows the image of SiGe or Ge SEG in the channel area in a FinFET structure. The process starts to form a "V-shaped" Si recess surface and to grow the Si<sub>0.3</sub>Ge<sub>0.7</sub> as strain relaxed buffer (SRB) layer [110].

**Figure 20.** Cross-section TEM image of strained Ge-cap/ SRB Si<sub>0.3</sub>Ge<sub>0.7</sub>SEG grown inside oxide trenches of FinFET [110].

# 5.3. SiGe/Si Mutil-Layers Epitaxy Growth for Gate-All-Around (GAA) Structure

For better control over a SCEs, a more aggressive design e.g., GAAFETs is proposed to be integrated beyond 5 nm node. For such transistors, SiGe or Ge is proposed to be grown as muti-layers and later selectively etched to form the channel region.

As shown in Figure 21, it is a vertical GAA structure that uses silicon nanowire as a channel to increase the channel width of the device and reduce leakage current [111], and effectively suppress SCEs.

Figure 21. A vertical gate-all-around nanowire structure [111].

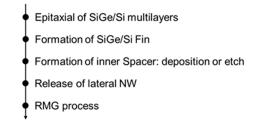

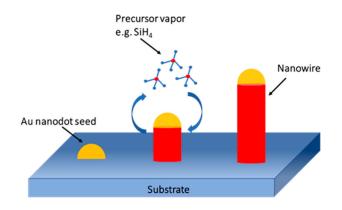

In GAAFET, the width of the channel is increased by using multiple Si nanowires. A fabrication process of hGAAFETs is shown in Figure 22. At first, a multilayer of SiGe/Si is grown on the substrate. After the multilayer growth, the fins are patterned by using spacer technology. Later, dummy gates and internal spacers, such as silicon-nitride, are defined. At this stage, selective etching of SiGe is performed with respect to the Si layer, and then a nitride layer is deposited and etched to define internal spacers. Finally, HfO<sub>2</sub>/TiN/W deposition can be used as metal gate for lateral GAA NWs [112].

However, the preparation process of nanowires faces some challenges, e.g., the control of nanowire sizes [113], and its ideal circular shape in cross section [114]. When hGAAFETs are processed, SiGe is used as a sacrificial layer and it has to be completely removed while retaining Si. With regard to vGAAFETs, precisely controlled etching of SiGe is critical for the device feature size.

SiGe/Si nanowires can be divided into vertical and horizontal nanowires. The vertical nanowire GAA requires more disruptive technological changes, while the horizontal one has less deviation from FinFET process, and the manufacturing is less difficult [112,115].

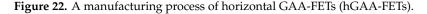

There are two methods to form NWs: Top-down and bottom-up ones. VLS is the most common growth method for bottom-up nanowire. The principle of this method has been described in Figure 23. The VLS metod applies a catalyst metal (typically Au), and chemical vapor deposition (CVD) technique is usually utilized for the NW growth [116]. The diameter of the NWs is determined by the size of the catalyst (catalytic seed) and related to the growth direction, and the length is determined by the flow rate and the time of the precursor vapor [117].

Figure 23. Schematic of VLS growing nanowires [117].

The top-down preparation of SiGe nanowires mainly relies on SiGe's selective isotropic etching process. The shape of the nanowire is determined by photolithography and etching. The top-down approach has many advantages for horizontal nanowire formation e.g., yield and availability of mature technology [112]. Wet etching is used to prepare SiGe\Si nanowires. The chemical liquid composition used to selectively etch SiGe is HNO<sub>3</sub>: BOE: H<sub>2</sub>O or H<sub>2</sub>O<sub>2</sub>: BOE: H<sub>2</sub>O. HNO<sub>3</sub> and H<sub>2</sub>O<sub>2</sub> react with Ge preferentially as strong oxidants, and the oxide layer reacts with BOE to remove SiGe. It is worth mentioning that the high concentration of HF is corrosive to Si and SiO<sub>2</sub>. Dry plasma etching can be used to prepare SiGe/Si nanowires as well. CF<sub>4</sub>/O<sub>2</sub>/He reaction system is used as the etching gas for SiGe. The high-energy particles of traditional plasma will cause damage to the lattice. The use of additional RF power can reduce ion-induced damage [116]. Compared with the traditional continuous etching, atomic layer etching (ALE) can achieve precise control of the etching size. The oxidant and the etching agent alternately cycle when ALE technique is used [113]. ALE can achieve atomic-scale reactions, and is a very promising method for etching small-scale patterns. ALE can be used in both wet etch and dry etch [113,118]. Figure 24 shows the etching of (SiGe/Si) multilayer fins.

**Figure 24.** TEM images of post-etching of Si/SiGe multilayer fins in two directions (longitudinal and transverse cross-section). Two fin-patterning options have been designed: (a) Isolated and (b) dense FETs, which were carried out by sidewall pattern transfer technology [112].

# 6. Implantation and Advanced Doping Methods

Ion implantation has played an important role as a doping method in the fabrication of semiconductor devices for many years. Especially in the manufacture of CMOS devices, implantation offers a precise way to introduce expected species (B/P/As, etc.) into the wafers compared to traditional thermal diffusion. The quantity of both dopants and its distribution could be well controlled by this method. However, when the critical dimensions of MOSFETs evolved into nanoscale, 3D structures e.g., FinFETs or nano-wires, implanataion becomes more complicated. It happens when the architecture brings more requirements for the doping process to achieve highly activated, low damaged, and diffusion-controlled junctions.

#### 6.1. Conformal Doping on 3D Structure Devices

One of the greatest challenges on 3D devices manufacturing is how to make a high aspect ratio doping within 3D structure. A large tilt is applied for implantation on FinFET initially, but later with the continuous requirement for increasing the packing density, the incident angles is restricted by the tight fin pitch due to the shadowing effect during implantation [119].

A novel doping technology called Plasma doping has been considered as an effective solution to achieve conformal doping distribution on 3D structures [119–123]. The technique is designed differently with traditional ion implanter where no species separate components in this system. The dopant gas is ionized in the chamber and the ions containing the dopant species are then extracted from the created plasma and can be accelerated to the substrate at varied angles. In this way, a more uniform doping profile could be obtained as demonstrated by K.Han et al. [124]. The amorphous layer created by plasma doping on a fin structure was more uniform than that done by beamline implant system.

Another alternative method for nano-scale doping is solid (or liquid) phased diffusion (SPD) technology. Dopant containing compounds are coated on the surface uniformly and then driven into the substrate via rapid thermal diffusion instead of implantation [125,126]. SPD could be carried out in several ways. For three-dimension structures, mono-layer-doping (MLD) is believed to be one of the most promising candidates [127–129]. The process starts from a self-assembled monolayer formation which is mainly composed of organic dopant. After the dopants are attached uniformly to the surface and catalyzed by a low temperature, the hydrosilylation reaction will be enabled to form covalent bonds between the molecules and silicon atoms of the substrates. After that, a rapid thermal treatment will break the molecules and drive the dopant atoms into the substrates. Until then, a capping layer is always needed to prevent the dopant from diffusing out into the atmosphere outside. The whole procedure is defect free, and the dose could be tuned by modulating the content of dopant

impurities in the molecules. Moreover, the dose is affected by other factors due to the self-limiting surface reacting properties.

#### 6.2. Defect Reduction

At present, implantation is still the leading candidate for doping, however it is well known that implantation for S/D regions and S/D extension will always bring damage to the substrate. This is especially observed when the energy or fluxion is high enough, a large number of defects will be created due to the cascade collisions between injecting ions and atoms of the target. In principle, the damage and most of these defects could be recovered later by a high temperature treatment like spike or millisecond annealing. However, there are always some deactivated clusters composed of interstitial or dopant atoms residue remained at the end of range area, which might degrade the resistance and lead to junction leakage.

Substrate temperature has to be chosen in order to effectively affect the damage generation [130,131]. It is known that implanted amorphous layer is essential for S/D engineering in CMOS to achieve highly activated shallow junction, but the disadvantage is the lattice damage and the created point defects. Fareen et al. has explained the physical mechanism of cryo-implantation. When the substrate temperature is decreased to -100 °C, implantation will be favorable to improve the amorphization by forming continuous thicker amorphous layer. In this way, the amount of Si interstitials is reduced and the formation of interstitial-boron (I-B) clusters is inhibited, which is the main mechanism of dopant deactivation and junction leakage [132,133].

Despite the fact that amorphization is greatly helpful in improving activation, it is not always expected in 3D devices. For 3D devices e.g., FinFET or NWs, the channel or extension implanatation should be in nanoscale and easily amorphized. Especially for the extension area, it is easily fully amorphized, which might cause permanent fin damage even after thermal annealing. This will result in poor parasitic resistance and higher junction leakage. To avoid this problem, Wood et al. tried to prevent amorphization generation by raising the substrate temperature in n-type S/D extension implantation. It has proved that hot implantation is effective to suppress the amorphization of the fin structure, and the junction could be improved by > 10 X, which means the damage is decreased greatly in this way [134].

#### 6.3. Material Modification

Apart from doping process, material modification is another potential application of implantation in advanced devices. As reported, Ge, Si, or C are employed to inhibit the channeling or transient enhanced diffusion (TED) effect in ultra shallow junction (USJ) module [135,136]. Moreover, Ge or As is also proved to be favorable to decrease the contact resistance [137–139]. Since the structure of CMOS has evolved into three dimensions, titanium silicide has re-acted as standard contact schemes due to its better thermal stability and lower contact resistivity.

Recently, pre-amorphous implantation (PAI) is reported to be effective to improve the performance of Ti silicide. Mao et al. [140] and Yu et al. [141] have demonstrated that when a low-energy pre-amorphous Ge implantation is applied on contact area, it will lead to great conductivity improvement, and an extremely low  $\rho$  of about  $1.5 \times 10^{-9}$   $\Omega$ cm could be achieved. The mechanism could be explained by the interfacial morphology promotion induced by PAI. The PAI process is helpful to enhance both the diffusion of Si atoms and bonding of Ti-Si [142].

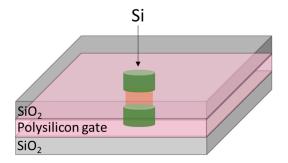

#### 7. ALD, HKMG and NC Materials

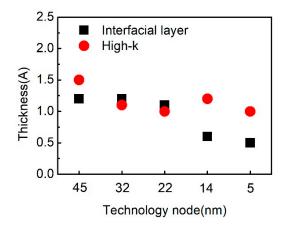

High-k and metal gate have been introduced into CMOS technology to replace the traditional  $SiO_2$ /poly-silicon gate electrode since 45 nm technology node. Along with the shrinking of the feature size, the type and thickness selection of the high-k and metal gate material are modified correspondingly.  $SiO_2$  and  $HfO_2$  are chose to be interfacial layer and high k dielectric from 45nm to 5nm technology node. Figure 25 shows the related thicknesses of these oxide layers. It can be seen that the interfacial

layer decreases slightly from 1.2 nm to 1.1 nm when the technology node decreases from 45 nm to 22 nm, while the thickness of  $HfO_2$  reduces from 1.5 nm to 1.0 nm. Tri/Fin-FET structure is introduced instead of the planar structure. The thickness of  $SiO_2$  continuously decreases to 0.6nm while  $HfO_2$  thickness increases to 1.2 nm.  $SiO_2$  is the best passivation of Si surface, which can be used to make a device with high reliability. However, 0.6 nm is rather thin, which is only several layers of atoms and cannot be further decreased dramatically. So,  $SiO_2$  is estimated to be about 0.5nm and  $HfO_2$  is about 1.0 nm at 5 nm node.

Figure 25. Interfacial layer and high-k dielectric thickness from 45 nm to 5 nm node.

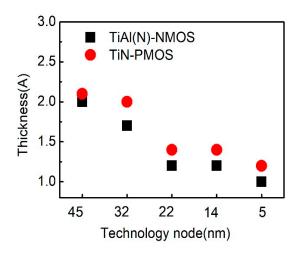

For metal gate, the thickness of NMOS and PMOS work function metals range from the technology node is shown in Figure 26. TiAl(N) is used as NMOS work function metal and TiN as PMOS work function metal in both 45nm node and 32nm node device [143,144]. The thickness of TiAl(N) and TiN are ~2.0 nm and ~2.1 nm, respectively, in 45nm node, while they are ~1.7 nm and 2 nm in 32 nm node. The introduction of Tri-gate FinFET structure and gate-all-around (nanowire) structure improves the electrostatic gate control and the requirement of metal gate work function decreases. Thus, due to the miniturization of device and limited filling space, the metal gate thickness still needs to be decreased. The thickness of TiAl(N) and TiN are ~1.2 nm and ~1.4 nm, respectively, in both 22 nm node and 14 nm node. They are estimated to be about 1.0nm and 1.2nm for TiAl(N) and TiN, respectively, at 5 nm node.

Figure 26. Work function metal thicknesses from 45 nm to 5 nm node.

The traditional way to deposit metal gate is physical vapor deposition (PVD), which can easily deposit a variety of metal gate materials and give much more metal gate selections. For the CMOS device of 45nm node and 32nm node, the aspect ratio of the gate stack is not so large that PVD can satisfy the requirements. However, when it comes to FinFET or nanowire structure, the aspect ratio

is rather high, which can be more than 2:1 when the CD size is less than 20nm. Therefore, PVD cannot satisfactorily perform the filling of metal gate structure anymore. Atomic layer deposition (ALD) is the best solution, which has capability of excellent conformal step coverage [145]. HfO<sub>2</sub> and P type metal can be easily deposited by ALD, but it is relatively difficult for N type workfunction metal deposition due to the limitation of precursor. Table 1 shows the typical related study results of different workfunction metals. Thermal ALD of TiN using TiCl<sub>4</sub> and NH<sub>3</sub> as precursors at 350 °C was demonstrated by Lujan et al. [146]. The effective workfunction was extracted to be 5.3eV, which is suitable for PMOS application. Jeon et al. fabricated stacked metal Ti<sub>1-x</sub>Al<sub>x</sub>N using TDMAT, TMA, and  $NH_3/H_2$  plasma [147]. The effective work function was 5.04 eV. The same group could also grow TiC-TiN layers by using TDMAT and NH<sub>3</sub>/H<sub>2</sub> plasma. The effective workfunction was decreased from 5.0 eV to 4.6 eV by increasing the growth temperature [148]. G. Cho et al. could grow TiC<sub>x</sub>N<sub>y</sub> film using TDMAT and H<sub>2</sub>, NH<sub>3</sub>, and CH<sub>4</sub>/H<sub>2</sub> plasma separately. It was found that the Ti-C and Ti-N bound have an important effect on the effective workfunction value. The lowest effective workfunction was estimated to 4.66 eV [149]. Most of the ALD N type metal is deposited by plasma enhanced (PE) ALD. PEALD of TaC<sub>v</sub> using organic precursor and a carbon containing gas has an effective workfunction value of 4.77–4.54 eV [150]. Most of the other N type metals, TiC, TaCN, and WC<sub>0.4</sub>, etc., are also deposited by PEALD [151–153]. Compared with PEALD, thermal ALD has no plasma damage on the underlayer dielectric and could improve the device performance.

**Table 1.** The effective workfunction of different metals grown by atomic layer deposition (ALD) for N type Metal-Oxide-Semiconductor Field-Effect Transistor (NMOSFET).

| Metal                               | Dep. Method | Effective Workfunction   | Ref   |

|-------------------------------------|-------------|--------------------------|-------|

| TiN                                 | thermal ALD | 5.3 eV                   | [146] |

| Ti <sub>1-x</sub> Al <sub>x</sub> N | PEALD       | 5.04 eV                  | [147] |

| TiC-TiN                             | PEALD       | 5.0-4.6 eV               | [148] |

| TiC <sub>x</sub> N <sub>y</sub>     | PEALD       | 4.66 eV                  | [149] |

| TaCy                                | PEALD       | 4.77–4.54 eV             | [150] |

| TiĆ                                 | PEALD       | 5.24–4.45 eV             | [151] |

| TaCN                                | PEALD       | 4.37 eV                  | [152] |

| WC <sub>0.4</sub>                   | PEALD       | $4.2 \pm 0.1 \text{ eV}$ | [153] |

| TiAlC                               | thermal ALD | 4.79–4.49 eV             | [154] |

| TiAlC                               | thermal ALD | 4.4 –4.24 eV             | [155] |

| TaAlC                               | thermal ALD | 4.74–4.49 eV             | [156] |

| TaAlC                               | thermal ALD | 4.65–4.26 eV             | [157] |

| ErC <sub>2</sub>                    | ALD         | 3.9 eV                   | [158] |

Chao et al. systematically studied thermal ALD TiAlC and TaAlC. The effective workfunction could be tuned and the lowest effective workfunction of 4.24 eV was obtained, which is suitable for NMOS application [154–157].

Currently, a major challenge for integrated circuits is the control of low power consumption. With the shrinking of the feature size of traditional transistor devices, the power consumption increases sharply. Low-power devices are the current research hotspots of integrated circuits. The sub-threshold swing of negative capacitance transistors is less than 60 mV/dec, which breaks through the sub-threshold swing limit of traditional transistor devices [159]. Therefore, V<sub>dd</sub> and I<sub>off</sub> can be effectively reduced and applied to low-power electronic devices. In the current reported data, the minimum value of the sub-threshold swing has reached 42 mV/dec [160] and negative capacitance transistors show excellent application prospects. The discovery of ferroelectricity of doped HfO<sub>2</sub> materials provides tremendous potential for the negative capacitance transistors [161], due to the excellent compatibility with the nowadays COMS technology. However, the fatigue characteristics are still poor. In the near future, the research on negative capacitance transistors will continue to heat up. Finding suitable ferroelectric materials and realizing greater negative capacitance values are the focus and challenge of technological research and development.

#### 8. ALD W for Nano-Transistors

Since Intel introduced high-k and metal gates (HKMG) to MOSFET, ALD technology has been applied to grow different related materials for nanoscale transistors. As an excellent electrode filler material, tungsten was first used in integrated circuits for contact hole filler tungsten bolt (W plug) in metal interconnects. After the appearance of HKMG, tungsten was also used as filler electrode material for metal grids. Recent studies about memory structures have shown that  $\beta$ - phase W can produce giant magnetoresistance (GMR) effects due to their large spin hall angles. This discovery has a high application prospect in third-generation magnetic memory [162]. Here, a brief of the current status and progress of ALD W films and their applications in semiconductor devices has been provided.

When depositing a mono-metallic in the atomic layer, the purpose of using a deoxidizer is to replace and remove the coordination group connected to the metal atom. The ALD W reaction belongs to the replacement reaction of fluoride (WF<sub>6</sub>) and deoxidizer (such as silane, ethylamine, etc.). At present, WF<sub>6</sub> is commonly used as the precursor of W, and the  $B_2H_6$  and SiH<sub>4</sub> are used as replacement reductant precursors.

ALD growth process is very sensitive to the chemical properties of the surface. As a surface self-limiting chemisorption reaction, the higher the active sites on the surface exit, the greater the chemisorption probability is, and the better the surface nucleation. Hwanyeol Park et al. [163] simulated the process of ALD W deposited on TiN surface using  $B_2H_6$  and  $WF_6$  as precursors by first-principles density functional theory (DFT). The precursor adsorption processes of ALD W on different TiN surfaces were investigated in detail. Three orientations and three positions of the  $B_2H_6$  on three different Ti surfaces are considered, which are the TiN(111) of the Ti ending, TiN(001), and the TiN(111) of the N ending. The results show that the overall reaction energy between  $B_2H_6$  and  $WF_6$  is lowest at N-terminated TiN (111). The study found that controlling the texture of TiN films is essential to improve subsequent W nucleation.

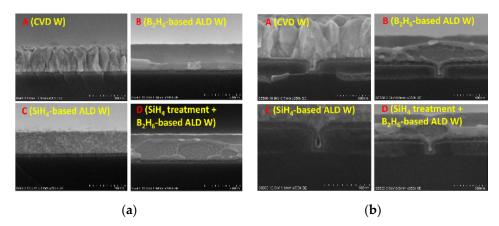

#### 8.1. ALD W as Gate Filling Metal

ALDW can be used as gate filling metal for 22 nm and beyond nodes for CMOS technology [164,165]. Wang et al. has shown that the amorphous ALD W using  $B_2H_6$  and  $WF_6$  shows lower growth rate, lower resistivity, and better gap-filling capability in gate trenches with high aspect ratio, in contrast to the polycrystalline ALD W using SiH<sub>4</sub> and WF<sub>6</sub> as displayed in Figure 27. Furthermore, it has been shown that the doping of boron (B) in ALD W does not affect the C–V and I–V characteristics of as-prepared capacitors. This indicates that the ALD W using  $B_2H_6$  and  $WF_6$  is a good metal for gate filling, which can be widely used in nanoscale transistors [166]. It was found that, among filling metals, transistors filled by ALD W using SiH<sub>4</sub> show higher drive capability and better control of SCEs.

**Figure 27.** Cross-sectional SEM pictures of W films grown in different conditions: (**a**) On blank wafers and (**b**) trenches filling capacity [166].

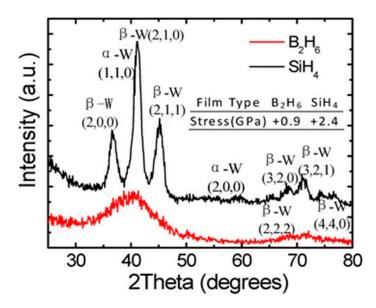

Further investigations were performed by XRD to study the internal morphology of ALD W films. The results show that crystalline phases were detected in the ALD W films grown by SiH<sub>4</sub> as precursor; meanwhile, the films deposited with  $B_2H_6$  were amorphous as shown in Figure 28 [166].

Figure 28. XRD patterns of ALD W grown by SiH<sub>4</sub> and  $B_2H_6$  precursors and the estimated stress [166].

# 8.2. Area-Selective ALD W

Area-selective ALD W is a bottom-up process and it solves the edge placement errors problems encountered in the process of top-down etching and other processes. By using the substrate-dependent nucleation of ALD processes, we can use the hydrogen to expand the substrate selectivity window during W atomic layer deposition [167]. Tungsten ALD is more energetically favorable on Si than on SiO<sub>2</sub>, but after several ALD cycles, the selectivity will be lost. Kalanyan et al. found that, during the WF<sub>6</sub> dose step, adding H<sub>2</sub> can help passivate SiO<sub>2</sub> against W nucleation without affecting W growth on silicon. Surface characterization confirms that H<sub>2</sub> can promote fluorine passivation of SiO<sub>2</sub> through surface reactions with HF.

# 9. SiN<sub>x</sub> Film and Strain Engineering

$SiN_x$  is a kind of material that is widely used in CMOS-lines as gate dielectric, spacer, hardmask, and passivation layer. When time goes into the post-Moore age, with increase of transistors integration in a chip, more information will be transferred between chips optically, which enhances the demands of the interconnections. Different from electric current in metal wiring and electron transport, signal transmission in optical interconnection fundamentally comes from photons. It means that electron transmission by means of copper connection will not be the main action in the chip, but the signal is substituted with photons transmit within optical fiber or waveguide with low power consumption [168]. As the third-generation waveguide platform,  $SiN_x$  film shows much more superior performances than previous waveguide platforms including fibers and silicon waveguides.  $SiN_x$  film and its strain engineering play an important role in monolithic integration photonics and eletronics.

# 9.1. Different Properties of $SiN_x$ Film

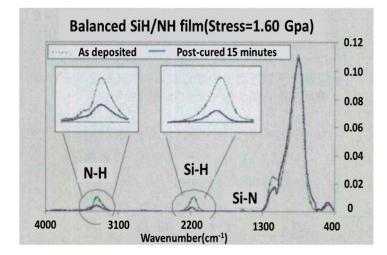

The properties of  $SiN_x$  film mainly depend on its chemical composition. Si/N ratio and chemical bonding variation will lead to the changes of mechanical and optical characteristics such as refractive index, stress, optical band gap, and Young's modulus. In CMOS lines, low pressure chemical vapor deposition (LPCVD), plasma-enhanced chemical vapor deposition (PECVD), and ALD technologies are the normal processes. LPCVD technology could produce silicon nitride that is either highly strained

and stoichiometric (refractive index is ~2.0@633 nm) or low stress and silicon rich (higher refractive index). PECVD-based silicon nitride has a composition that strongly depends on the deposition conditions, and can be silicon-rich, stoichiometric, and nitrogen-rich (lower refractive index). The best step coverage is the advantage of ALD-based silicon nitride. Classifying the  $SiN_x$  film by stress, it can be identified as tensile, compressive, and non-stress films. With these different properties, it can be applied in many technical areas.

# 9.1.1. High Tensile Stress Contact Etch Stop Layer (CESL)

In fabrication, tensile stress  $SiN_x$  film is usually manufactured by LPCVD or PECVD process. It is well known that LPCVD technique is usually used to create high-tensile-stress  $Si_3N_4$  films up to 2Gpa. When we did not need to care about its high thermal budget, this deposition technique could be really a good choice. However, sometimes when the process flow reaches the backend of the line, high temperature would be incompatible, and the devices are practically destroyed [169]. PECVD technology is a highly efficient, mature, and low thermal budget process, which is the best choice in the backend of the line [170]. However, meanwhile, its low thermal budget brings the issue that the hydrogen in the silicon nitride film could not have been pushed out. This reduces the film tensile stress down to about 1Gpa [171]. In order to improve the tensile stress, plasma treatment and ultraviolet thermal process (UVTP) have been applied as shown in Figure 29. It is important to mention here that the UVTP treatment after films deposition could increase tensile stress in the films to 1.7 Gpa. During this method, Si-H, N-H bonding were broken to push out H gas through UV and thermal process. This ability made PECVD technology a good choice to meet the demands of both high tensile stress and low thermal budget.

**Figure 29.** A spectrum shows the improvement of tensile stress using ultraviolet thermal process (UVTP) method [172].

## 9.1.2. High Compressive Stress CESL

High compressive stress  $SiN_x$  film is also very important during the post-Moore age. Achieving high strain is hard for LPCVD technology while it is easier for PECVD technology. In order to produce high compressive stress film, there were high and low RF power sources coupled with diluted gas by PECVD. It has been found that the compressive stress has a high relationship with diluted gas species. The compressive value is about -1.2 Gpa when nitrogen was used as diluted gas [173]. The compressive value would be increased to about -2.3 Gpa when a mixture of argon and nitrogen was used as diluted gas. Furthermore, the compressive value could be increased to about -3.1Gpa with the changing of diluted gas to hydrogen and argon mixture. Here, the hydrogen is utilized to reduce energy loss during plasma bombardment. If further compressive value is desired, the elasticity

modulus of the film must be improved by inducing carbon element. It is found that the compressive value could attain to -3.5Gpa when SiH<sub>4</sub> is replaced with Trimethylsilane (TMS). The mechanism was that TMS contained carbon element, which impelled hydrogen to implement higher compressive value [174].

# 9.2. The Application of $SiN_x$ Film in Post-Moore Age

# 9.2.1. As Waveguide Transmitting Light in Photonics

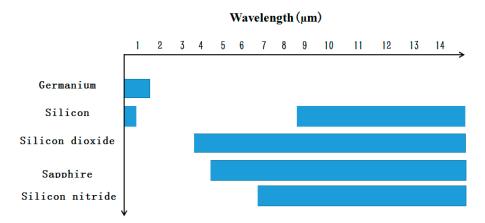

Photonic integrated circuits have been based on several kinds of material platforms [175–177], and each platform has its own advantages and challenges. Today, mainstream silicon photonics products are built on silicon-on-insulator (SOI) wafers through traditional CMOS pilot line. Silicon nitride ( $Si_3N_4$ ) photonics, a third integration platform, has characteristics and performance superior to the silicon-on-insulator (SOI) photonics and group III-V photonics platforms and is compatible with foundry-scale processes.

Figure 30 shows the light transparent windows of the different waveguide core materials. Compared with silicon and III-V platforms, silicon nitride core has a broad transparency range (0.4–2.35  $\mu$ m), which takes it into the bio-science field where silicon core cannot. In addition to broad transmission wavelength, lower index contrast with silica compared to silicon, no suffering from two-photon absorption (TPA), and free carrier absorption are all silicon nitride's superiority.

**Figure 30.** Light transparent window of the core materials for different waveguide and the white areas represent optical transparency meanwhile the blue areas signify high energy loss [178].

## 9.2.2. Strain Engineering in Modify Germanium Band Gap

It is well known that germanium is pseudo-direct bandgap material. A transition from indirect to direct band gap has been predicted for tensile-strained germanium since the energy position of the conduction  $\Gamma$  valley versus strain decreases more rapidly than the band-edge L valley [179,180]. Many methods for increasing the tensile stress in Ge have been explored, including strained Ge growth, thermally induced strains, external stresses, stressor layers, and strain redistribution. As a stressor layer, SiN<sub>x</sub> film is a very attractive possibility to change germanium band structure because of its compatibility with a CMOS processing and the flexibility to control the stress transfer and achieve high tensile or compressive strain [181–184]. In 2013, Centre national de la recherche scientifique (CNRS) demonstrated that when a strong tensile strain silicon nitride stressor covered germanium microdisks growing on GaAs substrate, up to 1% biaxial strain resulted in direct band gap emission red-shifting from 1550 nm up to 2000 nm under the room temperature [183]. In 2015, their publication said that when all-around tensile stress of silicon nitride was brought up to 1.45%, it would result in red-shift toward 2100 nm wavelength.

$SiN_x$  film is also a kind of flexible material whose properties and characteristics are altered as process conditions changed. The unique ability makes it widely used in the post-Moore era especially in the field of silicon-based photonic integrated circuit.

# 9.2.3. The Application of SiN<sub>x</sub> Stress Engineering in IV MOSFET

There are various advanced stress technologies to enhance the carrier mobility in the channel including shallow trench isolation (STI), nitride CESL, embedded SiGe, or SiC in source/drain [185]. Among all these feasible stress inducing approaches, the intrinsic stress of thin  $SiN_x$  film by a CESL has become an important technique that receives much attention because it is easy to execute in nanoscale semiconductor devices.

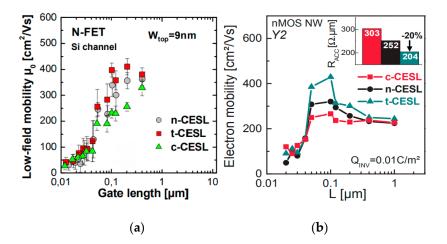

The effect of CESL in IV MOSFETs with Si and Ge and GeSi channel material have been reported in many publications. Recently, more and more articles pay attention on nanoscale Ge or GeSi MOSFET. Both the experimental and simulation work presented the stress-induced mobility gain of CESL as strongly dependent on the layout arrangement of devices, particularly in situations with narrow widths [186]. P. Nguyen et al. has demonstrated induced CESL in  $\Omega$ -gate CMOS nanowires with p-FETs and n-FETs down to W = 15~20nm gate length [187,188]. As shown in Figure 31a,b, tensile CESL is the best option to improve n-FET performance. c-CESL, n-CESL, and t-CESL represent compressive-CESL, neutral-CESL, and tensile-CESL, respectively.

**Figure 31.** NMOSFET electron mobility vs. contact etch stop layer (CESL) technology, (**a**) in 9 nm n-FET NW. A better mobility is observed under tensile CESL [187] and (**b**) Electron mobility vs. L for different CESL in nanowires. Inset: extracted access resistance [188].

## 10. Advanced Etching for Nano-Transistor Structures

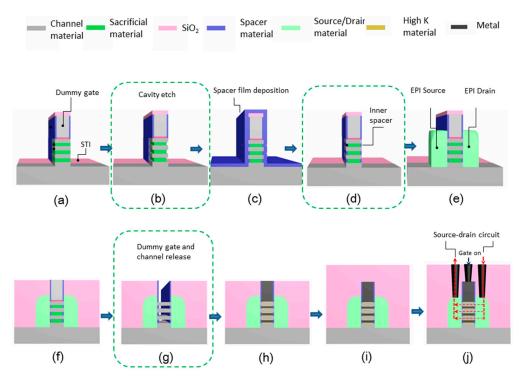

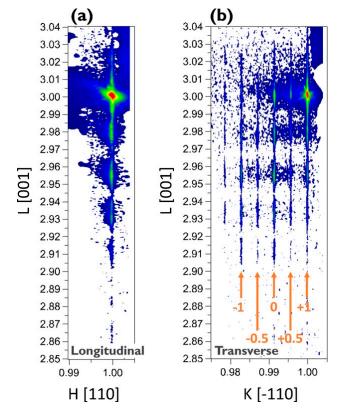

As CMOS technology enters the 3 nm node, GAA nanosheet/nanowire becomes the most powerful competitor to replace FinFET technology because of its excellent control of SCEs [189,190]. As it was mentioned above, GAA devices mainly have two forms, horizontal [191,192] and vertical [46,193,194], and selective etching plays a very important role in these manufacturing processes. For the preparation of horizontal nanowires shown in Figure 32, there are three main steps that require precise selective etching to prepare inner spacers and release dummy gates and nanowire channels. For vertical nanowire devices (see Figure 33), selective etching is used to precisely control the diameters of the channels.

**Figure 32.** Process flow and critical etching steps for manufacturing lateral nanowire GAA device: (a) Source/drain Fin recess for opening active area, (b) cavity etching for defining the growth position and size of the inner spacer, (c) inner spacer film deposition, (d) controlled etching of spacer film and formation of inner spacer, (e) source/drain epitaxial growth, (f) dielectric deposition and planarization, (g) dummy gate removal and nanowires formation, (h) filling and planarization of high-K metal gates, (i) interlayer dielectric deposition, and (j) metal contact plug and current direction when device is on on-state [195].

Channel formation by SiGe isotropic selective etching

**Figure 33.** Schematic of vertical nanowire GAA transistor: (**a**) Structural design for a single device, and (**b**) test structure with two devices connected in parallel via a local interconnect bridge [46].

# 10.1. High Selective Etching for Channel Full Release

Removal of the sacrificial layer to obtain nanowires or nanosheets is a very critical process step (as shown in Figure 32g). This step requires a high etch selectivity when the nanowire channel is

released. This is achieved through the selective etching of sacrificial layer to the channel material. The channel material is generally Si, with SiGe sacrificial layer. Conversely, the channel material may be Ge or SiGe, and the sacrificial material is SiGe or Si. Therefore, SiGe selective etching is required to obtain silicon channels, or silicon selective etching is required to obtain SiGe channels.

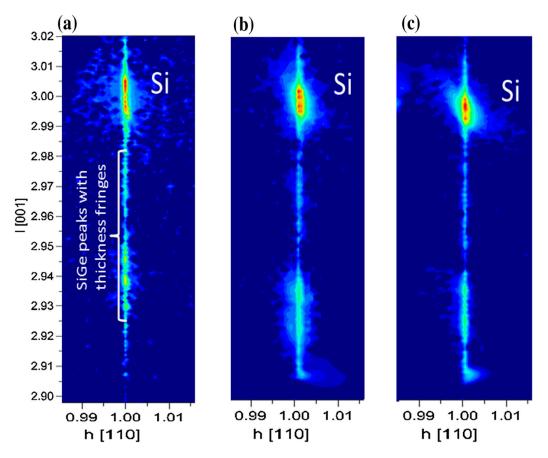

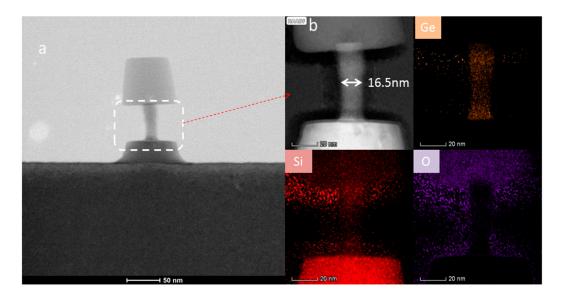

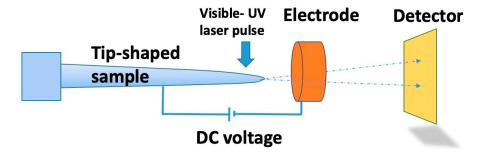

For SiGe selectivity etching, alkali and acid containing oxidant are commonly used chemical reagents, such as H<sub>2</sub>O<sub>2</sub>/NH<sub>4</sub>OH [196] and H<sub>2</sub>O<sub>2</sub>/HF/CH<sub>3</sub>COOH [197,198]. The outcome of this etching method easily leads to structural collapse due to the solution capillary effect, especially for structures with high aspect ratio and small size. One way to overcome the above limitation of the liquid reaction is to change the process to selective etching of SiGe by vapor phase HCl [199]. The gaseous HCl method may offer a high selectivity to Si in a suitable high temperature range, and there is no collapse problem after etching a small size structure with a high aspect ratio. One drawback with this method is that high reaction temperature will cause potential risks of dopant diffusion and stress relaxation [200,201]. Remote plasma selective etching of SiGe is a technique with higher precision than the above pure chemical etching, and it is a process under room temperature without additional thermal effects on the material. The etching gases are mainly CF<sub>4</sub> [202], CF<sub>4</sub>/O<sub>2</sub>/N<sub>2</sub>/CH<sub>2</sub>F<sub>2</sub> [203,204], and NF<sub>3</sub>/Ar/NO [205]. Conventional plasma etching is usually used for anisotropic etching [206]. However, using  $CF_4/O_2/He$ in traditional inductively coupled plasma (ICP) for SiGe selective etching has achieved a good etching effect. The etching morphology has advantages over wet etching as shown in Figure 34 and damaged material can be removed and the SiGe layer is preserved as shown in high-reosultion reciprocal lattice maps (HRRLMs) in Figure 35 [207]. The position of SiGe peak in all maps is aligned to the Si peak imdicating neglible strain relaxation after initial vertical etch and in consequence of lateral etch steps.

**Figure 34.** The SEM images of cross section comparing the profile between wet etching and inductively coupled plasma (ICP) dry etching: (a) Wet etching SiGe with 6% HF/30%  $H_2O_2/99.8\%$  CH<sub>3</sub>COOH = 1:2:4 etching 8 min, and (b) ICP dry etching SiGe with CF<sub>4</sub> /O<sub>2</sub> /He = 4:1:5 [207].

Selective etching of Si leaves SiGe nanowires to obtain high mobility channels, therefore research in this area has remarkably boomed. Wet alkaline solutions such as NH<sub>4</sub>OH [208] and TMAH [209,210] have a high selectivity in silicon etching to SiGe, but all have obvious crystal orientation, which is due to the etching rate Si (100) > Si (110) > Si (111). Liu et al. reported that ACT<sup>R</sup> 210 and ACT <sup>R</sup> 301 reduced the crystal orientation behavior of etching and improved the selectivity ratio of Si (111)/SiGe etch to 13: 1 [211]. In order to overcome the wet crystal orientation anisotropy and liquid capillary effect, dry etching is preferred. The dry etch mainly includes SF<sub>6</sub>/CF<sub>4</sub>/H<sub>2</sub> (selectivity Si to Si<sub>0.5</sub>Ge<sub>0.5</sub> is about 10: 1) [212], CF<sub>4</sub>/H<sub>2</sub>/Ar (selectivity Si to Si<sub>0.5</sub>Ge<sub>0.5</sub> is about 30: 1) [25,213] and CF<sub>4</sub>/N<sub>2</sub>/O<sub>2</sub> (selectivity Si to Si<sub>0.5</sub>Ge<sub>0.5</sub> is about 10: 1) [214]. Both dry and wet etching methods overcome the crystal anisotropy issue, but the etching selection ratio still needs to be improved.

**Figure 35.** High-reosultion reciprocal lattice maps (HRRLMs) in the vicinity of the asymmetric (113) Bragg reflection acquired on SiGe/SiMLS: (**a**) Unprocessed structure; (**b**) after vertical anisotropic etch and 100:1 DHF wet clean, and (**c**) lateral isotropic SiGe selectivite by using ICP dry etching [207].

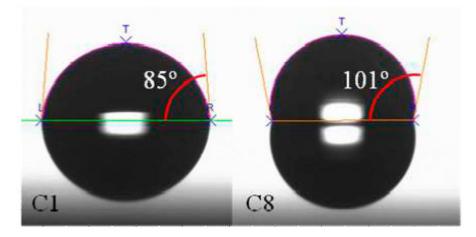

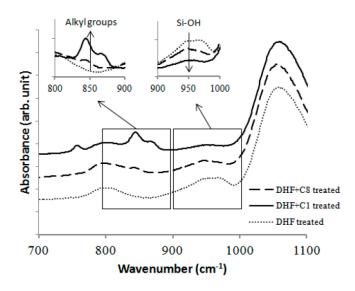

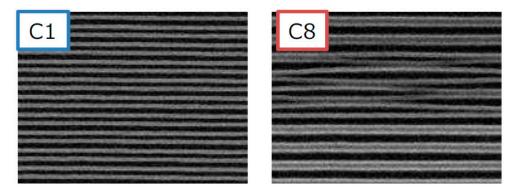

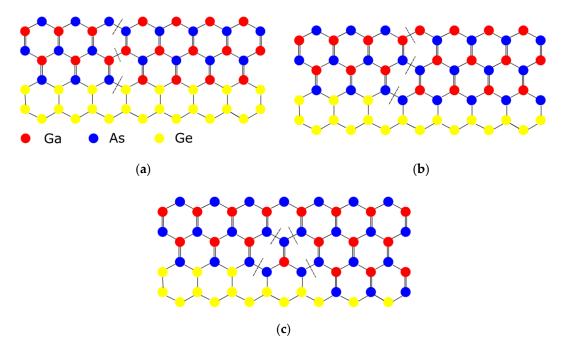

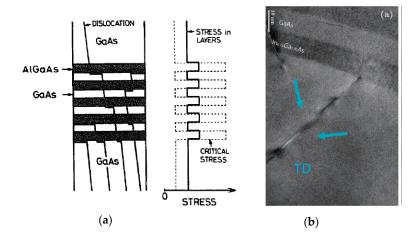

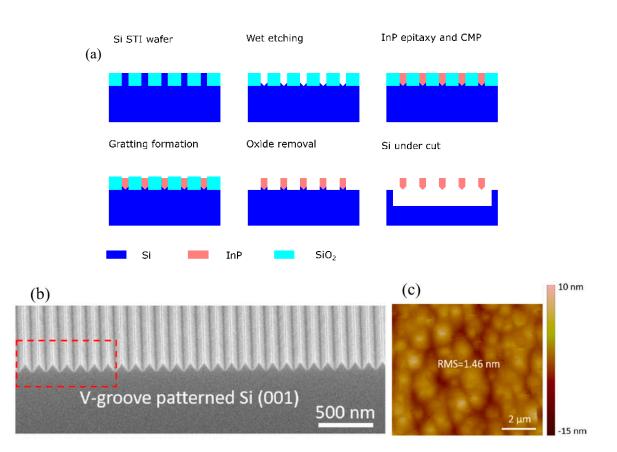

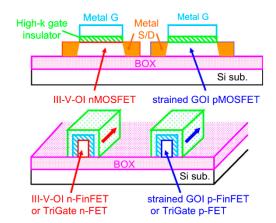

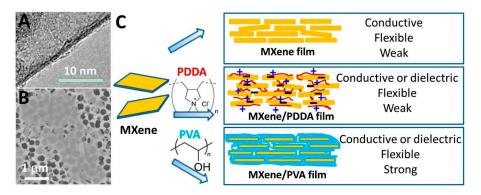

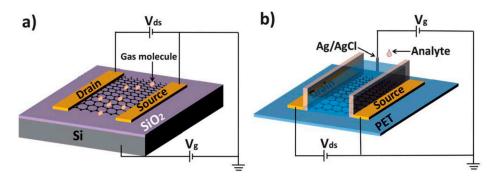

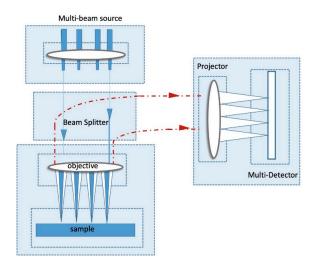

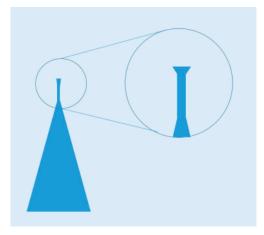

#### 10.2. Precise Selectivity Etching for Channel Partial Release