# A 2-kfps Sub-μW/pix Uncooled-PbSe Digital Imager with 10-bit DR Adjustment and FPN Correction for High-Speed and Low-Cost MWIR Applications

Josep Maria Margarit, *Student, IEEE*, Germán Vergara, Víctor Villamayor, Raúl Gutiérrez-Álvarez, Carlos Fernández-Montojo, Lluís Terés, and Francisco Serra-Graells, *Member, IEEE*

### **Abstract**

Mid-wavelength infrared (MWIR) thermography is an emerging technology with promising applications such as industrial monitoring, medicine and automotive, but its use in high-speed cameras is not yet widespread due to the lack of inexpensive sensor integration solutions and their common reliance on bulky cooling mechanisms. This work fills the gap by presenting a monolithic uncooled high-speed imager based on vapor-phase deposition lead selenide (VPD PbSe) photoconductors and a fully digital and configurable CMOS read-out integrated circuit (ROIC) to operate the MWIR imager. This ROIC features cancellation of PbSe dark current, compensation of its output capacitance and correction of the fixed pattern noise (FPN) caused by process non-uniformities in CMOS fabrication and detector deposition. The low-cost  $80\times80$  imager has been integrated using  $0.35~\mu m$  2P4M standard CMOS technology and PbSe detector post-processing with 135  $\mu m$  pixel pitch and 60 % fill factor values. Experimental opto-electrical performance exhibits 10-bit real-time FPN compensation and DR calibration over the entire focal plane operating at 2 kfps, sub-0.5 LSB inter-pixel crosstalk, sub- $\mu m$  pixel power consumption, and an overall figure of merit of 55 mK×ms.

### **Index Terms**

CMOS, imager, digital pixel sensor (DPS), fixed pattern noise (FPN), low-power, infrared, MWIR, PbSe, uncooled, high-speed, low-cost.

- J. M. Margarit, L. Terés and F. Serra-Graells are with Instituto de Microelectrónica de Barcelona IMB-CNM(CSIC), Spain (e-mail:josepmaria.margarit@imb-cnm.csic.es).

- G. Vergara, V. Villamayor, R. Gutiérrez-Álvarez and C. Fernández-Montojo are with New Infrared Technologies S.L., Spain. F. Serra-Graells is also with Universitat Autònoma de Barcelona, Spain.

### 1

# I. Introduction

NFRARED (IR) has always been a spectral region of interest for imagers due to the capability of matter to self emit at this wavelength range, in contrast to the illumination required in the visible, and the thermal information obtained from observed objects. This interest is in agreement with the large number of IR imagers incorporated into strategic, industrial, scientific and medical equipments for a wide range of applications like surface analysis by thermography [1], automotive night vision [2], object tracking [3] and weather forecast [4].

From the detector viewpoint, two major technologies are in practice dominating the IR imaging market. On the one hand, microbolometers [5] are the common choice for thermal imaging in the long-wavelength IR (LWIR) range, showing very low-cost figures thanks to their CMOS technology compatibility and uncooled operation. Although pixel pitch is being steadily improved [6], [7], microbolometers intrinsically suffer from limited signal sensitivity and frame rate (below 100-fps). On the other hand, quantum-well IR photodetectors (QWIP) [8] can cover those fields demanding both high-speed and high-sensitivity, typically in the short-wavelength IR (SWIR) range, at the expense of higher costs and power consumption due to their hybrid packaging and cryogenic cooling, respectively. An interesting alternative to avoid this tradeoff is the choice of lead selenide (PbSe) photoconductive technologies. These mid-wavelength IR (MWIR) detectors allow uncooled operation like microbolometers, but with the high-speed capabilities of their QWIP counterparts. Target applications include: automotive, metallurgy, glass and paper manufacturing, where process dynamics above the kHz play a crucial role; pollution monitoring, accordingly to the MWIR signature of carbon-based molecules; and transportation, as to prevent axis, wheel, motor overheating and malfunctioning combustion. A Noise Equivalent Temperature Difference (NETD) below 0.5 K is commonly required in these practical cases.

Classically, the severe drawbacks in terms of photoresponse uniformity and long term stability

of the chemical bath deposition (CBD) methods [9] used to build PbSe MWIR detectors have limited their use to linear imagers only. During last years, the introduction of PbSe technologies based on vapor phase deposition (VPD) [10] are enabling to overcome the previous CBD limitations, extending PbSe post-processing compatibility to CMOS technologies in order to obtain monolithic active focal plane arrays (FPAs) with high fill factors. In this sense, results from a 32×32 VPD PbSe CMOS MWIR imager prototype exceeding 1 kfps at room temperature have been reported [11].

From the CMOS circuit viewpoint, the use of PbSe detectors introduces specific design challenges both at FPA and at active pixel sensor (APS) levels of the imager. First, this type of IR detectors exhibits unitary dark-to-signal current ratios strongly higher than those from the rest of quantum light sensing technologies (typically orders of magnitude below unity). As a result, a direct cancellation mechanism of this PVT-dependent large offset current is needed inside each APS, which is not covered by the existing background suppression techniques [12], [13]. Second, the large parasitic capacitance of the post-processed PbSe detector can limit signal bandwidth in case of using it as the pixel integration capacitor. Hence, in-pixel capacitive transimpedance amplifiers (CTIAs) [14]–[17] are required in practice to exploit the high-speed capabilities of PbSe detectors. Third, due to the nature of the VPD post-processing, fixed pattern noise (FPN) plays an important role on the response of PbSe FPAs. In consequence, both offset (dark current) and gain (responsivity) corrections are also needed inside each APS. A solution for this double compensation is not addressed by the available FPN reduction approaches [14], [18]–[22]. Finally, very low-power operation is mandatory for the CMOS pixel circuits to minimize thermal effects on the uncooled MWIR detector stacked on top of the APS.

In order to achieve the above circuit design challenges, this paper proposes an imager architecture for VPD PbSe CMOS imagers with dynamic and digital programmability of both offset and

gain parameters for each individual pixel. The device takes advantage of a sub- $\mu$ W truly digital pixel sensor (DPS) with CTIA-based integrator and built-in 10-bit analog-to-digital converter (ADC) to offer kfps uncooled imaging in the MWIR spectrum. The development of this high-speed imager was initially announced in [23], but no details about its design nor its experimental results were revealed. The present paper is organized as follows. General imager characteristics and read-out architecture are detailed in Sections II and IV, respectively. Section III reviews the uncooled MWIR detector technology. The monolithic PbSe CMOS integration of the resulting imager is described in Section V, while Section VI compiles all the experimental MWIR results. Finally, conclusions are summarized in Section VII.

# II. DIGITAL IMAGER OVERVIEW

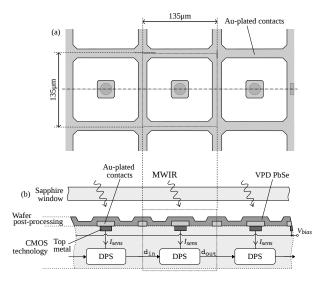

Basically, the imager of Fig. 1 is constituted of a digital-only I/O focal plane of 80 fully independent rows of daisy chains of 80 DPS cells each. Oppositely to traditional image sensor architectures where pixel bias, digital control, row/column decoding and/or ADC is distributed outside the FPA [13], [14], [16], [18], [20], [22], our approach integrates all functionality locally inside each pixel avoiding any analog signal sharing between them. The PbSe quantum detector described in Section III is deposited on top of the CMOS array and performs photoconductive transduction of the incoming MWIR radiation. This input current is acquired, conditioned and converted to digital domain, at pixel level, in order to deliver high-SNR 10-bit output video frame sequences. To perform such tasks, every pixel offers individually programmable adjustment of both offset and gain parameters. Since imager pixels can be configured at the same time and resolution as the output frame code is read, both technology-dependent spatial noise and dynamic range on output images can be improved in real-time and without noticeable speed costs.

All pixels in the FPA are accessed by rows, and operated according to two iterative global modes: synchronous communication and asynchronous acquisition (Fig. 1(c)). During communication

nication, the 10 bit/pix correction maps are serially written-in through the bus of row inputs, and translated to its corresponding in-pixel analog circuit configuration; meanwhile, the 10 bit/pix compensated frames are also serially read-out through the bus of row outputs. Offset and gain maps are entered in different programming-in/read-out time slots (e.g. alternate frames) at a variable refreshing frequency adjustable to system requirements. Over acquisition, all pixels in the FPA are set up to collect the detector currents and to asynchronously integrate their effective values to digital 10-bit words. The resulting data is stored in each pixel and read out in the next frame cycle. Both DAC and ADC are reset while in communication before and after D/A conversion, respectively. Fig. 1 also displays a practical scenario of complete offset and gain tuning with in-pixel FPN compensation. A frame set with no offset compensation and a common medium gain value usually exhibits the visual noise of Fig. 1(a), whereas appropriate individual pixel calibration significantly optimizes image generation as depicted in Fig. 1(b).

# III. UNCOOLED MWIR PBSE PHOTOCONDUCTIVE TECHNOLOGY

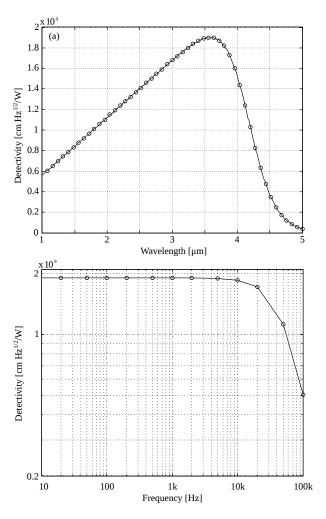

Polycrystalline PbSe is a quantum photoconductor composed of a compact layer of PbSe microcrystals to provide detectivities up to  $10^9$  cm $\sqrt{\text{Hz/W}}$  and  $\mu\text{s}$ -range response times in the MWIR spectrum range at room temperature. Such characteristics make PbSe a remarkable candidate for high-speed and low-cost uncooled IR detection. Standard polycrystalline PbSe films are produced by Chemical Bath Deposition method (CBD). Wet CBD imposes serious technological limitations on uniformity and reproducibility to manufacture medium and large-scale 2D detector arrays in monolithic devices. Primary reasons the incompatibility between wet processing and the multi-level metal substrates required in order to obtain good filling factors and low metal density at detector contacts. To overcome this deficiencies, an alternative procedure based on thermal evaporation of PbSe in vacuum followed by a specific sensitization method was developed [10]. As depicted in Fig. 2, the new VPD method deposits a thin layer of PbSe

on standard CMOS wafers that provide the read-out electronics, offering good yield in common 8-inch wafers and compatibility with complex monolithic multilayer structures like interference filters.

In order to integrate PbSe detectors and CMOS circuits in a single die, two key technological bottlenecks had to be saved: compatibility between detector and circuit materials at their interface, and CMOS operational drifts that PbSe sensitization treatments at high temperature could induce. For the former, PbSe was contacted by gold (Au) on top of a stacked metal layer to access each individual CMOS sensor. For the latter, a two-fold strategy was selected as follows: PbSe post-processing was redefined in order to lower the temperature and duration of each technological step, and design rules for high-stress environments were strictly observed according to foundry recommendations. All phases and masks were optimized to post-process standard 8-inch 0.35  $\mu$ m 2P4M CMOS wafers. The obtained pixel stacked structure allows DPS fill factors to exceed 50 %. Unlike microbolometers, photoconductive PbSe detectors do not need to be operated in vacuum to minimize thermal conductivity effects from surrounding environment. Hence, the whole IR imager can be encapsulated in low-cost standard packages with sapphire window.

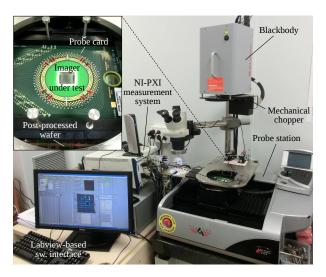

Fig. 3 shows the MWIR response of the post-processed PbSe detector at room temperature, which returns the typical triangular-shaped spectral profile of quantum detectors. When cooled, the detector peak sensitivity is shifted towards longer wavelengths (e.g. 4 μm at 253 K). Signal modulation bandwidth under uncooled operation extends up to 60 kHz, and reduces at lower temperatures with an approximate rate of 2.7 %/K. This behavior is driven by the influence of detector resistance on its internal RC product. The spectral properties of VPD PbSe were studied using the blackbody of Fig. 9 and f/1 aperture optics.

A common relevant metric used to characterize the performance of IR imaging systems is the noise equivalent temperature difference (NETD), which evaluates the response of such systems

in terms of thermal sensitivity. It is described by (1) as the temperature change  $\Delta T$ , for incident radiation, that gives an output signal change  $\Delta V_s$  equal to the RMS noise level  $V_n$  [24]

$$NETD = V_n \frac{\Delta T}{\Delta V_s} \tag{1}$$

Background radiation is usually the main source of noise in IR quantum detectors. Therefore, at the background limited performance (BLIP) conditions photon-induced shot noise dominates NETD, which can be approximated by the equation

$$NETD = \frac{1}{\tau_o C_{T\lambda} \eta_{BLIP} SNR_B} = \frac{1}{\tau_o C_{T\lambda} \eta_{BLIP} \sqrt{N_c}}$$

(2)

where  $\tau_o$  stands for the optics transmission,  $C_{T\lambda}$  is the thermal contrast,  $\eta_{BLIP}$  the percentage of BLIP (i.e. the ratio of photon shot noise to composite FPA noise),  $SNR_B$  the signal-to-noise ratio at background radiation and  $N_c$  is the number of photogenerated carriers collected for a given acquisition time  $T_{acq}$ . Because of the high resistive (typically around 1 M $\Omega$ ) nature of PbSe detectors, current read-out at constant voltage bias is preferred over voltage read-out at constant current strategies. In practice, PbSe exhibits both noticeable background photogeneration mean and deviation due to uncooled operation and the amorphous nature of its structure, respectively. The latter can lead to signal-to-dark current ratios close to unity under common radiation scenarios (e.g. 1  $\mu$ A for a 1-V biasing). The measured parameters of the VPD PbSe photoconductor are summarized in Table I. NETD performance was measured at a blackbody temperature of 600 K, accordingly to the MWIR spectral range of the imager.

# IV. FULLY FPN-COMPENSATED DPS-BASED READ-OUT ARCHITECTURE

When assessing the performance of APS-based imagers, the NETD figure of (2) is extended to include noise contributions of the read-out circuitry itself. Considering all major noise sources uncorrelated, the percentage of BLIP in integrating topologies can be described as

$$\eta_{BLIP_{APS}} = \left(1 + \frac{\sigma_{ROIC}^2}{\sigma_{photon}^2}\right)^{-1/2} \simeq \sqrt{N_c} \left(N_c + \sigma_{det}^2 + \sigma_{samp}^2 + \sigma_{integ,ir}^2 + \sigma_{drv,ir}^2 + \sigma_{MUX,ir}^2 + \sigma_{ADC,ir}^2\right)^{-1/2}$$

(3)

where  $\sigma^2_{photon}$  is the shot noise power of photon background in carriers and  $\sigma^2_{ROIC}$  stands for the sum of all ROIC noise contributions, mainly: composite dark current, thermal and flicker detector noise  $(\sigma^2_{det})$ , kTC noise of the sample-and-hold stage  $(\sigma^2_{samp})$ , and the input-referred noises of integrator  $(\sigma^2_{integ,ir})$ , line driver  $(\sigma^2_{drv,ir})$ , multiplexer  $(\sigma^2_{MUX,ir})$  and ADC  $(\sigma^2_{ADC,ir})$ .

In order to improve signal integrity and grant high-speed operation at low-power figures, the proposed read-out architecture of Fig. 1 implements a fully digital I/O interface with massive pixel-parallel asynchronous A/D conversion. First point to note in this figure is the absence of any analog bus. As a result,  $\sigma^2_{MUX,ir}$  and  $\sigma^2_{drv,ir}$  contributions are automatically removed from (3). Second, in-pixel ADC allows to reduce the sampling ratio (so equivalent noise bandwidth) proportionally to the FPA number of rows (M) and/or columns (N) as to external or column/row-wise ADC, respectively. In consequence, and supposing the ADC is thermal noise limited,  $\sigma^2_{ADC,ir}$  can be downscaled up to  $\sigma^2_{ADC,ir}/MN$  at the cost of even stronger power and area circuit design constrains. For this purpose, asynchronous integrate-and-fire modulation [25], [26] and in-situ digital low-pass filtering are chosen for the in-pixel ADC. The resulting ADC architecture opens the possibility of pixel area optimization against kTC noise, since both capacitance of the analog integrator and capacity of the digital integrator play an equivalent role.

Compared with other kfps DPS-based CMOS implementations like [27], our design combines the aforementioned pulse-density modulation with all-digital and local-only signaling to curtail crosstalk in critical analog nodes of the layout. Both spike-counting and local interconnectivity avoid tracing pulsating signal paths throughout the focal plane, with the latter also allowing to drastically optimize pixel digital output buffers in terms of power; local biasing provides

additional noise immunity by cutting off coupling noise on power supply lines. To further avoid the presence of switching perturbation along integration, acquisition and communication are separated in two well-differentiated phases as described in Section II: no clock is generated while performing A/D conversion. Switching noise mainly arises in the substrate and propagates through circuit asymmetries over the pixel sensor [28]. The presence of perturbations on power supply nodes, either at routing or substrate level, are reflected in higher  $\sigma_{integ,ir}^2$  and  $\sigma_{ADC,ir}^2$  values. They are specially noticeable in the quantizer stage as comparator jitter noise and can severely limit the performance of the system in terms of NETD. Last but not least, every DPS cell includes a built-in DAC to configure both offset-cancellation and gain tuning at individual pixels. Apart from attenuating detector and CMOS FPN along the focal plane, offset programming circuitry allows to boost the number of effective photogenerated carriers integrated in acquisition, and provides additional NETD enhancement according to (2). Under this scheme, offset-correction  $\sigma_{offs}^2$  and integrator  $\sigma_{integ,ir}^2$  noises become key ROIC contributors during acquisition. The former adds to  $\sigma_{det}^2$  in (4) as input noise current  $\sigma_{offs}^2$ :

$$\eta_{BLIP_{DPS}} \simeq \sqrt{N_c} \left( N_c + \sigma_{det}^2 + \sigma_{offs}^2 + \sigma_{integ,ir}^2 + \sigma_{ADC,ir}^2 \right)^{-1/2}$$

(4)

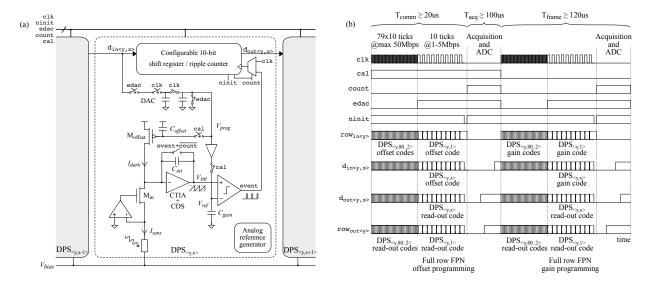

The DPS circuits used in the present imager are based on the nanopower topologies introduced by authors in [29]. This implementation is adapted to the particular operating conditions of the PbSe detector and to increase the yield of its monolithic integration. Layout is compacted to a pitch of 135  $\mu$ m for a low-cost 0.35  $\mu$ m 2P4M CMOS technology. Every pixel cell shown in Fig. 4(a) includes its own analog reference and bias generator, and DAC for FPN suppression. Furthermore, and in order to avoid input bandwidth limitations due to the detector capacitance values of Table I, an specific circuit for input capacitance compensation is also incorporated.

As depicted in Fig. 4(b), only 5 control signals are needed to operate all the DPSs of the focal plane and, by extension, the entire read-out integrated circuit (ROIC): cal is used to select

between offset or gain programming, edac to enable the former offset/gain configuration and define its resolution, count to select between acquisition or communication mode, ninit to initialize acquisition and clk to synchronize digital program-in/read-out communications. All DPSs follow the two global communication and acquisition modes previously described. In the first case, offset and gain FPN corrections can be serially programmed at every other frame as  $V_{prog}$  through the 10-bit switched-capacitor DAC of Fig. 4(a) and the chronogram of Fig. 4(b) according to the equation

$$V_{prog} = V_{DD} \frac{1 - 2^{-N_{bit}}}{2^{N_{bit}} - 1} d_{in} \doteq G_{DAC} d_{in}$$

(5)

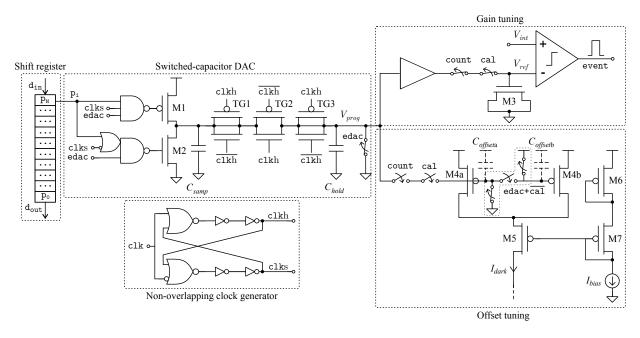

where  $G_{DAC}$  and  $N_{bit}$  stand for the DAC conversion gain and the number of effective bits used for programming, respectively. Even under ideally null FPN conditions, ADC gain tunability offers an additional mechanism to dynamically change the DPS contrast and, consequently, to adapt image DR by regions according to instantaneous illumination conditions. Fig. 5 details the circuit implementation for offset and gain tuning. A non-overlapping clock is mandatory to provide proper isolation between sample and hold capacitances along programming. In order to minimize undesired injection to  $C_{samp}$ , charge in this node is added or removed through the direct path composed by minimum-size M1-M2 transistors. These devices are controlled by the corresponding logical function between each serially programmed code  $p_{1}$ , as well as the non-overlapped sample clock clks and enable edac signals. The charge stored in  $C_{samp}$  is then recombined with  $C_{hold}$  through dummy-switch devices so as to compensate for both clock feedthrough and charge injection effects. To keep the desired linear response of (5), DAC capacitances were cautiously matched and shielded from neighboring nodes.

Depending on count state, the resulting  $V_{ref}$  analog value is either stored in M3 as comparator threshold reference voltage or combined again in  $C_{offset}$  as an M4 biasing gate voltage for  $I_{dark}$  generation. Thus, the  $M_{offset}$  device of Fig. 4(a) acts as a programmable DC current source

constituted, in practice, by M4 and M5 in Fig. 5. The lower 1/f noise of pFET stages facilitates to keep this phenomena below what is the dominant detector noise component. In this sense, M4a and M4b were accurately sized and paired to exhibit low flicker levels, as well as to cover its large (up to 5  $\mu$ A) dark current excursion. The cascode device M5 was also included to safeguard offset cancellation from channel modulation and coupling distortion.

Back to Fig. 4(a), in acquisition mode the MWIR detector current  $I_{sens}$  is read through  $M_{in}$ : its local OpAmp control supplies a low enough input resistance to compensate for detector parasitic capacitance and set the differential biasing of PbSe photoconductor at 1 V.  $I_{dark}$  offset is then subtracted, and low-frequency components of the outcoming effective current are integrated by the CTIA. The resulting voltage ramp  $V_{int}$  is quantified at 1 bit by the comparator according to the ADC gain  $V_{ref}$  retained in  $C_{gain}$ . All generated events are fed back to reset the CTIA block, resulting at event in the asynchronous current-to-frequency conversion of the IR-radiation reliant value. Over an acquisition time of hundreds of  $\mu$ s, the digital module acts as a 10-bit ripple counter and completes the time-domain A/D conversion by low-pass filtering the asynchronous pulse-density modulated (PDM) stream. In the communication phase of the next frame, event generation is disabled and the 10-bit internal binary memory is reconfigured to provide a serial scanning path along the 80 DPS in every row of the focal plane, as depicted in Fig. 4(b). Considering CTIA reset times, the closed-loop operation of the previous circuitry generates a spiking signal of frequency

$$f_{event} = \frac{1}{T_{reset} + \frac{C_{int}V_{ref}}{(I_{sens} - I_{dark})}} \tag{6}$$

which corresponds to a digital inter-frame counted word of value

$$d_{\text{out}} = \frac{f_{event}}{f_{acq}} = \frac{T_{acq}}{T_{reset} + \frac{C_{int}V_{ref}}{(I_{sens} - I_{doub})}}$$

(7)

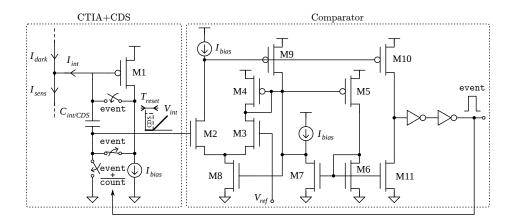

Fig. 6 draws the detailed schematic employed for pulse-density modulation. M1 and  $C_{int/CDS}$

constitute the class-AB CTIA stage, whose flicker contributions are canceled at reset by its particular correlated double sampling (CDS) triple-switch scheme. Along event duration, M1 noise is integrated in the same  $C_{int/CDS}$  and removed from the effective noise charge. Previous input compensation also allows to reduce the influence of the detector capacitance over the integrator response. Together with the posterior low-pass filtering provided by the counter,  $C_{int/CDS}$  can be compacted to 500 fF while keeping both kTC contributions to  $\sigma_{integ,ir}^2$  in (4) and CTIA noise transfer gain at acceptable levels.  $V_{int}$  is quantized at the specified  $V_{ref}$  voltage by the high input/output-range comparator M2-M11. This topology is designed to deliver fast reset times at low-power operation by means of the dynamic biasing supplied by the positive feedback M13-M14 during threshold reach. All  $I_{bias}$  sources are optimized for sub-100nA static low-current consumption.

# V. MONOLITHIC PBSE-CMOS INTEGRATION

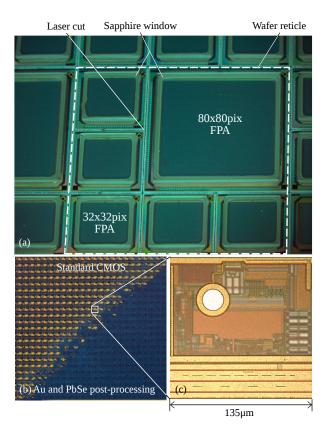

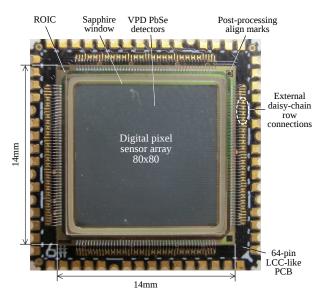

Fig. 7 shows the proposed  $80\times80$  pixel imager after being integrated, together with other  $32\times32$  pixel designs, over 8-inch wafers with standard  $0.35\mu m$  2P4M CMOS technology and the PbSe post-processing steps described in Section III. The  $135~\mu m$  pixel size was selected according to pitch limitations imposed by the Au contact lithography itself. As shown in Fig. 7(c), metal 4 was mainly reserved to access the IR detector. Control lines were routed horizontally using metal 3, also employed to shield the in-pixel switched-capacitor DAC. Inside the FPA, pixels were arranged in alternate left-right row I/O directionality to allow for external concatenation. The fabricated imager occupied a total area of  $14\times14~mm^2$  with 196 pads distributed along the four sides of the die. The succeeding low-cost packaging procedure included the following steps: Firstly, a rectangular sapphire glass was used in order to coat and protect the FPA from damaging external contamination or scratch. Wafers were then diced by laser and all pads of the ROIC were wire-bonded to the custom chip-carrier PCB of Fig. 8. The board accesses the

focal plane in 5-row groups, with an equivalent 16-bit I/O bus, matching standard 64-pin leaded chip-carrier (LCC) sockets. Is this external serialization which, in practice, limits the maximum frame rate of the imager to an equivalent 480x480-pixel FPA parallel-access time. Packaging was finally sheltered using standard dam and fill techniques.

### VI. EXPERIMENTAL RESULTS

The integrated imager was electro-optically tested after on-wafer screening using the setup shown in Fig. 9. This test bench was composed of a CI Systems SR-200 high-emissivity IR blackbody with mechanical chopping, a National Instruments (NI) PXI-1042 8-slot digital measurement system and a Pegasus S200 semi-automatic 200-mm probe station from Wentworth Laboratories. Custom NI Labview-based interfaces were developed for both on-wafer and in-package testing, which included the generation of the operational chronogram of Fig. 4(b).

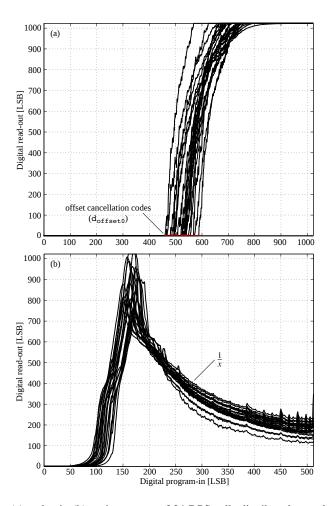

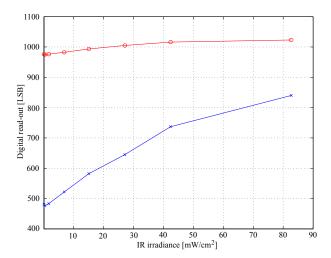

Fig. 10 shows the experimental tuning response of 24 different DPS cells to both offset and gain parameters. Measurements were taken without IR illumination. In the first case, all gain programming codes (i.e.  $d_{gain}$ ) were fixed to 226 LSB. The full 10-bit range of the in-pixel DAC depicted in Fig. 4 is devoted to match the dark current  $I_{dark}$  dispersion exhibited by PbSe detectors according to the  $d_{offset}$  tuning curve of Fig. 10(a) and equation (7). Gain programming was performed after individual pixel offset calibration so that all outputs are aligned at half full scale for the same gain code of 226 LSB. As it can be clearly seen in Fig. 10(b), digital output reading follows the expected 1/x law also predicted by (7). Under negligible reset times, substituting  $V_{ref}$  by (5) in the previous equation results in the tuning characteristic

$$d_{\text{out}} = \frac{T_{acq}}{C_{int}G_{DAC}d_{\text{gain}}}(I_{sens} - I_{dark})$$

(8)

inversely proportional to the input gain programming code. Integral non-linearities arise mainly from capacitive mismatching at both sample and hold nodes, and residual change injection and

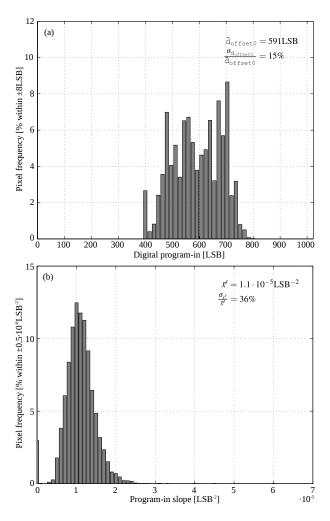

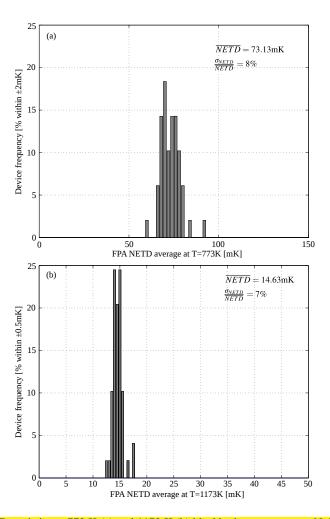

clock feedthrough effects at DAC switches. In practice, there is a lower boundary at which the reference voltage for the comparator of Fig. 4 is no longer operative. Higher values are not effective either, as the transfer curve saturates beyond the MSB gain code. Thus,  $V_{ref}$  is programmed within a 9-bit span in order to compensate variations on both detector sensitivity and ADC conversion gain. The statistical results of Fig. 11 were obtained applying the same programming codes to the whole set of 6400 pixels of the focal plane, and corroborate the necessity of the included FPN correction mechanisms at pixel level.

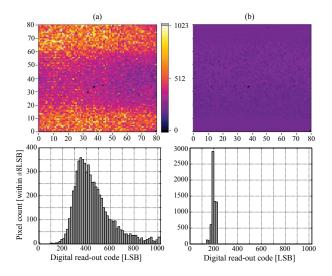

Experimental results of the built-in FPN cancellation capabilities are presented in Fig. 12 to 14. All characteristics reported in this section were obtained setting the clock frequency to 10 MHz during communication phase except for the final 10 clock periods devoted to in-pixel DAC operation, when it was scaled down to 3 MHz. To generate large and uniform illumination, a 1173 K IR dark body was placed 10.75 cm away from the imager of Fig. 8, and signal strength was regulated by using 8 different apertures. Integration time was 500  $\mu$ s for an operating frame rate of 1.1 kfps. No optics were used in these measurements.

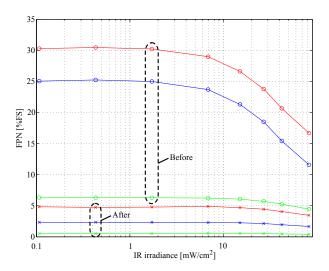

The raw image shown in Fig. 12(a) corresponds to the digital read-out with null IR illumination when flat FPN code maps are programmed in all active pixels. On-chip frame equalization is achieved in Fig. 12(b) after applying offset and gain correction. Both maps are previously computed by an automatic calibration routine running in the NI-PXI system, configured in this case for the decimal output reading code 200 LSB, but reducible down to 50 LSB for the target DR extension of 60 dB. FPN calibration fingerprints are stored in the same system and recomputed only in case of severe temperature drifts. Fig. 13 shows pixel-to-pixel, row-to-row and column-to-column FPN statistics, expressed in percentages over full scale (1023 LSB), for the entire focal plane. Non-uniformities in the imager arise at row level in the direction of power line routing. Calibration of the image sensor manages to reduce all FPN values under 5 % full

scale. FPN decays in the right side of the figure are caused by saturation of pixel digital counts. Pre and post-equalization imager read-out codes evolve as described in (7), with good linearity up to the frequency limit imposed by  $T_{reset}$ , as reported in Fig. 14.

Concerning temporal noise, the NETD results of Fig. 15 were measured throughout the 49 dices that compose a full wafer. NETD improves with temperature according to the higher irradiance of hotter surfaces, displaying variances below 10 %. Instantaneous read-out noise was measured 4 LSB for an acquisition time of 200  $\mu$ s. Thanks to the operational flexibility of the imager, the predominant thermal contributions of  $\sigma_{integ,ir}^2$  and  $\sigma_{offs}^2$  in (4) can be filtered out below the single-bit threshold by scaling  $T_{acq}$ , with a rate close to the square-root of cut-off frequency scaling, to a frame speed below 300 fps. Moreover, because the equivalent integrated signal increases proportionally to exposure time, SNR may be simultaneously risen by tuning each pixel gain in order to avoid saturation.

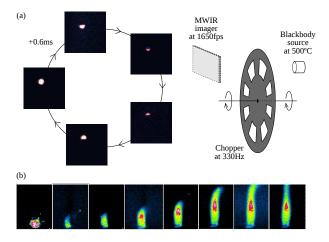

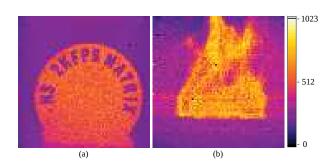

Fig. 16 presents dynamic captures of the MWIR imager, under uncooled operation, to a 330-Hz pulsing bright spot generated by mechanical chopping. Dark body temperature is in this case 773 K, placed at a distance of 40 cm from the FPA, using 3-cm focal length and f/1 aperture optics. The resulting digital frame sequence read at 1650 fps ratifies the speed capabilities of the imager. In the same figure, the ignition sequence of a lighter is also given as a practical high-speed application example. In proof of image uniformity and sensitivity, Fig. 17 shows two raw photograms acquired at this same rate from different scenes and devices. The absence of inter-pixel crosstalk evinces from the spatial acuity of disk slots in Fig. 17(a), even with the small array size and current detector pitch constraints of the imager. Fig. 17(b) displays effective temperature screening for a fast-moving flame. In terms of production yield, the total amount of operative pixels exceeds the 99.9 % of every FPA. Dead pixels are essentially sparse and can be easily interpolated though posterior post-processing.

Table II summarizes performance compared to state-of-art uncooled IR imagers. Even implementing the full A/D conversion and dual FPN compensation inside each active pixel, the imager keeps static power consumption below 1  $\mu$ W/pix. The compact pitch reported in [7] is achieved at the cost of having analog pixel output, which may be prone to inter-pixel crosstalk and to extra FPN added at column or row levels, compared to all-digital I/O active pixels. Since the area of the DPS circuit proposed here is dominated by the digital block, pixel pitch can be reduced by downscaling the target CMOS technology. To the best of our knowledge this is the only uncooled IR imager operating at 2 kfps and supplying independent digital offset and gain tuning capabilities for FPN cancellation and DR adjustment at every pixel. The proposed architecture features an overall figure of merit NETD× $\tau_{imager}$  of 55 mK×ms, nearly one order of magnitude beyond the latest microbolometer frame-based imagers [7].

# VII. CONCLUSIONS

An  $80\times80$  pixel MWIR PbSe imager has been integrated in standard 0.35  $\mu$ m 2P4M CMOS technology. It is the first high-speed IR quantum image sensor monolithically fabricated in a standard VLSI CMOS technology and operates without any need of external cooling nor packaging in vacuum. The resulting low-cost imager has a fill factor of 60 % and it is capable of delivering frame rates up to 2 kfps with on-the-fly offset and gain FPN digital compensation at pixel level, 10-bit read-out and sub- $\mu$ W/pix of static power consumption. Exhaustive electro-optical results prove the architectural efficacy of the read-out circuitry, which performs an FPN lower than 5 % and a FOM of 55 mK×ms.

### ACKNOWLEDGMENT

This work has been partially funded by the Avanza Competitividad I+D+i TSI-020100-2010-738 project from the Ministry of Energy, Industry and Tourism of Spain.

### REFERENCES

- [1] L. Cheng and G. Y. Tian, "Surface Crack Detection for Carbon Fiber Reinforced Plastic (CFRP) Materials Using Pulsed Eddy Current Thermography," *IEEE Sensors J.*, vol. 11, no. 12, pp. 3261–3268, Dec 2011.

- [2] J. H. Lim, O. Tsimhoni, and Y. Liu, "Investigation of Driver Performance With Night Vision and Pedestrian Detection Systems - Part I: Empirical Study on Visual Clutter and Glance Behavior," *IEEE Trans. Intell. Transp. Syst.*, vol. 11, no. 3, pp. 670–677, Sep 2010.

- [3] F. Lamberti, A. Sanna, and G. Paravati, "Improving Robustness of Infrared Target Tracking Algorithms Based on Template Matching," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 47, no. 2, pp. 1467–1480, Apr 2011.

- [4] N. Jaiswal and C. Kishtawal, "Objective Detection of Center of Tropical Cyclone in Remotely Sensed Infrared Images," *IEEE J. Sel. Topics Appl. Earth Observations Remote Sens.*, vol. 6, no. 2, pp. 1031–1035, 2013.

- [5] C. Posch, D. Matolin, R. Wohlgenannt, T. Maier, and M. Litzenberger, "A Microbolometer Asynchronous Dynamic Vision Sensor for LWIR," *IEEE Sensors J.*, vol. 9, no. 6, pp. 654–664, Jun 2009.

- [6] P. Robert, J. Tissot, D. Pochic, V. Gravot, F. Bonnaire, H. Clerambault, A. Durand, and S. Tinnes, "Uncooled 17μm 1/4 VGA IRFPA Development for Compact and Low Power Systems," in *Proceedings of the SPIE*, ser. Electro-Optical and Infrared Systems: Technology and Applications IX, vol. 8541, 2012.

- [7] B. Dupont, A. Dupret, S. Becker, A. Hamelin, F. Guellec, P. Imperinetti, and W. Rabaud, "A [10°C; 70°C] 640x480 17μm Pixel Pitch TEC-Less IR Bolometer Imager with Below 50mK and Below 4V Power Supply," in *Proceedings of the International Solid-State Circuits Conference*. IEEE, February 2013, pp. 394–396.

- [8] S. Gunapala, S. Bandara, J. K. Liu, J. Mumolo, D. Ting, C. J. Hill, J. Nguyen, B. Simolon, J. Woolaway, S. Wang, W. Li, P. LeVan, and M. Tidrow, "Demonstration of Megapixel Dual-Band QWIP Focal Plane Array," *IEEE J. Quantum Electron.*, vol. 46, no. 2, pp. 285–293, Feb 2010.

- [9] T. H. Johnson, "Solutions and Methods for Depositing Lead Selenide," US Patent 3 178 312, 1965.

- [10] G. Vergara, R. Almazán, L. Gómez, M. Verdu, P. Rodríguez, and M. T. Montojo, "Method of Treating Polycristalline Lead Selenide Infrared Detectors," European Patent 1 852 920, 2007.

- [11] G. Vergara, R. Linares-Herrero, R. Gutiérrez-Álvarez, M. T. Montojo, C. Fernández-Montojo, A. Baldasano-Ramírez, and G. Fernández-Berzosa, "VPD PbSe Technology Fills the Existing Gap in Uncooled Low-Cost and Fast IR Imagers," in Proceedings of the SPIE, ser. Infrared Technology and Applications XXXVII, vol. 8012, May 2011.

- [12] D. Woo, I. Nam, and H. Lee, "Smart Reset Control for Wide-Dynamic-Range LWIR FPAs," *IEEE Sensors J.*, vol. 11, no. 1, pp. 131–136, Jan 2011.

- [13] N. Cottini, M. Gottardi, N. Massari, R. Passerone, and Z. Smilansky, "A 33-µW 64×64 Pixel Vision Sensor Embedding

- Robust Dynamic Background Subtraction for Event Detection and Scene Interpretation," *IEEE J. Solid-State Circuits*, vol. 48, no. 3, pp. 850–863, Mar 2013.

- [14] M. Perenzoni, N. Massari, D. Stoppa, L. Pancheri, M. Malfatti, and L. Gonzo, "A 160×120-Pixels Range Camera With In-Pixel Correlated Double Sampling and Fixed-Pattern Noise Correction," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1672–1681, Jul 2011.

- [15] K. Murari, R. Etienne-Cummings, N. Thakor, and G. Cauwenberghs, "A CMOS In-Pixel CTIA High-Sensitivity Fluorescence Imager," *IEEE Trans. Biomed. Circuits Syst.*, vol. 5, no. 5, pp. 449–458, Oct 2011.

- [16] R. Xu, B. Liu, and J. Yuan, "A 1500-fps Highly Sensitive 256×256 CMOS Imaging Sensor With In-Pixel Calibration," *IEEE J. Solid-State Circuits*, vol. 6, no. 6, pp. 1408–1418, Jun 2012.

- [17] H.-S. Kim, S.-W. Han, J.-H. Yang, S. Kim, Y. Kim, S. Kim, D.-K. Yoon, J.-S. Lee, J.-C. Park, Y. Sung, S.-D. Lee, S.-T. Ryu, and G.-H. Cho, "An Asynchronous Sampling-Based 128×128 Direct Photon-Counting X-Ray Image Detector with Multi-Energy Discrimination and High Spatial Resolution," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 541–558, Feb 2013.

- [18] M. Snoeij, A. Theuwissen, K. A. A. Makinwa, and J. Huijsing, "A CMOS Imager With Column-Level ADC Using Dynamic Column Fixed-Pattern Noise Reduction," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 3007–3015, Dec 2006.

- [19] S. Otim, B. Choubey, D. Joseph, and S. Collins, "Characterization and Simple Fixed Pattern Noise Correction in Wide Dynamic Range "Logarithmic" Imagers," *IEEE Trans. Instrum. Meas.*, vol. 56, no. 5, pp. 1910–1916, Oct 2007.

- [20] D. Das and S. Collins, "Fixed-Pattern-Noise Correction for an Integrating Wide-Dynamic-Range CMOS Image Sensor," IEEE Trans. Electron Devices, vol. 60, no. 1, pp. 314–319, Jan 2013.

- [21] T. Serrano-Gotarredona and B. Linares-Barranco, "A 128×128 1.5% Contrast Sensitivity 0.9% FPN 3-μs Latency 4-mW Asynchronous Frame-Free Dynamic Vision Sensor Using Transimpedance Preamplifiers," *IEEE J. Solid-State Circuits*, vol. 48, no. 3, pp. 827–838, Mar 2013.

- [22] J. Lee, I. Baek, D. Yang, and K. Yang, "On-Chip FPN Calibration for a Linear-Logarithmic APS Using Two-Step Charge Transfer," *IEEE Trans. Electron Devices*, vol. 60, no. 6, pp. 1989–1994, Jun 2013.

- [23] G. Vergara, R. Linares-Herrero, R. Gutierrez-Alvarez, C. Fernandez-Montojo, L. J. Gomez, V. Villamayor, A. Baldasano-Ramirez, and M. T. Montojo, "80×80 VPD PbSe: The First Uncooled MWIR FPA Monolithically Integrated with a Si-CMOS ROIC," in *Proceedings of the SPIE*, ser. Infrared Technology and Applications XXXIX, vol. 8704, May 2013.

- [24] A. Rogalski, "Progress in focal plane array technologies," Progress in Quantum Electronics, vol. 36, pp. 342–473, 2012.

- [25] S. Ouzounov, E. Roza, J. Hegt, G. van der Weide, and A. van Roermund, "Analysis and design of high-performance asynchronous sigma-delta modulators with a binary quantizer," *IEEE J. Solid-State Circuits*, vol. 41, no. 3, pp. 588–596, 2006.

- [26] A. Alvarado, M. Rastogi, J. Harris, and J. Principe, "The integrate-and-fire sampler: A special type of asynchronous  $\Sigma \Delta$

- modulator," in Proceedings of the International Symposium on Circuits and Systems, 2011, pp. 2031–2034.

- [27] S. Kleinfelder, S. Lim, X. Liu, and A. El-Gamal, "A 10000 Frames/s CMOS Digital Pixel Sensor," *IEEE J. Solid-State Circuits*, vol. 12, no. 12, pp. 2049–2059, Dec 2001.

- [28] M. Peng and H.-S. Lee, "Study of Substrate Noise and Techniques for Minimization," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 2080–2086, 2004.

- [29] J. Margarit, L. Teres, and F. Serra-Graells, "A Sub-μW Fully Tunable CMOS DPS for Uncooled Infrared Fast Imaging," *IEEE Trans. Circuits Syst. I*, vol. 56, no. 5, pp. 987–996, May 2009.

# LIST OF FIGURES

| 1  | FPN-compensated digital I/O imager architecture. Practical examples of raw imaging under no compensation (c) and in pivel EPN corrected convicition (b). Posice |          |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|    | ing under no compensation (a) and in-pixel FPN-corrected acquisition (b). Basic imager operation scheme (c). Figure not in scale.                               | 20       |

| 2  | Simplified layout (a) and cross-section (b) of the MWIR VPD PbSe detector after                                                                                 | 20       |

| 2  | being post-processed on top of the CMOS wafer                                                                                                                   | 20       |

| 3  | Experimental response of the integrated VPD PbSe photoconductor at 300K in                                                                                      | 20       |

| 9  |                                                                                                                                                                 | 21       |

| 4  | Digital pixel sensor circuit circuitry (a) and global operational chronogram (b).                                                                               | _1       |

| •  |                                                                                                                                                                 | 21       |

| 5  | Detailed in-pixel DAC schematic for offset and gain programming, and non-over-                                                                                  |          |

|    |                                                                                                                                                                 | 22       |

| 6  | Detailed in-pixel integrate-and-fire ADC schematic with CDS                                                                                                     | 22       |

| 7  | Microscope photograph of the VPD PbSe post-processed wafer with sapphire pro-                                                                                   |          |

|    | tection (a), FPA detail with (bottom-right) and without (top-left) Au and PbSe                                                                                  |          |

|    | deposited on top (b), and pixel detail before post-processing (c)                                                                                               | 23       |

| 8  | Micrograph of the MWIR imager fabricated in 0.35 $\mu$ m 2P4M CMOS technology                                                                                   |          |

|    | with VPD PbSe post-processing. The ROIC is directly wire bonded to chip-carrier                                                                                 |          |

|    | PCB for 64-pin LCC-like sockets                                                                                                                                 | 23       |

| 9  | Electro-optical validation setup used for imager screening at wafer level. Experi-                                                                              |          |

|    | mental results were obtained utilizing the same blackbody and NI-PXI measurement                                                                                |          |

|    | system                                                                                                                                                          | 24       |

| 10 | Experimental offset (a) and gain (b) tuning curves of 24 DPS cells distributed over                                                                             |          |

|    | the $80 \times 80$ -pixel FPA. Operating conditions are no IR illumination and $d_{gain} = 226$                                                                 |          |

|    | LSB (a), and calibrated $d_{offset}$ to achieve $d_{out} = 512$ LSB at $d_{gain} = 226$ LSB                                                                     | 24       |

| 11 | Suc But                                                                                                                                                         | 24       |

| 11 | Experimental deviations of offset cancellation codes (a) and gain programming slope values (b) of the 6400 DPS cells of the entire FPA                          | 25       |

| 12 |                                                                                                                                                                 | 25<br>25 |

| 13 | Measured image pixel-to-pixel (red), row-to-row (blue) and column-to-column (green)                                                                             | 23       |

| 13 |                                                                                                                                                                 | 26       |

| 14 | Average saturated-pixel read-out values over imager focal plane versus incoming                                                                                 | 20       |

|    | IR irradiance before (red) and after (blue) in-pixel equalization. Offset is calibrated                                                                         |          |

|    | at 480 LSB read-out in order to reach saturation.                                                                                                               | 26       |

| 15 | Experimental NETD statistics at 773 K (a) and 1173 K (b) blackbody temperatures.                                                                                |          |

|    | Noise measurements are averaged for each one of the 49 imagers of an entire wafer.                                                                              | 27       |

| 16 | Measured imager speed performance with mechanical chopper (a) and practical                                                                                     |          |

|    | lighter switch-on sequence example (b)                                                                                                                          | 27       |

| 17 | Sample photograms of hot round plate (a) and flame (b) captured at 1650 fps                                                                                     | 28       |

|    |                                                                                                                                                                 |          |

|    | LIST OF TABLES                                                                                                                                                  |          |

| I  | Typical parameters of the integrated VPD PbSe Photoconductor at room temperature.                                                                               | 29       |

| II | Performance comparison between uncooled IR imagers                                                                                                              | 29       |

Figure 1. FPN-compensated digital I/O imager architecture. Practical examples of raw imaging under no compensation (a) and in-pixel FPN-corrected acquisition (b). Basic imager operation scheme (c). Figure not in scale.

Figure 2. Simplified layout (a) and cross-section (b) of the MWIR VPD PbSe detector after being post-processed on top of the CMOS wafer.

Figure 3. Experimental response of the integrated VPD PbSe photoconductor at 300K in terms of MWIR spectral detectivity (a) and modulation bandwidth (b).

Figure 4. Digital pixel sensor circuit circuitry (a) and global operational chronogram (b). row<sub>in</sub> and row<sub>out</sub> are FPA I/O at row level, as illustrated in Fig. 1.

Figure 5. Detailed in-pixel DAC schematic for offset and gain programming, and non-overlapping clock generator circuit.

Figure 6. Detailed in-pixel integrate-and-fire ADC schematic with CDS.

Figure 7. Microscope photograph of the VPD PbSe post-processed wafer with sapphire protection (a), FPA detail with (bottom-right) and without (top-left) Au and PbSe deposited on top (b), and pixel detail before post-processing (c).

Figure 8. Micrograph of the MWIR imager fabricated in  $0.35~\mu m$  2P4M CMOS technology with VPD PbSe post-processing. The ROIC is directly wire bonded to chip-carrier PCB for 64-pin LCC-like sockets.

Figure 9. Electro-optical validation setup used for imager screening at wafer level. Experimental results were obtained utilizing the same blackbody and NI-PXI measurement system.

Figure 10. Experimental offset (a) and gain (b) tuning curves of 24 DPS cells distributed over the  $80\times80$ -pixel FPA. Operating conditions are no IR illumination and  $d_{\text{gain}}=226$  LSB (a), and calibrated  $d_{\text{offset}}$  to achieve  $d_{\text{out}}=512$  LSB at  $d_{\text{gain}}=226$  LSB (b). Results averaged over 150 frames from the same FPA with  $\bar{\sigma}_{\bar{d}_{\text{out}}}=4$  LSB.

Figure 11. Experimental deviations of offset cancellation codes (a) and gain programming slope values (b) of the 6400 DPS cells of the entire FPA.

Figure 12. Measured image and read-out dispersion before (a) and after (b) in-pixel equalization.

Figure 13. Measured image pixel-to-pixel (red), row-to-row (blue) and column-to-column (green) FPN versus incoming IR irradiance before and after in-pixel equalization.

Figure 14. Average saturated-pixel read-out values over imager focal plane versus incoming IR irradiance before (red) and after (blue) in-pixel equalization. Offset is calibrated at 480 LSB read-out in order to reach saturation.

Figure 15. Experimental NETD statistics at 773 K (a) and 1173 K (b) blackbody temperatures. Noise measurements are averaged for each one of the 49 imagers of an entire wafer.

Figure 16. Measured imager speed performance with mechanical chopper (a) and practical lighter switch-on sequence example (b).

Figure 17. Sample photograms of hot round plate (a) and flame (b) captured at 1650 fps.

$\label{thm:conductor} \text{Table I} \\ \text{Typical parameters of the integrated VPD PbSe Photoconductor } \text{$\operatorname{\text{at room temperature}}$.}$

| Parameter                         | Value             | Units   |

|-----------------------------------|-------------------|---------|

| Array pitch                       | 135               | $\mu$ m |

| Spectral range at -3dB            | 1.7 to 4.3        | $\mu$ m |

| Peak detection wavelength         | 3. <mark>6</mark> | $\mu$ m |

| Peak detectivity                  | $1.9 \times 10^9$ | cm√Hz/W |

| Corner frequency $(f_c)$          | 60                | kHz     |

| NETD at 600K                      | 125               | mK      |

| Dark resistance at $V_{bias}$ =1V | 1±20%             | ΜΩ      |

| Dark current at $V_{bias}$ =1V    | 1±20%             | $\mu$ A |

| Output capacitance                | 200               | fF      |

$\label{thm:collection} \mbox{Table II} \\ \mbox{Performance comparison between uncooled IR imagers.}$

|                                       | Posch et al. [5]    | Dupont et al. [7]     | This work             |

|---------------------------------------|---------------------|-----------------------|-----------------------|

| CMOS                                  | $0.35\mu\mathrm{m}$ | $0.18 \mu \mathrm{m}$ | $0.35 \mu \mathrm{m}$ |

| technology                            | 2P4M                | 1P6M                  | 2P4M                  |

|                                       |                     |                       | MWIR                  |

| IR sensing                            | LWIR a-Si           | LWIR a-Si             | VPD PbSe              |

| technology                            | $\mu$ bolometers    | $\mu$ bolometers      | photocon-             |

|                                       | ·                   |                       | ductor                |

| Pixel array                           | 64×64               | 640×480               | 80×80                 |

| Pixel pitch                           | $50\mu\mathrm{m}$   | $17\mu\mathrm{m}$     | $135\mu\mathrm{m}$    |

| Fill factor                           | 69%                 | N.A.                  | 60%                   |

| Max. frame rate                       | 30fps               | 60fps                 | 2000fps               |

| Pixel output                          | Digital<br>AER      | Analog                | Digital<br>10bit      |

| Built-in-pixel<br>FPN<br>cancellation | None                | Offset only           | Offset and<br>Gain    |

| NETD $	imes	au_{	ext{imager}}$        | N.A.                | 400mK×ms<br>at 300K   | 55mK×ms<br>at 600K    |

| Supply voltage                        | 3.3V                | 4V                    | 3.3V                  |

| Static power consumption              | <1µW                | <1µW                  | <1µW                  |