Digital Object Identifier XXX

# arXiv:2006.04627v2 [cs.CR] 15 Jun 2020

# A Survey on Split Manufacturing: Attacks, Defenses, and Challenges

# TIAGO D. PEREZ, SAMUEL PAGLIARINI

Tallinn University of Technology (TalTech)

Department of Computer Systems

Centre for Hardware Security

Tallinn, Estonia

(e-mails: {tiago.perez,samuel.pagliarini}@taltech.ee)

Corresponding author: T. D. Perez (e-mail: tiago.perez@taltech.ee).

This work was supported by the European Union through the European Social Fund in the context of the project âĂIJICT programmeâĂİ.

### **ABSTRACT**

In today's integrated circuit (IC) ecosystem, owning a foundry is not economically viable, and therefore most IC design houses are now working under a fabless business model. In order to overcome security concerns associated with the outsorcing of IC fabrication, the Split Manufacturing technique was proposed. In Split Manufacturing, the Front End of Line (FEOL) layers (transistors and lower metal layers) are fabricated at an untrusted high-end foundry, while the Back End of Line (BEOL) layers (higher metal layers) are manufactured at a trusted low-end foundry. This approach hides the BEOL connections from the untrusted foundry, thus preventing overproduction and piracy threats. However, many works demonstrate that BEOL connections can be derived by exploiting layout characteristics that are introduced by heuristics employed in typical floorplanning, placement, and routing algorithms. Since straightforward Split Manufacturing may not afford a desirable security level, many authors propose defense techniques to be used along with Split Manufacturing. In our survey, we present a detailed overview of the technique, the many types of attacks towards Split Manufacturing, as well as possible defense techniques described in the literature. For the attacks, we present a concise discussion on the different threat models and assumptions, while for the defenses we classify the studies into three categories: proximity perturbation, wire lifting, and layout obfuscation. The main outcome of our survey is to highlight the discrepancy between many studies some claim netlists can be reconstructed with near perfect precision, while others claim marginal success in retrieving BEOL connections. Finally, we also discuss future trends and challenges inherent to Split Manufacturing, including the fundamental difficulty of evaluating the efficiency of the technique.

**INDEX TERMS** Hardware Security, Hardware Trojans, Integrated Circuits, IP Theft, Reverse Engineering, Split Manufacturing

### I. INTRODUCTION

Counterfeiting and intellectual property (IP) infringement are growing problems in several industries, including the electronics sector. In Europe, for instance, seizures of counterfeit electronics products increased by almost 30% when comparing the 2014-2016 to the 2011-2013 period [1]. Legitimate electronics companies reported about \$100 billion in sales losses every year because of counterfeiting [2].

As electronic systems are being increasingly deployed in critical infrastructure, counterfeit and maliciously modified integrated circuits (ICs) have become a major concern. The globalized nature of the IC supply chain contributes to the problem as we lack the means to assess the trustworthiness

of the design and fabrication of ICs. It is conceivable – if not likely – that a fault in a low-quality counterfeit IC (or even a maliciously modified IC) will effectively disrupt critical infrastructure with grave consequences. Therefore, hardware security has gained more attention in the past decades, emerging as a relevant research topic.

As the IC supply chain has became more globalized, ensuring the integrity and trustworthiness of ICs becomes more challenging [3]. When a modern IC is conceived, the probability that all involved parties are trusted is, in practice, close to zero. The process of conceiving an IC can be broken down into three major steps: design, manufacturing, and validation. *Designing* an IC involves arranging blocks and

FIGURE 1. Taxidermy of counterfeit electronics (adapted from [3]).

their interconnections. Some blocks are in-house developed, while some are third-party IPs. Finally, a layout is generated by instantiating libraries that might also be in-house developed or provided by third parties. The resulting layout is then sent to a foundry for *manufacturing*. The process of *validation* requires test for physical defects as well as verification of packaged parts for correct functionality. Both test and packaging facilities may be untrusted, as these efforts are often offshored. Thus, in order to produce an IC, sensitive information almost inevitably is exposed to untrusted parties. Today's reality is that ICs are vulnerable to many hardware-based threats, including insertion of hardware trojans, IP piracy, IC overbuilding, reverse engineering, side-channel attacks, and counterfeiting.

Hardware trojans are malicious modifications to an IC, where attackers insert circuitry (or modify the existing logic) for their own malicious purposes. This type of attack is (typically) mounted during manufacturing, as the foundry holds the entire layout and can easily identify critical locations for trojan insertion. Third-party IPs can also contain trojans/backdoors that may contain hidden functionalities, and which can be used to access restricted parts of the design and/or expose data that would otherwise be unknown to the adversary.

IP piracy and IC overbuilding are, essentially, illegal ownership claims of different degrees. As said before, during designing an IC, third-party and in-house developed IPs are utilized. The untrusted foundry (or a rogue employee of it) can copy one of those IPs without the owner's authorization. Similarly, malicious foundries can manufacture a surplus of ICs (overbuilding) without the owner's knowledge, and sell these parts in the grey market.

Reversing engineering of ICs has been extensively demonstrated in the specialized literature [4]. An attacker can identify the technology node and underlying components (memory, analog, and standard cells), from which a gatelevel netlist can be extracted and even a high-level abstraction can be inferred [5]. Reverse engineering can be effortlessly executed during manufacturing, as the foundry holds the entire layout and most likely promptly recognizes some of the IP as well. After fabrication, when ICs are already packaged and in the field, reverse engineering is more laborious but can

still be executed by a knowledgeable adversary.

According to [3], counterfeit components are classified into seven distinct categories, as illustrated in Fig. 1. Recycled, remarked, out-of-spec/defective, and forged documentation are intrinsic after-market problems, where products are offered by parties other than the original component manufacturer or authorized vendors. These cases are highlighted in red. On the other hand, overproducing, cloning, and tampering are problems faced during the designing and/or fabrication of ICs. For this reason, in this paper, we will focus on these threats. It is important to realise that these threats could be avoided if a trusted fabrication scheme was in place. However, the escalating cost and complexity of semiconductor manufacturing on advanced technologies made owning an advanced foundry unfeasible for design houses which now have the tendency to adopt the fabless business model [6]. Consequentially, outsourcing of the manufacturing exposes their entire layout to untrusted foundries, leaving their designs vulnerable to malicious attacks.

While many *ad hoc* techniques have been proposed to individually combat these threats, very few solutions directly address the lack of trust in the fabrication process. Split Manufacturing stands out from other techniques as it promotes a hybrid solution between trusted and untrusted fabrication. The technique was first pitched to DARPA circa 2006 in a white paper authored by Carnegie Mellon and Stanford universities. Later, it was picked by IARPA which then launched the Trusted IC program [7] that successfully stewarded much of the research in the area and led to this survey.

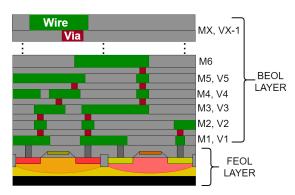

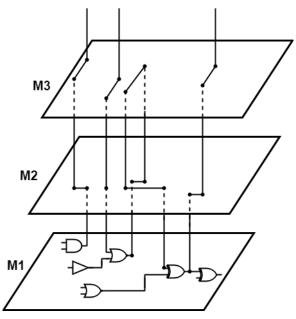

In Split Manufacturing, the key concept is to *split* the circuit in two distinct parts before manufacturing, one containing the transistors and some routing wires, and the other containing the remaining routing wires. These parts are then fabricated in different foundries. The anatomy of an IC is illustrated in Fig. 2 (adapted from [8]), containing two set of layers, the bottom layer where the transistors are built, called Front end of the Line (FEOL), and the top layer where the metal layers are built for routing purposes, called Back end of Line (BEOL). In Split Manufacturing, the FEOL is first manufactured in a high-end foundry, and later the BEOL is stacked on top of it by a second (and possibly low-end)

FIGURE 2. Anatomy of an integrated circuit (adapted from [8]).

foundry. This process requires electrical, mechanical, and/or optical alignment techniques to ensure the connections between them. Additionally, FEOL and BEOL technologies have to be compliant with each other [9] regarding the rules for metal/via dimensions where the split is to be performed. The split can be performed at the lowest metal layer (M1) or at higher layers, for which trade-offs are established between attained security and overheads. If the BEOL and FEOL technologies are vastly different from one another, Split Manufacturing may incur heavy overheads.

In this work, the focus is on the Split Manufacturing technique. As described above, Split Manufacturing can tackle threats that occur during the fabrication. Its avoids overproduction, reverse engineering (to some extent) and unwanted modifications, limiting the capability of attackers. In Section II, we provide a background and more in-depth explanation of the technique. We address security threats in Section II, demonstrating the potential vulnerabilities found in split circuits and describing the state-of-the-art attacks proposed until the present day. In Section IV, the security of split circuits is discussed, showing how it can be improved using enhancement techniques. Future trends and lessons learnt are discussed in Section V. Finally, our conclusions are presented in Section VI.

### II. SPLIT MANUFACTURING: BACKGROUND

As mentioned before, in order to have access to advanced technologies, many design companies have to outsource their IC manufacturing to untrusted high-end foundries. Protecting their designs against threats that may occur during manufacturing is a concern. Designs can be protected by applying the Split Manufacturing technique, thus combating all threats highlighted in Fig. 2.

Split Manufacturing protects a design by hiding sensitive data from the untrusted foundry. This is achieved by splitting the IC into two parts before manufacturing, a horizontal cut that breaks the circuit into one part containing the transistors and some (local) routing wires, and another containing only routing wires. These parts are termed FEOL and BEOL.

As the FEOL and the BEOL of an IC are built sequentially, first FEOL and then BEOL, this characteristic enables the

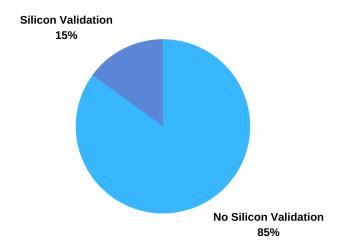

Split Manufacturing technique. Since the FEOL contains the transistors and possibly a few of the lowest ultra-thin metal layers – the most complex parts of an CMOS process [10] –, it is logical to seek to use a high-end foundry for its manufacturing, even if said foundry is not trusted. Completing the IC can then be done in a trusted low-end foundry, where the BEOL is stacked on top of the FEOL. Split Manufacturing was successfully demonstrated in [9], [11], [12], where designs were manufactured with ~0% of faults, and are reported to present a performance overhead of about 5%. Therefore, the technique is, in principle, feasible and available for design companies to make use of, such that they can utilize advanced foundries without fully exposing their layouts during manufacturing.

However, there are many caveats to Split Manufacturing. The technique can be successfully applied only if the technologies used to build the FEOL and BEOL are "compatible". In theory, a layout can be split at any layer if the chosen layer presents a good interface between FEOL and BEOL. However, since advanced technologies utilize the dual-damascene fabrication process, the layout can only be split on metal layers [13], thus, the FEOL cannot terminate in a via. The dual-damascene process is characterized by patterning the vias and trenches in such a way that the metal deposition fills both at the same time, i.e., via-metal pairs (e.g., V1 and M2) must mandatorily be built by the same foundry.

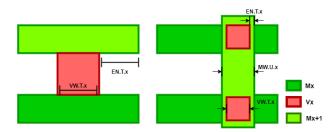

Two technologies are said to be compatible with each other if there is a way for a BEOL via to land on the FEOL uppermost layer while respecting all design rule checks (DRCs) of both technologies. DRCs are used to guarantee the manufacturability and functionality of an IC, and are defined with respected to the characteristics of the materials utilized and to tolerance ranges of the manufacturing processes (e.g., polishing, patterning, and deposition). These rules encompass minimum enclosure, width, spacing, and density checks. Modern technologies have several options for via shapes and as long as one via shape is valid, the technologies are compatible for Split Manufacturing purposes. However, in practice, to keep the overhead of the technique under control, an array of via shapes must be feasible, thus providing the physical synthesis with a rich selection for both power and signal routing. According to [9], compatibility between two technologies can be generalized by enclosure rules as in Eq. 1, where MW.U.x is the minimum width of Mx on untrusted foundry, VW.T.x is the minimum width of Vx on trusted foundry and EN.T.x is the minimum enclosure on trusted foundry. As illustrated in Figure 3, the minimum enclosure width, Mx.EX.Vx, must be compatible between the two foundries. In modern technologies, Eq. 1 is no longer sufficient as it does not capture the intricate rules for vias and line endings (enclosure from 1 side, 2 sides, 3 sides, Tshaped/hammerheads, etc.).

$$MW.U.x \ge VW.T.x + (2EN.T.x) \tag{1}$$

FIGURE 3. Compatibility rules between FEOL and BEOL (adapted from [9]).

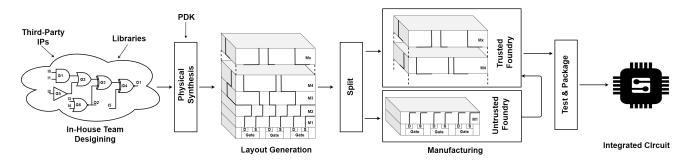

Split Manufacturing also presents challenges on the design flow front, which is illustrated in Fig. 4. An in-house team designs the circuit, from RTL to layout. Most likely, the layout contains IPs obtained from third parties. Depending on the metal layer where the layout is to be split, it may affect existing IP. Logic and memory IP may use higher metal layers – memories typically require 4 to 5 metal layers, while standard cells typically require 2 metal layers –, limiting where the split can be done. Standard cells and memories have to be re-designed if they use metal layers that will be split, a grave challenge that may render Split Manufacturing significantly harder to execute.

Still referring to Fig. 4, the FEOL and BEOL are generated using a hybrid process design kit (PDK), and then later split to be manufactured. After splitting the layout correctly, the FEOL is first manufactured in a high-end foundry, and later the BEOL is stacked on top of it by a second (and possibly low-end) foundry.

Even by splitting the layout, it is often argued that the FEOL exposes enough information to be exploited. Attacks towards the FEOL can effectively retrieve the BEOL connections by making educated guesses. The efficiency of the guessing process is inherently linked to the threat model assumed, which determines the information the attacker possesses to begin with. The literature describes two distinct threat models:

- Threat model I: an attacker located at the untrusted foundry holds the FEOL layout and wants to retrieve the BEOL connections.

- Threat model II: an attacker located at the untrusted foundry holds the entire gate-level netlist that is assumed to be provided by a malicious observer. The attacker here still holds the FEOL layout and wants to retrieve the BEOL connections. [14].

It is important to emphasize that the second threat model completely nullifies the security introduced by Split Manufacturing. Possessing the gate-level netlist makes reverse engineering the layout trivial, as if the attacker held the entire layout, not only the FEOL. Assuming the attacker has knowledge about the netlist challenges the integrity of the design company itself. It could be argued that this vulnerability is so severe that Split Manufacturing virtually stops making sense. For this reason, threat model I is the focus in this work. However, as our goal is to present a comprehensive survey,

related works that use threat model II will be covered as well.

Assuming threat model I, an attacker already knowing all the layers that make up the FEOL, is now interested in retrieving the BEOL connections to recreate the full design (or as close as possible). The commonly used assumption is that attackers are powerful and work within the untrusted foundry in some capacity. Thus, the attackers have deep understanding about the technology. Extracting the (still incomplete) gate-level netlist from a layout is, therefore, a trivial task for the attacker.

Many approaches to retrieve the BEOL connectivity have been proposed, several of which are termed *proximity attacks* [8], [15], [16]. Since EDA tools focus on optimizing power, performance, and area (PPA), the solution found by a placement algorithm (that uses heuristics internally) tends to place connected cells close to one another as this will, in turn, reduce area, wirelength, and delay. Therefore, finding the correct missing connections between FEOL and BEOL can be done by assessing input and output pins that are in proximity (thus, the name proximity attack). The more input and output pins to connect, the higher is the probability to make a wrong connectivity guess. Thus, a higher level of security is achieved by splitting the circuit at the lowest metal layer possible.

As a promising technique to enhance the security of ICs in this era of fabless chip design, Split Manufacturing still faces some enormous challenges:

Logistical challenge: Split Manufacturing is not presently incorporated into the IC supply chain. Finding foundries with compliant technologies that are willing to work with each other is not trivial.

Technological challenge: even within compliant technologies, non-negligible overheads can be introduced if they are vastly different<sup>1</sup>. In the worst case scenario, it can make routing impossible. Thus, this fact narrows down the technology choices available and feasibility of certain layers as candidates for splitting.

Security challenge: the attained security of straightforward Split Manufacturing is still under debate. Attacks towards the FEOL can be effective, where the hidden connections can be retrieved.

For the purpose of this survey, we categorize related works in the literature as attacks and defenses. In *attacks*, authors propose new attack models or modifications of existing attacks in order to improve their effectiveness. In *defenses*, authors propose new techniques to use together with Split Manufacturing in order to improve its security level.

### III. ATTACKS ON SPLIT MANUFACTURING

The Split Manufacturing technique was developed to protect ICs against threats related to manufacturing in potentially untrusted foundries. In practical terms, to split the layout means to hide some connections from the untrusted foundry.

<sup>&</sup>lt;sup>1</sup>For a thorough discussion and silicon results on BEOL-related overheads, please refer to [17].

FIGURE 4. Split Manufacturing Design Flow.

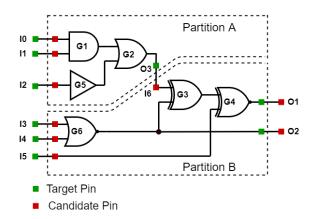

FIGURE 5. Example of a partitioned circuit.

The security provided by Split Manufacturing is based on the fact that the attacker in the FEOL foundry cannot infer the missing BEOL connections. This assumption, however, was challenged by several works where authors proposed attack approaches that can potentially retrieve the missing connections with varying degrees of success. In the text that follows, we present works that proposed Split Manufacturing attacks. These attacks are discussed in chronological order as compiled in Tab. 1. For each studied attack, we report the related threat model, attack type, novelty, and benchmark circuits used in experiments.

The first reported attack is by Jeyavijayan *et al.* and is described in [8]. In this work, the authors assume that naive Split Manufacturing (i.e., splitting a layout without care for the connections) is inherently insecure. They introduced the concept of proximity attacks that exploits "vulnerabilities" introduced by EDA design tools. Since EDA tools focus on optimizing for PPA, the solution found by a placement algorithm tends to place logically connected cells close to one another so they become physically connected during routing. Therefore, the distance between output-input pairs can be used as a metric to recover the missing BEOL connections.

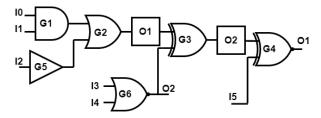

Designs are commonly partitioned during physical implementation, i.e., separated into small logical blocks with few connections between them. That way, the designer have total control of the floorplaning regarding the blocks placement.

This approach also allows for blocks to be implemented separately and later integrated, creating a sense of parallelism in the design flow which can reduce the overall time required for physical synthesis. Consider as an example the circuit illustrated in Fig. 5 that is partitioned into partition A and B. Consider a target output pin  $P_{x,A,out}$  and its corresponding candidate input pin  $P_{x,B,in}$ . During placement, the EDA tool will attempt to place the pin  $P_{x,A,out}$  as close as possible to  $P_{x,B,in}$ , possibly closer than any other pin in partition B. Using this insight, an attacker may recover the missing connections in the FEOL layout, performing then a proximity attack. The authors argue that their proposed attack flow is successful due to being able to leverage the following "hints" provided by the EDA tools:

Hint 1 - Input-Output Relationship: partition input pins are connected either to another partition output pin or to an input port of the IC (i.e., input to input connections are excluded from the search space).

Hint 2 - Unique Inputs per Partition: input-output pins between partitions are connected by only one net. If a single partition output pin feeds more than one input pin, the fan-in and fan-out nodes are usually placed within the partitions (i.e., one-to-many connections are ruled out from the search space).

Hint 3 - Combinational Loops: in general, only very specific structures are allowed to utilize combinational loops (e.g., ring oscillators). These structures are very easy to identify. In most cases, random logic does not contain combinational loops (i.e., connections that would lead to combinational loops can be excluded from the search space).

An attacker can correctly connect a target pin to a candidate pin by identifying the closest pin from a list of possible candidates. The list of possible candidates is created by observing the hints mentioned above. A possible candidate pin is an unassigned output pin of another partition and an unassigned input port of the design. Then, a minimum distance metric is used to connect the pins based on the previously discussed heuristic behavior of EDA tools.

In Algorithm 1, we describe the proximity attack detailed in [8]. The input to the algorithm is the FEOL layout, from which the information about unassigned input-output ports

can be derived. The algorithm does not describe the specifics of how to derive a netlist from a layout. However, the complexity of this task is rather straightforward. It is assumed that the attacker possesses information about both the PDK and the standard cell library. In many cases, the untrusted foundry is the actual provider of both<sup>2</sup>. From there, a layout in GDSII or OASIS format can be easily reverted to a netlist by any custom design EDA tool.

### **Algorithm 1:** Proximity attack

Input: FEOL layers

Output: Netlist with BEOL connections

- 1 Reverse engineer FEOL layers and obtain partitions;

- while Unassigned partition pins or ports exist do

- 3 | Select arbitrary unassigned pin/port as a targetPin;

- 4 ListOfCandPins = BuildCandPinsList(targetPin);

- 5 Select candPin from ListOfCandPins that is closest to

- targetPin;

- 6 Connect targetPin and candPin;

- 7 Update netlist;

- 8 Return: netlist

- 9 BuildCandPinsList(targetPin)

Input: targetPin  $P_{X,i,in}$

Output: CandPins for targetPin

10 CandPins = Unassigned output pins of other partitions +

unassigned input ports of the design;

11 for each  $Pin_J \in CandPins$  do

if CombinationalLoop(targetPin,  $Pin_J$ ) then

CandPins -=  $Pin_J$ ;

14 Return: CandPins

12

From the gate-level netlist, the algorithm chooses an arbitrary *TargetPin* from the unassigned partition input pins and output ports, creates a list of possible *CandidatePins*, and then connects the *TargetPin* to the closest pin in this list. After each connection, the netlist is updated. This procedure is repeated until all unassigned ports are connected. When the procedure is over, the attacker obtains the possible missing BEOL connections. If all guesses were correct, the original design has been recovered and Split Manufacturing has been defeated.

Algorithm 1 was originally applied to the ISCAS'85 [23] suite of benchmark circuits. These circuits were selected and published to help in comparing automatic test pattern generation (ATPG) tools. Due to the small size of these circuits, they may not be the best option to assess the effectiveness of Split Manufacturing. The authors reported an effectiveness of 96% of Correct Connection Rate (CCR) for the c17 circuit (smallest circuit in the ISCAS'85 suite with only 6 gates), demonstrating that the algorithm is capable of retrieving the missing BEOL connections. In Tab. 2, we highlight the best and worst results in terms of CCR.

Jeyavijayan *et al.* [8] were the first to question the security of straightforward Split Manufacturing. Their proximity at-

<sup>2</sup>For the PDK, it is very natural that it is created by the untrusted foundry itself. For standard cell libraries, the cells might be designed by the foundry or by a third-party licensed by the foundry. In either case, the effort to revert a layout to a netlist remains trivial.

FIGURE 6. Representation of the routing for the first 3 metal layers of a simple circuit (adapted from [18]).

tack showed promising results, even if the considered benchmark circuits were rather small in size. This was the starting point for other studies proposing different attacks to Split Manufacturing in an attempt to retrieve the missing BEOL connections. Improvements over the original proximity attack, as well as other attacks, are compiled in Tab. 1.

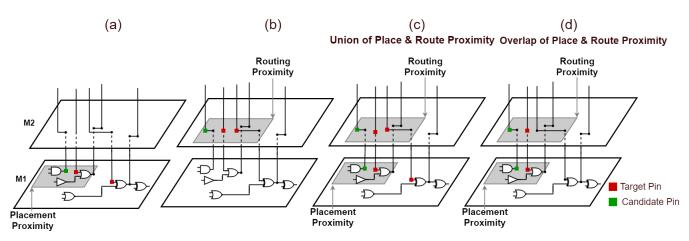

The effectiveness of the proximity attack utilizing distance of unassigned pins alone as metric to find missing BEOL connections was questioned by Magaña *et al.* [18]. The authors proposed to utilize both placement and routing information in augmented proximity attacks. For their results, large-sized circuits from the ISPD-2011 routability-driven placement contest [24] were used. These benchmarks are better representatives of modern circuits as they contain 9 metal layers and up to two million nets in a design. Thus, in an attempt to increase the success rate of the attack for large-sized circuits, they proposed routing-based proximity in conjunction with placement-centric proximity attacks.

A key difference present in [18] is that this work utilizes a different threat model (model II), claiming that the untrusted foundry possesses information about the the entire place & routed netlist (as well as the FEOL layout). This assumption is hard to reason if the attacker's intent was to overproduce the IC or pirate the IP. For these goals, clearly, this assumption is unnecessary. The attacker himself can, if he indeed possesses the netlist, perform his own physical synthesis and generate his own layout. The interest in reverse engineering the BEOL connections of the original design diminishes. Nevertheless, we report on the strategies employed by the authors of [18] since they build on the approach proposed by [8].

Regarding the attacks, the authors of [18] proposed four

TABLE 1. Threat Models, Attacks, and Metrics.

| Work | Year | Threat<br>model | Attack type | Novelty                                                        | Benchmark suite(s) | Largest circuit size (gates) | Avg. circuit<br>size (gates) |

|------|------|-----------------|-------------|----------------------------------------------------------------|--------------------|------------------------------|------------------------------|

| [8]  | 2013 | I               | Proximity   | Attack Based on Proximity                                      | ISCAS'85           | 3.51K                        | 1288                         |

| [18] | 2016 | II              | Proximity   | Placement and routing proximity used in conjunction            | ISPD'11            | 1.29M                        | 951k                         |

| [19] | 2018 | Ī               | Proximity   | Network-Flow-Based with Design<br>Based Hints                  | ISCAS'85 & ITC'99  | 190.21K                      | 9856                         |

| [20] | 2018 | I               | Proximity   | Proximity Attack Based on Machine<br>Learning                  | ISPD'11            | 1.29M                        | 951k                         |

| [21] | 2019 | I               | SAT         | SAT Attack without Proximity Information                       | ISCAS'85 & ITC'99  | 190.21K                      | 9856                         |

| [22] | 2019 | I               | SAT         | SAT attack dynamically adjusted based on proximity information | ISCAS'85 & ITC'99  | 190.21K                      | 9856                         |

TABLE 2. Benchmark Size and Comparison of Attack Results.

| Work | Benchmark   | Attack                       | Split Layer | Size (In Gate Count) | Metric                 | Result |

|------|-------------|------------------------------|-------------|----------------------|------------------------|--------|

| [8]  | c17         | Proximity                    | Not Defined | 6                    | CCR(%)                 | 100    |

| [8]  | c7552       | Proximity                    | Not Defined | 3513                 | CCR(%)                 | 94     |

| [18] | Superblue 1 | Placement Proximity          | M2          | 847k                 | % Match in List        | 12.84  |

| [18] | Superblue 1 | Placement Proximity          | M2          | 847k                 | CCR(%)                 | 5.479  |

| [18] | Superblue 1 | Routing Proximity            | M2          | 847k                 | % Match in List        | 71.08  |

| [18] | Superblue 1 | Routing Proximity            | M2          | 847k                 | CCR(%)                 | 0.651  |

| [18] | Superblue 1 | Overlap (P&R) Proximity      | M2          | 847k                 | % Match in List        | 13.05  |

| [18] | Superblue 1 | Overlap (P&R) Proximity      | M2          | 847k                 | CCR(%)                 | 3.977  |

| [18] | Superblue 1 | Crouting Proximity           | M2          | 847k                 | % Match in List        | 82.08  |

| [18] | Superblue 1 | Crouting Proximity           | M2          | 847k                 | CCR(%)                 | 0.651  |

| [19] | c7552       | Network-flow Based Proximity | Not Defined | 3513                 | CCR(%)                 | 93     |

| [19] | c7552       | Proximity                    | Not Defined | 3513                 | CCR(%)                 | 42     |

| [19] | B18         | Network-flow Based Proximity | Not Defined | 94249                | CCR(%)                 | 17     |

| [19] | B18         | Proximity                    | Not Defined | 94249                | CCR(%)                 | < 1    |

| [20] | Superblue 1 | Proximity                    | M6          | 847k                 | % Match in list        | 33.40  |

| [20] | Superblue 1 | Proximity                    | M6          | 847k                 | CCR(%)                 | 0.76   |

| [20] | Superblue 1 | ML                           | M6          | 847k                 | % Match in list        | 83.12  |

| [20] | Superblue 1 | ML                           | M6          | 847k                 | CCR(%)                 | 1.91   |

| [20] | Superblue 1 | ML-imp                       | M6          | 847k                 | % Match in list        | 74.65  |

| [20] | Superblue 1 | ML-imp                       | M6          | 847k                 | CCR(%)                 | 2.11   |

| [20] | Superblue 1 | ML-imp                       | M4          | 847k                 | % Match in list        | 75.45  |

| [20] | Superblue 1 | ML-imp                       | M4          | 847k                 | CCR(%)                 | 2.58   |

| [21] | c7552       | SAT Attack                   | Not Defined | 3513                 | Logical Equivalence(%) | 100    |

| [21] | B18         | SAT Attack                   | Not Defined | 94249                | Logical Equivalence(%) | 100    |

| [22] | c7552       | Improved SAT Attack          | Not Defined | 3513                 | Logical Equivalence(%) | 100    |

| [22] | B18         | Improved SAT Attack          | Not Defined | 94249                | Logical Equivalence(%) | 100    |

different techniques to identify a small search neighborhood for each pin. The goal is to create a neighborhood that is small enough to make further pruning feasible, and therefore increase the likelihood of including the matching pins. The techniques are called *placement proximity*, *routing proximity*, *crouting proximity* and *overlap of placement and routing proximity*, and are described in the text that follows. The circuit illustrated in Fig. 6 is the example (before the split) that will guide the discussion on these four techniques.

Placement proximity exploits the placement information of cells. Each split wire is taken from the pin location of the corresponding standard cell that is connected to it. A search neighborhood is defined as a square region centered around the corresponding pin with an area equal to the average areas of the bounding boxes (BB) in a typical design. The authors argue that it can also be measured based on BBs of the nonsplit wires in the design under attack, under the assumption

that the number of wires that remain in the FEOL is also very large in practice. Let us consider the circuit illustrated in Fig. 6 as an example. If the split is done at M2, the search area defined using the placement proximity would be as illustrated in Fig. 7 (a). Note that the layer at which the layout is split does not affect the search area defined by the placement proximity.

Routing proximity exploits the routing information. First, for each split wire, pins are identified as the point where the wire is actually cut at the split layer, i.e., the via location. Next, a square area centered around those pins is defined. The size of the square area is defined based on the average BBs of the pins on that layer in the design. This procedure for identification results in different neighborhood sizes according to the split layer location, i.e., the search radius adapts to the routing resources of each layer. A search area defined using routing proximity is illustrated in Fig. 7 (b).

Crouting proximity takes into account routing congestion by exploiting the union of placement and routing proximity. The search area for each pin is defined in such way that the ratio of number of pins to the search area is equal across all the pins in the split layer. Thus, if a pin is located at a high routing congestion area, the search area will be expanded until the pin density in the new search area reaches a target value or the search area grows to four times its starting value. The starting value is set according to the split layer, set as the average of numbers of pins which fall within a BB. A search area defined using crouting proximity is illustrated in Fig. 7 (c).

The last strategy proposed by [18] also combines placement and routing information. It is referred to as *Overlap of placement and routing proximities*. The concept here is to include a subset of pins identified by the placement proximity list which have their corresponding pins included in the routing proximity list. According to the author, intuitively, the overlap then identifies a subset of pins which may be more likely to point towards the direction of the matching pin. A search area defined using the overlap of placement and routing proximities is illustrated in Fig. 7 (d).

Magaña et al. [18] assessed each strategy using the benchmark circuit *superblue1*. Different split layers were also considered. In Tab. 2, we compiled the results for split layer M2. By comparing the results, it becomes clear that no strategy was able to recover 100% of the missing BEOL connections. The best result was only 5.479% of CCR. This is in heavy contrast with the findings of [8]. However, as we previously noted, the circuit sizes differ by orders of magnitude.

According to the authors of [18], proximity alone is in no way sufficient to reverse engineer the FEOL. However, proximity attacks have merit as they can be used to narrow down the list of candidates to a significantly smaller size. Using crouting proximity, in 82.08% of the cases, the search area defined contained the matched pin in the list of candidates. The authors also present results for a circuit split at M8. We opt not to show these results in Tab. 2. Using the circuit superblue1 as an example, the number of unassigned pins when the circuit is split at M8 is only 1.2% of the pins when split at M2. Therefore, the small number of unassigned pins to be connected overshadows the large circuit used for their experiments. It must also be emphasized that splitting a circuit in such higher layers is rather impractical since M8 tends to be a very thick metal reserved for power distribution in typical 10-metal stacks. There is very little value in hiding a power distribution network from an adversary that wants to pirate an IP. Once again, we opt not to show this result in our comparisons.

A network-flow based attack model towards flattened designs was proposed by Wang et. al [19]. The authors argue that the proximity attack originally proposed by [8] utilizes hints that can be used only by hierarchical designs, and that

modern designs are often flattened <sup>3</sup>. Based on the original proximity attack, they propose a proximity attack utilizing five hints: physical proximity, acyclic combinational logic circuit, load capacitance constraint, directionality of dangling wires, and timing constraint. Note that the first tow hints are already described by [8] and [18]. The three novel hints are described below:

Load Capacitance Constraint: gates can drive a limited load to honor slew constraints. Typically, maximum load capacitance is constrained and has a maximum value defined by the PDK and/or the standard cell characterization boundaries. Hence, an attacker will consider only connections that will not violate load capacitance constraints.

Directionality of Dangling Wires: routing engines tend to route wires from a source to a sink node along the direction of the sink node. Therefore, the directionality of remaining dangling wires at lower metal layers may indicate the direction of their destination cell with a high degree of certainty<sup>4</sup>. An attacker can disregard connections in the other directions.

Timing Constraint: connections that create timing paths that violate timing constraints can be excluded. An attacker, through an educated guess of the clock period, can determine a conservative timing constraint and exclude any connections that would lead to slower paths.

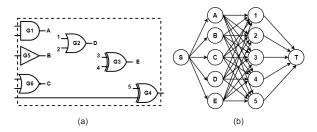

The network-flow based attacked framework proposed by Yang et al. considers two hints proposed by [8] plus the aforementioned hints to create a directed graph G = (V, E), where V is a set of vertices and E is a set of edges. The set (V) is composed by the set of vertices corresponding to the output pins  $V_o$ , and a set corresponding to the input pins  $(V_i)$ , the source vertex (S), and the target vertex (T). The set Econsists of  $E_{So}$ , edges from S to every output pin vertex,  $E_{oi}$ , edges from output pin vertices to input pin vertices, and  $E_{iT}$ , which includes edges from every input vertex to the target vertex. An example of this kind of representation is shown in Fig. 8, where (a) is the circuit with missing connections and (b) is the network-flow representation. The detailed problem formulation is omitted from this work. To find the connections, a min-cost network-flow problem is solved, where the decision variables are the flow  $x_{i,j}$  going through each edge  $(i,j) \in E$ . The authors utilize the Edmons-karp algorithm [25] to solve this problem. Complexity of the algorithm alone is given by  $O(VE^2)$ , however, in the worst case it is requried to run the algorithm V times; thus, the run-time of the complete network attack is given by  $O(V^2E^2)$  in the worst case.

<sup>3</sup>We highlight that best practices in circuit design have changed over the years. Hierarchical design was heavily utilized for many years, but it lost favor due to the difficulty in performing reasonable timing budgeting between the many blocks of a system. Thus, flattened designs are often used to facilitate timing closure.

<sup>4</sup>Metals usually have preferred directions that alternate along the stack (i.e., if M1 is vertical, then M2 is horizontal). Therefore, this hint becomes more effective if the attacker can observe more than one routing layer of the FEOL

FIGURE 7. Multiple strategies for pin/connectivity search areas according to [18].

FIGURE 8. (a) Circuit with missing connections. (b) Network-flow model for inferring the missing connections. (Adapted from [19]).

The network-flow approach was applied to ISCAS'85 and ITC'99 benchmark circuits. For comparison, teh authors applied both the original proximity attack and the network-flow attack to flattened designs. As shown in Tab. 2, their network-flow proximity attack outperformed the original attack in terms of CCR. However, despite the evident improvement, the attack could only retrieve 17% of the missing BEOL connections for a medium sized circuit (b18 from the ITC'99 suite).

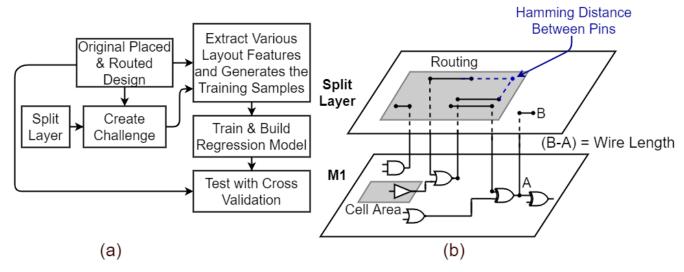

A Machine Learning (ML) framework was used by Zhang *et al.* [20] in an attempt to improve the attack proposed in [18]. The same setup as previously discussed was utilized. However, more layout features were incorporated in their ML formulation, including placement, routing, cell sizes, and cell pin types.

A high-level overview of their modeling framework is shown in Fig. 9 (a). First, they create a challenge instance from the entire layout and only FEOL view. Next, for each virtual pin (point where a net is broken on the split layer), layout information is collected, including placement, routing, cell areas, and cell pin as illustrated in Fig. 9 (b). Using this information, samples are generated which are fed into the ML training process. Each sample carries information of a pair of virtual pins which may or may not be matched. Classifiers then are built by the ML framework using training samples. After training and building the regression model, cross validation is used for evaluation which ensures validation of

the model is done on data samples which were not used for training. Their framework faces scaling issues when applied to lower split metal layers. An improved ML framework is then proposed as well, denoted by ML-imp, to solve the scaling issues.

For their experiments, Zhang et al. [20] utilize the ISPD'2011 benchmark suite. They compare results from their previous work [18] with their ML and ML-imp frameworks. However, they do not show results for lower split metal layers (e.g., M2). Instead, results are provided for M8, M6, and M4 splits. As pointed out before, utilizing higher layers for the split effectively shrinks the otherwise large circuits used in their experiments. A drastic reduction of unassigned pins is expected for such higher layers as higher metal layers are used often for power routing, not for signal routing. Results for the *superblue1* circuit are shown in Tab. 2. Regarding recovering missing BEOL connections, ML and ML-imp could only retrieve around 2%, therefore not showing a huge improvement over their previous work. However, search list area accuracy showed significantly better results when compared to their prior work. A caveat worth mentioning is that the proposed machine learning framework needs the entire layout during its modeling phase. This characteristic may, in an extreme case, nullify the applicability for an attacker that only holds the FEOL layout and cannot produce training samples from other sources.

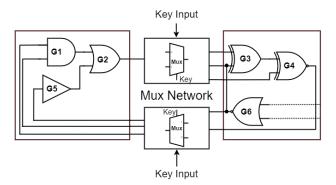

Attacks using proximity information as a metric are not the only solution to recover missing BEOL connections. An effective methodology to apply a Boolean satisfiability based strategy is proposed by Chen *et al.* [21]. The authors claim that their attack methodology does not need (or depend on) any proximity information, or even any other insights into the nature of EDA tools utilized in the design process. The key insight in their work is to model the interconnect network as key-controlled multiplexers (MUX). Initially, all combinations of signal connections between the FEOL partitions are allowed, as illustrated in Fig. 10. First, a MUX network is created in order to connect all missing paths in the circuit.

FIGURE 9. (a) Machine Learning Modeling by Zhang et al. [20]. (b) Few Exmples of Layout Features.

This MUX network leads to potential cyclic paths, thus, there is a possibility to generate many combinational loops during the attack process corresponding to incorrect key guesses. Therefore, constraints on the key values are generated in order to avoid activating the cyclic paths. The attack can be summarized in 4 steps: *identification of all cyclic paths, generation of cycle constraints, cycle constraints optimizations,* and finally, *SAT attack*. The authors utilize a SAT solverbased attack method derived from CycSat [26]. The SAT attack algorithm has as input the FEOL circuit with MUX network and a packaged IC that serves as an oracle. The algorithm outputs keys to be used in the MUXes such that correct BEOL connections are made.

In reality, [21] presents a different interpretation of Threat model I since the attacker is assumed to possess a functional IC. This IC would then have to be available in the open market for teh attacker to be able to purchase it. This characteristic severely narrows down the applicability of this SAT attack. For instance, ICs designed for space or military use will not be freely available, thus an oracle may not be known to the attacker.

Experimental results presented by [21] utilize ISCAS'85 and ITC'99 benchmark circuits. It has been shown that their attack could recover a logically correct netlist for all the studied circuits. However, there is a small clarification to be made that relates to what is a logically correct circuit. In Tab. 2, two of those results are shown. For seven of the studied benchmarks (c1908, c2670, c5315, c7552, b14, b15, b17), the connections recovered are identical to the BEOL connections. For the remaining benchmarks, the recovered connections are not identical but logically equivalent to the original circuit. In practice, the logically equivalent circuit may present performance deviations from the original design. Matching the performance of the original design can be done by re-executing place and route using the logically equivalent gate-level netlist. Depending on the attack goal, it

FIGURE 10. MUX network for a bipartitioned FEOL circuit (Adapted from [21]).

is possible that the attacker had already planned to re-execute the physical synthesis flow again (say, to resell the IP in a different form or shape). An attack that guarantees 100% of logic equivalence of the recovered netlist is powerful enough, allowing attackers to copy and modify split layouts.

In order to increase the efficiency and capacity of the SAT attack proposed in [21], the authors propose two improvements in [22]. First, the size of the key-controlled interconnect network that models the possible BEOL connections is reduced. Second, after the MUX network is inserted into the FEOL circuit, the number of combinational cycles it induces in the design for incorrect key guesses should also be reduced. Proximity information is then exploited to achieve the proposed improvements. The improved SAT attack method which exploits proximity information showed significant reduction in the attack time and increase in the capacity. Same as in [21], the circuits tested were 100% recovered, as shown in Tab. 2.

TABLE 3. Split Manufacturing Defenses.

| Work | Year         | Threat Model | Category                           | Defense                                                 | Metrics                                                                    | <b>Defense Overheads Presented</b>                                |

|------|--------------|--------------|------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|

| [8]  | 2013         | I            | Proximity Perturbation             | Pin Swapping                                            | Hamming<br>Distance                                                        | _*                                                                |

| [14] | 2013<br>2014 | II<br>I      | Wire Lifting<br>Layout Obfuscation | Wire Lifting                                            | k-Distance                                                                 | Power, Area, Delay and Wire-Length<br>Performance, Power and Area |

| [11] | 2014         | I            | ·                                  | Layout Obfuscation for SRAMs and Analog IPs             | -                                                                          | Performance, Power and Area                                       |

| [27] | 2014         | I            | Layout Obfuscation                 | Obfuscation Techniques                                  | Neighbor<br>Connectedness<br>and Entropy                                   | Performance and Area                                              |

| [28] | 2015         | I            | Layout Obfuscation                 | Automatic Obfus-<br>cation Cell Layout                  | Neighbor<br>Connectedness<br>and Entropy                                   | Performance, Power and Area                                       |

| [29] | 2015         | I            | Layout Obfuscation                 | Obfuscated<br>Built-in Self-<br>Authentication          | Obfuscation Connection                                                     | Number of Nets                                                    |

| [18] | 2016         | I            | Wire Lifting                       | Artificial Blockage<br>Insertion                        | Number of Pins                                                             | _*                                                                |

| [30] | 2016         | I            | Wire Lifting                       | Net Partition, Cell<br>Hidden and Pin<br>Shaken         | -                                                                          | _*                                                                |

| [15] | 2017         | I            | Proximity Perturbation             | Routing Perturba-<br>tion                               | Hamming<br>Distance                                                        | Performance and Wire-Length                                       |

| [31] | 2017         | I            | Wire Lifting                       | Secure Routing<br>Perturbation for<br>Manufacturability | Hamming<br>Distance                                                        | Performance and Wire-Length                                       |

| [32] | 2017         | I            | Proximity Perturbation             | placement-centric<br>Techniques                         | CCR                                                                        | Performance, Power and Area                                       |

| [33] | 2017         | II           | Proximity Perturbation             | Gate Swapping and<br>Wire Lifting                       | Effective Mapped<br>Set Ratio and Av-<br>erage Mapped Set<br>Pruning Ratio | Wire-Length                                                       |

| [34] | 2018         | I            | Wire Lifting                       | Concerted Wire Lifting                                  | Hamming<br>Distance                                                        | Performance, Power and Area                                       |

| [19] | 2018         | I            | Proximity Perturbation             | Secure Driven Placement Perturbation                    | Hamming<br>Distance                                                        | Power and Wire-Length                                             |

| [35] | 2018         | I            | Proximity Perturbation             | placement<br>and routing<br>perturbation                | Hamming<br>Distance                                                        | Performance, Power and Area                                       |

| [36] | 2019         | I            | Layout Obfuscation                 | Isomorphic replacement for Cell Obfuscation             | Isomorphic<br>Entropy                                                      | _*                                                                |

| [37] | 2019         | II           | Layout Obfuscation                 | Dummy Cell and<br>Wire Insertion                        | k-security                                                                 | Area and Wire-Length                                              |

<sup>\*</sup> Authors do not present any discussion regarding overhead.

### IV. SPLIT MANUFACTURING DEFENSES

Attacks toward Split Manufacturing showed promising results, as described in the previous section. A malicious attacker has the real potential to recover the missing BEOL connections. If the missing connections are successfully recovered, the security introduced by applying the technique is nullified. Therefore, straightforward Split Manufacturing is questioned by several works. Several authors propose defense techniques that augment the technique, i.e., techniques that, when used together with Split Manufacturing, do increase the achieved security against attacks. In Tab. 3, we compile a comprehensive list of defense techniques found in the literature. Each defense technique utilizes a different metric and Threat model, depending upon the type of attack they are trying to overcome. Since many of the studied defense

techniques often introduce heavy PPA overheads, Tab. 4 also shows if the studied work assessed overheads and which ones were addressed.

In the text that follows, the many defense techniques are divided into categories, namely Proximity Perturbation (i.e., change the location of cells or pins), Wire Lifting (i.e., move routing wires to upper layers), and Layout Obfuscation (i.e., hide the circuit structure). We present the categories in this exact order. For some techniques, it is worth mentioning that overlaps do exist and that techniques could be categorized differently. Thus, this categorization is our interpretation of the state of the art and may not be definitive. Furthermore, the boundaries between categories are not strict. For example, a technique may perform a layout modification that promotes proximity perturbation and leads to (indirect) wire lifting.

### A. PROXIMITY PERTURBATION

Attacks toward split circuits are generally based on leveraging proximity information. The first category of defenses, Proximity Perturbation, addresses this hint left by the EDA tools. The goal of the techniques within this category is to promote changes in the circuit such that the proximity information between the FEOL pins is less evident. Therefore, the success rate of the proximity attacks is decreased.

In [8], the authors propose pin swapping to overcome proximity attacks. Rearranging the partition pins can alter their distance in such a way that the attacker is deceived. As an example, if the pins  $P_{G3,B,in}$  and  $P_{G6,A,in}$  (Fig. 5) are swapped, the proximity attack will incorrectly guess the connection between  $P_{G2,A,out}$  and  $P_{G3,B,in}$ . Thus, a sufficient number of pins have to be swapped in order to create a netlist that is significantly different from the original netlist (based on some sort of metric for similarity). In [8], Hamming distance is proposed as a way to quantify the difference between the outputs of the original netlist and the modified netlist. The authors argue that the optimum netlist is created when the Hamming distance is 50%. Since the best rearrangement for N pins of partitions might take N!computations (rather computationally expensive), pair-wise swapping of pins is considered in [8]. Pair-wise swapping of pins results in  $O(N^2)$  computations.

The modified netlist is created based on a series of rules. Similarly to the proximity attack, a list of candidates pins to be swapped is created before the actual swap is applied. Since not every pin can be swapped, a candidate pin to be swapped should:

- be an output pin of the partition where the target pin resides

- not be connected to the partition where the candidate pin resides

- not form a combinational loop

Using the above constraints, a candidate pin is selected. The target pin also needs to be chosen carefully. In [8], IC testing principles [38] and hints from the original proximity attack are used to choose the target pin. The swapping procedure is described in Algorithm 2, where TestMetric is a metric based on IC testing principles described in details in [8]. The proposed defense technique is validated using ISCAS'85 circuits and the original proximity attack. For the smallest circuit, c17, it took only one swap to achieve 50% of Hamming Distance. For the largest studied circuit, c7552, it took 49 swaps. These results are summarized in Tab. 4.

As demonstrated in [8], rearranging the partition pins can thwart proximity attacks. However, according to Chen *et al.* [33], pin swapping at partition level has limited efficacy. They demonstrated that an attacker holding the FEOL layout as well as the nestlist can insert hardware trojans even when the defense approach of [8] is applied. It must be highlighted that [33] assumes threat model II, which we have previously argued that has the potential to nullify the vast majority of defenses towards split circuits. Thus, they proposed a defense

to counter the threat from hardware trojans. Their defense incorporates the global wire-length information, with the goal to hide the gates from their candidate locations, and as result decreasing the effective mapped set ratio (EMSR). The EMSR metric is an attempt to quantify the ratio of real gates location of a given mapping during a simulated annealing-based attack. This defense consists of two steps, first a greedy gate swapping defense [19], and second, a measurement of the security elevation in terms of EMSR. The technique is evaluated using ISCAS'85 benchmarks circuits and the EMSR metric to quantify the defense effectiveness. The results are shown in Tab. 4.

Following the same principle of increasing the Hamming Distance, Wang et al. [15] propose a routing perturbation based defense. The optimum Hamming distance is sought to be achieved by layer elevation, routing detours, and wire decoys, while test principles are used to drive the perturbation choices. Layer elevation is essentially a wire lifting technique: without changing the choice of split metal layer, wires are forced to route using higher metal layers, thus being lifted from the FEOL to the BEOL. Intentional routing detours are a way to increase the distance between disconnected pins of the FEOL. If done properly, disconnected pins will not be the closest to each other, deceiving the proximity attack. In some cases, routing detours will increase the distance between disconnected pins, however, they still remain the closest to each other. In this scenario, wire decoys can be drawn near disconnected pins, in such a way that decoys are now the closest and will instead be picked as the ideal candidate pin.

The perturbations proposed in [15] can incur heavy overheads, and, for this reason, wires to be perturbed are chosen by utilizing IC test principles. In [15], fault observability, as defined in SCOAP [39], is used as a surrogate metric for this task. The technique is evaluated using ISCAS'85 and ITC'99 benchmark circuits. For all studied circuits, the Hamming distance increased by an average of 27% at a cost of only 2.9% wire length overhead (WLO), on average. The results for the largest and smallest studied circuits are shown in Tab. 4.

Sengupta *et al.* [32] take a different direction from other works. They utilize an information-theoretic metric to increase the resilience of a layout against proximity attacks. As demonstrated in [32], mutual information (MI) can be used to quantify the amount of information revealed by the connectivity distance between cells. Mutual information is calculated by taking into account the cells connectivity D, if they are connected or not, and their Manhattan distance X, described by Eq. 2, where  $H[\cdot]$  is the entropy. The distribution of the variable X for a given layout is determined pairwise for all gates, allowing a straightforward computation of I(X;D). Thus, layouts with the lowest mutual information, i.e., the correlation between cell connectivity and their distance is low, are more resilient against proximity attacks.

$$MI = I(X; D) = H[X] - H[X/D]$$

(2)

**Algorithm 2:** Fault analysis-based swapping of pins to thwart proximity attack (adapted from [8]).

```

Input: Partitions

Output: List of target and swapping pins

1 ListofTargetPins = \emptyset;

2 ListofSwappingPins = \emptyset;

3 ListofUntouchedPins = All partition pins and I/O ports;

4 while Untouched output partitions pins or input ports exist do

for UntouchedPin do

5

SwappingPins =

BuildSwappingPinsList(UntouchedPin); for

SwappingPin \in SwappingPins do

Compute

8

TestMetric(UntouchedPin, SwappingPin);

Find the TargetPin and SwappingPin with the Highest

10

TestMetric from its SwappingPins;

ListofTargetPins + = TargetPins;

11

List of Swapping Pins + = Swapping Pins;

12

ListofUntouchedPins - = TargetPins;

13

LisofUntouchedPins -= SwappingPin;

14

Swap TargetPin and SwappingPin;

15

Update netlist;

17 Return: ListofTargetPins and ListofswappingPins;

BuildSwappingPinList(TargetPin);

Input: TargetPinP_{x,i,out}

Output: SwappingPins for TagetPin

for Pin_J \in SwappingPins do

if CombinationalLoop(TargetPin, Pin_J) then

SwappingPins-=Pin_J;

21 Return: SwappingPins;

```

In order to minimize the information "leaked" from mutual information, [32] applies cell placement randomization and three other techniques: g-color, g-type1, and g-type2. Randomizing the cell placement can achieve the desired low mutual information; however, the PPA overhead incurred is excessive. Minimizing mutual information without excessive PPA overhead can be achieved by the other techniques. From a graph representation of the circuit, graph coloring can be used to hide connectivity information, where gates of the same color must not be connected. Thus, the resulting colored netlist is then partitioned by clustering all cells of same color together. During cell placement, the cells with the same color will be confined within their respective clusters. According to [32], these constraints naturally mitigate the information leakage to a great extent. The g-color technique utilizes only the graph coloring as described above. The other two, g-type1 and g-type2, take into account the type of the gate when creating clusters. The g-type1 approach clusters gates only by their functionality, while g-type2 utilizes functionality and the number of inputs for clustering. The authors assessed their techniques utilizing ISCAS'85 and MNCN benchmark suites. Results for the smallest and largest circuits are shown in Tab. 4.

Similar to the pin swapping technique proposed in [8], Wang *et al.* [19] propose a placement-based defense with the same objective of deceiving a proximity attack by perturb-

ing proximity information. Differently from pin swapping, their placement-based defense considers the incurred wirelength overhead as a metric. This technique is based on changing gate locations such that the proximity hint is no longer effective. Their algorithm consists of two phases, one to select which gates to be perturbed and a second phase where the selected gates are (re)placed. Gate selection is done by extracting a set of trees using two techniques, BEOLdriven and logic-ware extraction. The first approach selects all gate trees that contain any metal wires in the FEOL, i.e., connections that are not hidden from the attacker. The second approach takes into account the wire-length impact and the gate tree impact on the overall security. After extracting the set of trees, the placement perturbation is done in one of two ways: physical-driven or logic-driven. For each extracted tree, the physical-driven perturbation changes the location of gates using a Pareto optimization approach. Also, each solution is evaluated by its wire-length overhead and a perturbation metric that discerns the placement difference from the original layout. According to [19], geometricbased difference alone may be insufficient to enhance the split circuit security. Thus, a logic-driven perturbation is performed with a weighted logical difference (WLD) metric, which encourages perturbation solutions with large logical difference from its neighbors. The authors assessed their techniques combining the gate selection and perturbation as BEOL+Physical, Logic+Physical and Logic+Logic, using ISCAS'85 and ITC'99 circuit benchmarks. Results for the smallest and largest circuits considered are shown in Tab. 4.

A considerably different approach is proposed by Patnaik et al. [35], whereas netlist modifications are promoted (instead of placement/routing modifications during physical synthesis). The goal is to modify the netlist of a design in order to insert (partial) randomization. According to [35], this approach helps to retain the misleading modifications throughout any regular design flow, thereby obtaining more resilient FEOL layouts where the netlist changes are later "corrected" in the BEOL. This methodology is implemented as an extension to commercial EDA tools with custom inhouse scripts. The process goes as follows: first, the netlist is randomized. Second, the modified netlist is place and routed. Lastly, the true functionality is restored by re-routing in the BEOL. For the netlist randomization, pairs of drivers and their sinks are randomly selected and swapped. This is done in such way to avoid combinational loops that may be introduced by swapping. The modified netlist then is place and routed, utilizing a 'do not touch'<sup>5</sup> setting for the swapped drivers/sinks to avoid logic restructuring/removal of the related nets. Finally, the true connectivity is restored in the BEOL with the help of correction cells [35] that resemble switch boxes. The technique is evaluated using ISCAS'85 circuits, and the results for the largest and smallest circuit are shown in Tab. 4.

<sup>&</sup>lt;sup>5</sup>This terminology is used in IC design to mean that a specific cell or family of cells should not be optimized, i.e., not to be touched.

TABLE 4. Results for Defense Techniques based on Proximity Perturbation.

| Work | Attack<br>Type | Benchmark | Defense Technique               | Defense Metric     | Defense Overhead       | Split<br>Layer | Result with-<br>out Defense | Result with<br>Defense |

|------|----------------|-----------|---------------------------------|--------------------|------------------------|----------------|-----------------------------|------------------------|

| [8]  | Proximity      | c17       | -                               | Hamming Distance   | 1 Swap for 50%<br>HD   | _*             | 100% CCR                    | 78% CCR                |

| [8]  | Proximity      | c7552     | -                               | Hamming Distance   | 49 Swaps for 50%<br>HD | _*             | 94% CCR                     | 91% CCR                |

| [33] | Proximity      | c432      | Modifed Greedy Gate<br>Swapping | EMSR               | 75% of WLO             | _*             | 90% EMSR                    | 25% EMSR               |

| [33] | Proximity      | c432      | Modifed Greedy Gate<br>Swapping | EMSR               | 300% of WLO            | _*             | 78% EMSR                    | 10% EMSR               |

| [15] | Proximity      | c432      | - ''                            | Hamming Distance   | 3.1% WLO for 46.1% HD  | _*             | 92.4% CCR                   | 78.8% CCR              |

| [15] | Proximity      | c432      | -                               | Hamming Distance   | 4.1% WLO for 31.7% HD  | _*             | 62.8% CCR                   | 37.9% CCR              |

| [32] | Proximity      | c432      | Random                          | Mutual Information | < 10% PPA              | M1             | 17% CCR                     | < 1% CCR               |

| [32] | Proximity      | c432      | g-color                         | Mutual Information | < 10% PPA              | M1             | 17% CCR                     | 2% CCR                 |

| [32] | Proximity      | c432      | g-type1                         | Mutual Information | < 10% PPA              | M1             | 17% CCR                     | 6% CCR                 |

| [32] | Proximity      | c432      | g-type2                         | Mutual Information | < 10% PPA              | M1             | 17% CCR                     | 4.5% CCR               |

| [32] | Proximity      | c7552     | Random                          | Mutual Information | < 10% PPA              | M1             | 13% CCR                     | < 1% CCR               |

| [32] | Proximity      | c7552     | g-color                         | Mutual Information | < 10% PPA              | M1             | 13% CCR                     | 2% CCR                 |

| [32] | Proximity      | c7552     | g-type1                         | Mutual Information | < 10% PPA              | M1             | 13% CCR                     | 4% CCR                 |

| [32] | Proximity      | c7552     | g-type2                         | Mutual Information | < 10% PPA              | M1             | 13% CCR                     | 3% CCR                 |

| [19] | SAT            | c432      | BEOL+Physical                   | Perturbation       | 4.5% WLO               | _*             | 58% CCR                     | 56% CCR                |

| [19] | SAT            | c432      | Logic+Physical                  | Perturbation       | 5.57% WLO              | _*             | 58% CCR                     | 58% CCR                |

| [19] | SAT            | c432      | Logic+Logic                     | WLD                | 1.68% WLO              | _*             | 58% CCR                     | 52% CCR                |

| [19] | SAT            | b18       | BEOL+Physical                   | Perturbation       | 8.06% WLO              | -*             | 15% CCR                     | 14% CCR                |

| [19] | SAT            | b18       | Logic+Physical                  | Perturbation       | 1.70% WLO              | -*             | 15% CCR                     | 17% CCR                |

| [19] | SAT            | b18       | Logic+Logic                     | WLD                | 0.61% WLO              | -*             | 15% CCR                     | 16% CCR                |

| [35] | Proximity      | c432      | Netlist Randomiza-<br>tion      | Hamming Distance   | < 10% PPA overall      | _*             | 92.4% CCR                   | 94.3% CCR              |

| [35] | Proximity      | c7552     | Netlist Randomiza-<br>tion      | Hamming Distance   | < 10% PPA overall      | _*             | 94.4% CCR                   | 94.3% CCR              |

<sup>\*</sup> Split layer not specified by the authors.

### B. WIRE LIFTING

Hiding routing information from untrusted foundries is the main objective of the Split Manufacturing technique. Since attacks mainly rely on hints left by EDA tools to recover the missing BEOL connections, the amount of hidden information is related to the circuit performance – splitting the circuits at low metal layers increases the security level. Following the same idea, wire lifting proposes 'lifting' wires from the FEOL layer to the BEOL. That is, changing the routing to split metal layers has the potential to increase the security level.

Wire lifting was first presented by Imerson *et al.* [14] where Split Manufacturing is considered as a 3D IC implementation [40]. For the sake of argument, we will continue to refer to this technique as Split Manufacturing, even if the notion of untrusted FEOL vs. trusted BEOL is shifted. This type of 3D implementation consists of two or more independently manufactured ICs, where each IC represents a tier that is vertically integrated on top of each other. Connections between the tiers are done using vertical metal pillars, referred to as through-silicon vias (TSVs). In [14], a 3D implementation consisting of two tiers is used for their experiments. The bottom tier containing the transistors and some routing wires (akin to the FEOL), and the top tier, containing only routing wires (akin to the BEOL). Regarding the manufacturing of these 3D ICs, the bottom tier is built in

a high-end untrusted foundry, and the top tier is built in an also untrusted foundry (not necessarily high-end, however).

In [14], threat model II is used, i.e., the adversary is assumed to possess the entire netlist. The problem is formulated as the attacker being the FEOL foundry, which in turn also possesses the so called 'unlifted netlist' extracted from the FEOL layout. By utilizing a graph to represent the circuits as previously described, the attacker seeks a bijective mapping of gates of the unlifted netlist to gates in the complete netlist. According to [14], if the attacker can distinguish any gate between the two netlists, the split circuit does not provide any security. A security notion is provided by the authors, based on existing multiple mapping between gates in the unlifted and complete netlists. Referred to as k-security, this metric qualifies that gates across the design are indistinguishable from at least k-1 other gates. Thus, a defender wants to lift wires in a way to guarantee the higher k - securitypossible. Two procedures are proposed to achieve this goal, one utilizing a greedy heuristic targeted at small circuits (due to scalability issues), and another procedure that utilizes partitioning to solve those issues. For their experimental study, they have utilized the ISCAS'85 benchmark suite and a DES crypto circuit with approximated 35000 gates. The results are shown in Tab. 5, where k = 1 is the original circuit and k = 48 is achieved when all the wires are lifted. It is worth to mention that, besides the notion of the security

TABLE 5. Results for Defense Techniques based on Wire Lifting.

| Work | Attack<br>Type | Benchmark   | Defense Technique                                  | Defense Metric   | Defense Overhead | Split<br>Layer | Result with-<br>out Defense | Result with<br>Defense |

|------|----------------|-------------|----------------------------------------------------|------------------|------------------|----------------|-----------------------------|------------------------|

| [14] | SAT            | c432        | Wire Lifting                                       | k-security       | 477% of WLO      | _*             | k=1                         | k=48                   |

| [18] | Proximity      | Superblue 1 | Routing Blockage In-<br>sertion                    | E[LS]            | Not Presented    | M4             | 1.51                        | 1.77                   |

| [18] | Proximity      | Superblue 1 | Routing Blockage Insertion                         | FOM              | Not Presented    | M4             | 1222.8                      | 1433                   |

| [34] | Proximity      | c432        | Concerted Lifting                                  | Hamming Distance | 7.7% of Area     | Average**      | 23.4                        | 45.9                   |

| [34] | Proximity      | c432        | Concerted Lifting                                  | CCR              | 13.2% of Power   | Average**      | 92.4                        | 0                      |

| [34] | Proximity      | c7552       | Concerted Lifting                                  | Hamming Distance | 16.7% of Area    | Average**      | 1.6                         | 25.7                   |

| [34] | Proximity      | c7552       | Concerted Lifting                                  | CCR              | 9.3% of Power    | Average**      | 97.8                        | 0                      |

| [31] | Proximity      | c2670       | CMP-Friendly                                       | Hamming Distance | 3.4% of WLO      | _*             | 14.5%                       | 20.4%                  |