Received January 14, 2020, accepted January 31, 2020, date of publication February 4, 2020, date of current version February 11, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.2971574

# A Survey of Swarm Intelligence Techniques in VLSI Routing Problems

XIAOHUA CHEN<sup>®</sup><sup>1</sup>, GENGGENG LIU<sup>®</sup><sup>1</sup>, (Member, IEEE), NAIXUE XIONG<sup>®</sup><sup>2</sup>, (Senior Member, IEEE), YARU SU<sup>®</sup><sup>1</sup>, AND GUOLONG CHEN<sup>®</sup><sup>1</sup>

<sup>1</sup>College of Mathematics and Computer Science, Fuzhou University, Fuzhou 350116, China

Corresponding author: Genggeng Liu (liugenggeng@fzu.edu.cn)

This work was supported in part by the National Natural Science Foundation of China under Grant 61877010 and Grant 11501114, and in part by the Natural Science Foundation of Fujian Province, China, under Grant 2019J01243.

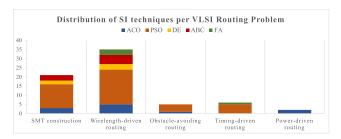

**ABSTRACT** Routing is a complex and critical stage in the physical design of Very Large Scale Integration (VLSI), minimizing interconnect length and delay to optimize overall chip performance. With the rapid development of modern technology, VLSI routing faces enormous challenges such as large delay, high congestion, and high-power consumption. As a rising optimization method, Swarm Intelligence (SI) inspired from collective intelligence behaviors through cooperation or interaction with the environment provides effectiveness and robustness for solving NP-hard problems. Many researchers have consequently used SI techniques to solve routing-related problems in VLSI. This paper reviews the application of several SI techniques to the VLSI routing filed. Firstly, five commonly used SI techniques and related models, and three classic routing problems are described: Steiner tree construction, global routing and detailed routing. Then an overview of the current state of this field is given according to the above categories, and the survey offers informative discussions from five aspects: 1) Steiner minimum tree construction; 2) wirelength-driven routing; 3) obstacle-avoiding routing; 4) timing-driven routing; 5) power-driven routing. Finally, under three new technology models: X-architecture, multiple dynamic supply voltage and via-pillar, the future development trends are pointed as follows: 1) suggesting suitable SI techniques to specific routing problems for advanced technology models; 2) exploring new and available SI techniques that have not yet been applied to VLSI routing.

**INDEX TERMS** Particle swarm optimization, swarm intelligence, routing, very large scale integration, Steiner tree construction.

| LIST OF ABBREVIATION                                                |                                         | DE   | Differential Evolution                     |  |

|---------------------------------------------------------------------|-----------------------------------------|------|--------------------------------------------|--|

| ABC                                                                 | Artificial Bee Colony                   | DPSO | Discrete Particle Swarm Optimization       |  |

| ACO                                                                 | Ant Colony Optimization                 | EDA  | Electronics Design Automation              |  |

| BPSO                                                                | Binary Particle Swarm Optimization      | FA   | Firefly Algorithm                          |  |

| CCPSO                                                               | Cooperatively Coevolving Particle Swarm | GA   | Genetic Algorithm                          |  |

|                                                                     | Optimization                            | GRC  | Global Routing Cell                        |  |

| CLPSO                                                               | Comprehensive Learning Particle Swarm   | GRG  | Global Routing Graph                       |  |

|                                                                     | Optimization                            | HST  | Hexagonal Steiner Tree                     |  |

| <b>CMOS</b>                                                         | Complementary Metal-Oxide-Semiconductor | HTS  | Hybrid Transformation Strategy             |  |

| CPSO                                                                | Cooperative Particle Swarm Optimization | IC   | Integrated Circuit                         |  |

| DDE                                                                 | Discrete Differential Evolution         | ISPD | International Symposium on Physical Design |  |

|                                                                     |                                         | ILP  | Integer Linear Programming                 |  |

|                                                                     |                                         | MDSV | Multiple Dynamic Supply Voltage            |  |

| The associate editor coordinating the review of this manuscript and |                                         | MST  | Minimal Spanning Tree                      |  |

| approving it for publication was Sudipta Roy <sup>©</sup> .         |                                         | MSV  | Multiple Supply Voltage                    |  |

<sup>&</sup>lt;sup>2</sup>College of Intelligence and Computing, Tianjin University, Tianjin 300350, China

OAOSMT Obstacle-Avoiding Octagonal Steiner

Minimum Tree

OARSMT Obstacle-Avoiding Rectilinear Steiner

Minimum Tree

OST Octagonal Steiner Tree

OSMT Octagonal Steiner Minimum Tree PSO Particle Swarm Optimization

QPSO Quantum Particle Swarm Optimization

RST Rectilinear Steiner Tree

RSMT Rectilinear Steiner Minimum Tree

SI Swarm Intelligence SMT Steiner Minimum Tree

SPSO Standard Particle Swarm Optimization

TSV Through Silicon Vias UFS Union-Find Sets

VLSI Very Large Scale Integration

#### I. INTRODUCTION

Very Large Scale Integration (VLSI) is a process of forming an Integrated Circuit (IC) by incorporating thousands of transistors into a single chip [1]. As integration continues to increase, more and more features, even a complete system can be integrated into a single chip. As the pillar of information industry, the design and manufacturing of VLSI are playing an increasingly important role in driving economic development, deepening industrial structure and lifestyle changes.

Physical design is the most time-consuming step in the design process of IC, and it is also one of the most important and active research field in VLSI computer-aided design technology. Due to its complexity, the whole process of physical design is often divided into partition, floorplanning, placement and routing. Routing plays a key role in VLSI physical design as it determines the specific shape and layout of interconnect, impacting performance, power and manufacturability, which is traditionally divided into the two steps of global and detailed routing. Global routing needs to connect all nets with all capacity constraints satisfied. While detailed routing takes a global routing solution with a small number of capacity violations (overflows), or none at all. And under the premise of ensuring spacing constraints and more sophisticated design rules, detailed routing completes the assignment of wires within the routing area.

With the rapid development of IC, these characteristics are presented: the feature size is getting smaller and smaller, the chip area is getting larger and larger, the power supply voltage is getting lower and lower, and the number of routing metal layers is also increasing. Traditional routing algorithms, which operate in isolated layout regions-channels or switch-boxes, are usually assumed to be routed on the premise of a small number of metal layers, making it difficult to accommodate more metal layers. Gradually, overthe-cell routing with six or multi-layer routing lead to the adoption of similar graph-theoretical techniques in global and detailed routing, perhaps with different layouts, resource and

delay models [2]. The routing algorithms require a better balance between wirelength minimization and congestion. In general, congestion is optimized by considering constraints such as obstacles, number of vias, and capacitance. However, the continuous reduction of process size and the increase of integration complexity make traditional routing algorithms unable to perform such multi-objective tasks well, and the design of routing algorithms faces new challenges.

Swarm Intelligence (SI) is an important category of optimization technique, which is inspired from simple behaviors and self-organizing interaction among agents like ant colonies foraging, bird flocking, animal herding, bacterial growth, honey bees, fish schooling, and so on [3]. Each SI algorithm has its own unique advantages. The specific behaviors of these animals in solving problems have different help for searching optimal solutions, so the performance of each SI algorithm is different for different problems. But these SI algorithms have one thing in common, that is, each of them has several agents working simultaneously. And experience learning or information sharing or competition among individuals can enable swarm to grow rapidly, improving search efficiency and precision. Therefore, many researchers have started applying various SI algorithms with great promise because of their high computational efficiency, reliability, scalability, self-organizing, longevity and low-cost [4]. In recent years, SI techniques have been widely used on many practical real-world problems in the fields of scheduling [5], production [6], facility control [7], [8], transportation [9] and so on.

The survey has the following four main objectives. First, we give an introduction about key concepts in VLSI routing, such as Minimum Spanning Tree (MST), Steiner tree and related routing issues including global and detailed routing. Second, the applications of some SI techniques in routing problems are listed to provide an overview of the current state of this hot field. Thirdly, we investigate and research some advanced processes, and give a discussion about the construction of routing models and evaluation models that are suitable for such processes. The final important goal is to identify future trends and research directions to better guide subsequent research efforts. This study discussed the contributions which were published in the relevant journals, conference proceedings and theses.

The rest of the paper is organized as follows. The core definitions and related concepts of SI techniques and VLSI routing issues are respectively presented in Sections II and III, so that they are easily linked to the rest of the research in this paper. Then, Section IV focuses on the investigated routing problems using the five SI algorithms to present a current state of the art. Section V provides a discussion of related issues, including multi-layer routing based on X-architecture, global routing in a Multiple Dynamic Supply Voltage (MDSV) chip design environment, and routing problems under the via-pillar process. Section VI clarifies the future trends and opportunities under each type of problems, while Section VII is to make a conclusion for this paper.

TABLE 1. Overview of different types of SI technique.

| Type of<br>SI Technique | Proposal                            | Inspiration                                                                  | Par | ameter Number / Parameters                                                                  | Computational<br>Complexity |

|-------------------------|-------------------------------------|------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------|-----------------------------|

|                         |                                     |                                                                              |     | Population size, $M$                                                                        |                             |

| ACO                     | Dorigo<br>(1992) [11]               | Ant colonies forage for food using pheromone as a mean of chemical messenger | 5   | Number of iterations, $t$                                                                   | -<br>- High<br>-<br>-       |

|                         |                                     |                                                                              |     | Pheromone factor, $\alpha$                                                                  |                             |

|                         |                                     |                                                                              |     | Heuristic factor, $\beta$                                                                   |                             |

|                         |                                     |                                                                              |     | Evaporation rate, $\rho$                                                                    |                             |

|                         | Kennedy and Eberhart<br>(1995) [12] | Social behavior of bird flocking                                             |     | Population size, $M$                                                                        | -<br>-<br>Low               |

|                         |                                     |                                                                              | 7   | Number of iterations, $t$                                                                   |                             |

| PSO                     |                                     |                                                                              |     | Inertia weight, $\omega$                                                                    |                             |

|                         |                                     |                                                                              |     | Acceleration coefficient, $c_1, c_2$                                                        |                             |

|                         |                                     |                                                                              |     | Random numbers with uniform distribution, $r_1$ , $r_2$                                     |                             |

|                         | Storn and Price<br>(1997) [13]      | Genetic evolution of biological populations                                  |     | Population size, $NP$                                                                       | -<br>-<br>Low<br>-          |

|                         |                                     |                                                                              | 7   | Number of iterations, $t$                                                                   |                             |

| DE                      |                                     |                                                                              |     | Scaling factor, F                                                                           |                             |

|                         |                                     |                                                                              |     | Crossover rate, $CR$                                                                        |                             |

|                         |                                     |                                                                              |     | Mutually exclusive integers randomly generated within the range $[1, NP]$ , $r_1, r_2, r_3$ |                             |

|                         | Karaboga<br>(2005) [14]             | Natural foraging behavior of real honey bees                                 |     | Population size, $NP$                                                                       | -<br>-<br>Medium            |

|                         |                                     |                                                                              | 5   | Number of iterations, $t$                                                                   |                             |

| ABC                     |                                     |                                                                              |     | The number of employed foragers, $SN$                                                       |                             |

|                         |                                     |                                                                              |     | The threshold that a employed bee role is transformed into a scout bee, $l$                 |                             |

|                         |                                     |                                                                              |     | A defined number of iterations, $c$                                                         |                             |

|                         | Yang<br>(2008) [15]                 | Behavior of fireflies<br>and their flashing light                            |     | Population size, $M$                                                                        | -<br>-<br>- High<br>-       |

|                         |                                     |                                                                              |     | Number of iterations, $t$                                                                   |                             |

|                         |                                     |                                                                              | 6   | Attractiveness, $\beta_0$                                                                   |                             |

| FA                      |                                     |                                                                              |     | Randomization parameter, $\alpha$                                                           |                             |

|                         |                                     |                                                                              |     | Absorption coefficient, $\gamma$                                                            |                             |

|                         |                                     |                                                                              |     | Random numbers with Gaussian distribution or uniform distribution, $\varepsilon$            |                             |

#### **II. SWARM INTELLIGENCE TECHNIQUES**

A system in which unintelligent entities exhibit collective intelligence behavior through cooperation or interaction with the environment is called *Swarm Intelligence*, having the characteristics of natural distribution and self-organizing characteristics [10]. It can show obvious advantages without the premise of centralized control and providing a global model. Inspired by nature and biology, SI techniques obtain collective intelligence behaviors through two fundamental concepts, *self-organization* and *division of labor*, and are widely used in optimization problems. Many heuristic optimization algorithms are developed on the basis of simulating the behavior of different biological populations.

This section introduces the basic principles and mathematical models of five SI algorithms commonly used in

VLSI routing problems: Ant Colony Optimization (ACO), Particle Swarm Optimization (PSO), Differential Evolution (DE), Artificial Bee Colony (ABC), Firefly Algorithm (FA). Table 1 outlines several important characteristics of these techniques.

## A. ACO

# 1) INSPIRATION AND BASIC IDEAS OF ACO

In the 1990's, ACO was introduced as a nature-inspired method for the solution of various combinatorial optimization problems [11]. The ACO algorithm is inspired by the feeding behavior of real ant colonies in nature. When looking for food, the ants will randomly explore the area near the nest. If an ant finds a source of food, it will evaluate the food

and brings some food back to the nest, leaving a pheromone along the way to guide other ants to find the food source. And the concentration of pheromones may depend on the quantity and quality of the food. Then the pheromone will gradually evaporate. If two ants find the same food at the same time and take different routes to return to the nest, the pheromone smell on the more complicated path will be lighter, and the ant colony will tend to another route closer to find food. Thus, the probability of selecting the path of the ant from the nest is proportional to the concentration of the pheromone on each path, and each passing ant will leave a pheromone on the way to achieve communication between the individuals, forming a positive feedback phenomenon [16]. The diversity of ant colonies and the characteristics of positive feedback make the ACO algorithm both innovative and learning.

#### 2) MATHEMATICAL REPRESENTATION OF ACO

The feasible solution of the problem to be optimized is represented by the ant's walking path, and all the paths of the whole ant colony constitute the solution space of the problem. Artificial ants construct solutions from sequences of solution components taken from a finite set of m available solution components  $C = \{c_{ij}\}$ . And a solution construction starts with an empty partial solution  $s^P = \emptyset$ . Then, at each step, the current partial solution  $s^P$  is extended by adding a feasible solution component from the set  $N(s^P) \in C \setminus s^P$ , which is done probabilistically as represented in Eq. (1) [16].

$$p(c_{ij} \mid s^P) = \frac{\tau_{ij}^{\alpha} \cdot \eta(c_{ij})^{\beta}}{\sum_{c_{il} \in N(s^P)} \tau_{il}^{\alpha} \cdot \eta(c_{il})^{\beta}}, \quad \forall c_{ij} \in N(s^P) \quad (1)$$

where  $\tau_{ij}^{\alpha}$  is the pheromone value associated with component  $c_{ij}$ , and  $\eta(\cdot)$  is a weighting function that assigns a heuristic value to each feasible solution component  $c_{ij} \in N(s^P)$  at each step.  $\alpha$  and  $\beta$  are positive parameters determining the relation between pheromone information and heuristic information.

The pheromone in Eq. (1) through the following pheromone evaporation process to increase the pheromone values associated with good or promising solutions, and decrease those that are associated with bad ones [17].

$$\tau_{ij} \leftarrow \begin{cases} (1 - \rho)\tau_{ij} + \rho \Delta \tau, & \text{if } \tau_{ij} \in s_{ch} \\ (1 - \rho)\tau_{ij}, & \text{otherwise} \end{cases}$$

(2)

where  $\rho \in (0, 1]$  is the evaporation rate. Different versions of ACO algorithms update pheromones in different ways.

# B. PSO

#### 1) INSPIRATION AND BASIC IDEAS OF PSO

PSO was first proposed by Kennedy and Eberhart in 1995 [12]. Its main idea is derived from the study of birds clustering behavior, using the characteristics of bird population attracted by habitat to guide human decision-making process. At the beginning, the flock flies in the air in no specific direction until one bird finds its habitat. Trapped by

the habitat, other companions will be affected by neighboring partners and habitats, and gradually fly to the habitat. In this process, two kinds of crucial information will be fully utilized, namely the experience from the bird itself and its neighboring partners. In the PSO algorithm, each solution of the optimization problem, called "particle", is regarded as a bird in the search space. All particles correspond to all possible solutions in the solution space. Each particle has no weight and volume, and its fitness value is determined by the objective function. The speed of a particle determines the direction and distance of its flight. And the particle completes the search in the solution space by learning form its own experience and the optimal particle in the group. In recent years, many scholars have carried out related research on PSO due to its simple calculation, easy implementation and low control parameters.

## 2) MATHEMATICAL REPRESENTATION OF PSO

In the PSO algorithm, particles dynamically adjust their position information by learning their best individual position and the global best position in the swarm. Consider a minimization problem with D-dimensional search space, assuming that the population size of is M, and the speed and position update formulas of the Standard Particle Swarm Optimization (SPSO) [18] are as follows:

$$V_{ij}^{t+1} = \omega \cdot V_{ij}^{t} + c_1 \cdot r_1 \cdot (P_{ij}^{t} - X_{ij}^{t}) + c_2 \cdot r_2 \cdot (G_j^{t} - X_{ij}^{t})$$

(3)

$$X_{ii}^{t+1} = V_{ii}^{t+1} + X_{ii}^{t} (4)$$

where  $1 \le i \le M$ ,  $1 \le j \le D$ . In Eq. (3),  $\omega$  is the inertia weight to better balance the exploration and exploitation of the algorithm.  $c_1$  and  $c_2$  are acceleration coefficients, which respectively adjust the step size of the particle flying to its personal best position and the global best position.  $r_1$  and  $r_2$  are mutually independent random numbers uniformly distributed in the interval (0,1).  $P_{ij}^t$  and  $G_j^t$  are the best position of the particle i and the global optimal position of the population respectively, satisfying the following formula:

$$P_{i}^{t} = \begin{cases} X_{i}^{t}, & \text{if } f(X_{i}^{t}) < f(P_{i}^{t}) \\ P_{i}^{t-1}, & \text{if } f(X_{i}^{t}) \ge f(P_{i}^{t}) \end{cases}$$

(5)

$$G^{t} = P_{g}^{t}, \quad g = \arg\min_{1 \le i \le M} [f(P_{i}^{t})]$$

(6)

In 1999, Clerc and Kennedy introduced constriction coefficient [19] in the evolution equation, relaxed the speed limit, and thus improved the convergence speed of the algorithm. The speed update formula is as follows:

$$V_{ij}^{t+1} = \chi \cdot (V_{ij}^t + \varphi_1 r_1 (P_{ij}^t - X_{ij}^t) + \varphi_2 r_2 (G_j^t - X_{ij}^t)) \quad (7)$$

where  $\varphi_1$  and  $\varphi_2$  are acceleration coefficients, and  $\chi$  is constriction coefficient satisfying:

$$\chi = \frac{2}{[2 - \varphi - \sqrt{\varphi^2 - 4\varphi}]}, \quad \varphi = \varphi_1 + \varphi_2, \ \varphi > 4$$

However, some dimensions that are close to the optimal solution are likely to be far from the optimal solution

although the particle position is improved after updating. Therefore, a kind of Cooperative Particle Swarm Optimization (CPSO) [20] is proposed to solve this problem. CPSO divides the dimensions of particles into several groups and each group is optimized with a single particle swarm. Then calculate the fitness value after combining the dimensions. Finally, the corresponding update is performed according to the update rules of the SPSO algorithm.

In order to solve the problem that PSO is easily trapped into local optimal when dealing with complex multi-peak problems, Liang *et al.* [21] proposed Comprehensive Learning PSO (CLPSO), in which particles have more learning objects and thus have more potential flight space.

# C. DE

#### 1) INSPIRATION AND BASIC IDEAS OF DE

The DE was proposed by Storn and Price on the basis of evolutionary ideas such as Genetic Algorithm (GA) in 1997 [13]. The essence is a multi-objective (continuous variables) evolutionary algorithm. And it is used for solving the overall optimal solution in multidimensional space. In community of DE, the individual trial solutions which constitute a population are called parameter vectors or genomes [22]. DE generates a population of individuals by encoding with a floating vector, and the optimization process includes mutation, hybridization, and selection operations. The basic idea is described as follows: Starting from a randomly generated initial population, a new individual is generated by summing the vector difference of any two individuals in the population with a third individual, and the fitness value is used to determine whether to retain the old individual. Through continuous evolution, retaining good individuals, and eliminating inferior individuals, DE guides search to the optimal solution.

# 2) MATHEMATICAL REPRESENTATION OF DE

The DE algorithm involves three control parameters, namely population size NP, scaling factor F, and crossover rate CR. The optimization process includes the following three operations.

#### a: MUTATION OPERATION

After initializing the population, DE employs the mutation operation to produce a mutant vector. Reference [23] gives five commonly used variation strategies as follows:

$$V_i^t = X_{r_1}^t + F \cdot (X_{r_2}^t - X_{r_3}^t) \tag{8}$$

$$V_i^t = X_{best}^t + F \cdot (X_{r_1}^t - X_{r_2}^t) \tag{9}$$

$$V_i^t = X_i^t + F \cdot (X_{best}^t - X_i^t) + F \cdot (X_{r_1}^t - X_{r_2}^t)$$

(10)

$$V_i^t = X_{best}^t + F \cdot (X_{r_1}^t - X_{r_2}^t) + F \cdot (X_{r_3}^t - X_{r_4}^t) \quad (11)$$

$$V_i^t = X_{r_1}^t + F \cdot (X_{r_2}^t - X_{r_2}^t) + F \cdot (X_{r_4}^t - X_{r_5}^t)$$

(12)

where  $V_i^t = \{v_{i,1}^t, v_{i,2}^t, \dots, v_{i,D}^t\}$  is mutant vector. The indices  $r_1, r_2, r_3, r_4, r_5$  are mutually exclusive integers randomly generated within the range [1, NP], and these indices are randomly generated once for each mutant vector. The scaling factor F is a positive control parameter for scaling the

difference vector.  $X_{best}^t$  is the best individual vector with the best fitness value in the population at generation t.

# b: CROSSOVER OPERATION

Crossover operation is applied to each pair of the target vector  $X_i^t$  and mutant vector  $V_i^t$  to generate a trial vector:  $U_i^t = \{u_{i1}^t, u_{i2}^t, \dots, u_{iD}^t\}$ . Crossover operation is defined as follows:

$$u_{ij}^{t} = \begin{cases} v_{ij}^{t}, & if \ rand_{j}[0, 1) \leq CR \ or \ j = j_{rand} \\ x_{ij}^{t}, & otherwise \end{cases}$$

(13)

where the crossover rate CR is a user-specified constant within the range [0,1), and controls the fraction of parameter values copied from the mutant vector.

# c: SELECTION OPERATION

Selection operation typically screens individuals based on fitness values. The selection operation can be expressed as follows:

$$X_i^{t+1} = \begin{cases} U_i^t, & \text{if } f(U_i^t) \le f(X_i^t) \\ X_i^t, & \text{otherwise} \end{cases}$$

(14)

#### D. ABC

#### 1) INSPIRATION AND BASIC IDEAS OF ABC

The ABC algorithm was proposed by Karaboga in 2005 [14]. The basic idea is that the bee colony cooperates with each other to complete the process of collecting honey through individual division of labor and information exchange. The minimal search model for bee colony to achieve collective intelligence includes three essential components: food sources, employed bees and unemployed bees, and two behavior patterns: the recruitment to a rich nectar source and the abandonment of a poor source [24]. The employed bees correspond to the collected food sources, store information about a certain food source, and share the information with other bees with a certain probability. The unemployed bees are mainly responsible for finding and mining food sources, and there are two types of unemployed bees, respectively: scouts, searching the environment surrounding the nest for new food sources, and onlookers, waiting in the nest and establishing a food source through the information shared by employed bees. In the beginning, all food sources are discovered by scout bees. Thereafter, the mining of nectar is completed by employed bees and onlooker bees. The sharing of food sources information is realized in the form of a swing dance in the dance area. After finding the food sources and collect their nectar, employed bees return to the nest and express the yield rate of food source through the duration of swing dance. That is, the yield rate is proportional to the likelihood that the food source is selected. Onlooker bees are employed after watching the swing dance and begin searching for the corresponding food source neighborhood and collecting honey. While the employed bee whose food source has been exhausted becomes a scout bee. ABC works through the transformation of three different types of roles to find high-quality honey sources.

#### 2) MATHEMATICAL REPRESENTATION OF ABC

In ABC, the location of food sources represents the possible solutions of the problem, and the amount of nectar in a food source corresponds to the quality (fitness) of the relevant solution. In the basic form, the number of employed bees is equal to the number of food sources (solutions).

Assume that the dimension of the problem is D, the number of food sources is SN, and the position of honey source i is expressed as  $X_i^t = [x_{i1}^t, x_{i2}^t, ..., x_{iD}^t]$ . The initial position of honey source i is randomly generated in the search space according to Eq. (15):

$$x_{ij} = L_j + rand(0, 1) \cdot (U_j - L_j)$$

(15)

where L and U represent the lower limit and upper limit of the search space, respectively.

At the beginning of the search, ABC algorithm utilizes the following expression to generate a new honey source location  $V_i^t = [v_{i1}^t, v_{i2}^t, ..., v_{iD}^t]$  around the honey source i:

$$v_{ij} = x_{ij} + \phi(x_{ij} - x_{kj}) \tag{16}$$

where  $k \in \{1, 2, ..., SN\}$ , and not equal to i. This parameter indicates that the employed bee randomly selects a nectar source other than i from SN nectar sources.  $\phi$  is a random number between [-1,1], which decides the magnitude of the perturbation. When the fitness of the new honey source  $V_i$  is better than  $X_i$ , the greedy selection is adopted to replace  $X_i$  with  $V_i$ , otherwise keep  $X_i$ . Eq. (16) indicates that when the search is close to the optimal solution, the step size will also be adaptively reduced.

After all the employed bees complete the operation of Eq. (16), they fly back to the information exchange area to share the honey source. And an onlooker bee chooses a food source depending on the probability value  $p_i$ , which is associated with food source. And it is calculated by the following expression:

$$p_i = \frac{fit_i}{\sum\limits_{n=1}^{SN} fit_n}$$

(17)

During the search process, if the honey source  $X_i$  has reached a threshold l by a defined number of iterations c and does not find a better food source, the honey source will be abandoned, and the corresponding employed bee will be converted into a scout bee. The scout bee will randomly generate a new food source in the search space to instead  $X_i$ . The above process is described as Eq. (18):

$$X_i^{t+1} = \begin{cases} L + rand(0, 1) \cdot (U - L), & c_i \ge l \\ X_i^t, & c_i < l \end{cases}$$

(18)

#### E. FA

# 1) INSPIRATION AND BASIC IDEAS OF FA

FA is a simulation of the biological characteristics of firefly luminescence in nature. It was proposed by Yang to effectively deal with multi-modal and global optimization problems [15]. The algorithm simulates the search and optimization processes into the attraction and movement of the firefly individuals, and measures the objective function of solving the problem as the position of the individual. In this algorithm, the reason why fireflies attract each other depends on two factors: their own *brightness* and *attractiveness*. The fluorescence brightness emitted by fireflies depends on the target value of their location. The higher the brightness, the better the position, that is the better the target value. Attractiveness is proportional to their brightness and they both decrease as their distance increases. For any two flashing fireflies, the less bright one will move towards the brighter one. If no one is brighter than a particular firefly, it will move randomly.

#### 2) MATHEMATICAL REPRESENTATION OF FA

The FA achieves target optimization through continuous updating of brightness and attractiveness. And the brightness of fireflies with distance r is expressed as follows:

$$I = I_0 e^{-\gamma r} \tag{19}$$

where  $I_0$  is the original light intensity and  $\gamma$  is the light absorption coefficient.

The attractiveness of a firefly is expressed as below:

$$\beta = \beta_0 e^{-\gamma r^2} \tag{20}$$

where  $\beta_0$  is the attractiveness at r = 0.

Firefly i is attracted by firefly i' and the position update formula is as follows:

$$X_i^{t+1} = X_i^t + \beta (X_{i'}^t - X_i^t) + \alpha^t \varepsilon_i^t$$

(21)

where the third term is randomization with  $\alpha^t$  being the randomization parameter, and  $\varepsilon^t_i$  is a vector of random numbers drawn from a Gaussian distribution or uniform distribution at time t. Furthermore, the randomization  $\varepsilon^t_i$  can easily be extended to other distributions such as Lévy flights [15].

#### III. ROUTING PROBLEMS IN VLSI

As the current IC industry continues to advance toward ultra-deep sub-micron processes, the integration of chips is further improved. Since more and more circuit components can be integrated on a single chip with the limitation of storage space and packaging process, the VLSI design approach faces new challenges. Among them, routing is one of the top ten problems that the current physical design needs to solve urgently [25]. In terms of chip size and capacity, the routing problem requires a circuit chip scale of tens of thousands of large modules and millions of small modules, and requires this work to be completed within a reasonable time. In addition, the quality of the routing severely affects other requirements in the design process, including timing and interconnection analysis. In order to reduce the high complexity of the routing process in chip design, the routing is usually divided into two steps: global routing and detailed routing. The global routing is a rough routing process, its function

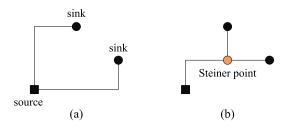

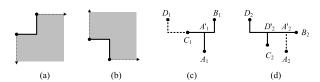

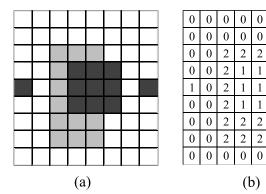

FIGURE 1. A three-pin net connected by (a) a spanning tree and (b) a Steiner tree, respectively.

is to reasonably distribute each part of the nets to be routed to each routing area in the chip, thereby clearly defining the routing problem of each routing area. The detailed routing is to complete the specific routing of each routing area under the guidance of the global routing results. This section gives a list of common subproblems in VLSI routing.

#### A. STEINER TREE

The shortest path problem of two-pin nets is one of the most basic problems in VLSI routing, which looks for the shortest routing path by given the position of the two pins while considering the obstacles. Commonly found strategies are maze routing [26], line probe methods [27], pattern routing [28] and so on. However, in actual routing problems, there are often more than two pins in a net. A common approach to dealing with multi-pin nets is to decompose the multi-terminal net into a set of two-terminal nets, that is, construct an MST with pins as nodes. In order to reduce the length of the routing tree, in addition to original nodes formed by given pins, the final MST can be constructed by introducing additional nodes called Steiner points. As shown in Figure 1(a), a three-pin net connected by spanning tree is given. The Steiner tree connection model corresponding to the net is shown in Figure 1(b). It can be seen that the length of the routing tree is greatly reduced after the introduction of the Steiner point. Therefore, the Steiner tree model has gradually become the best connection model for multi-pin net which is a key link in VLSI routing.

### 1) PROBLEM DESCRIPTION

The Steiner Minimum Tree (SMT) problem is to connect all pins through some extra points (called Steiner points) to achieve a minimal total length in VLSI routing.

In most routing problems, the segments can only route horizontally or vertically. This kind of routing tree is called Rectilinear Steiner Tree (RST). Rectilinear Steiner Minimum Tree (RSMT) construction is a NP-hard problem, which is as follows [29]: Given a set of points in the plane, the RSMT problem seeks to connect the points with a RST, which is a tree made up of horizontal and vertical line segments with the minimum cost. The cost of any edge in the tree is the rectilinear or Manhattan distance between its endpoints, and the cost of a tree is the sum of its edge costs.

However, this way of routing only horizontally and vertically limits the optimization of wirelength, so more

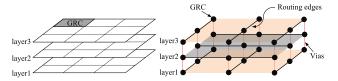

FIGURE 2. (a) Multilayer design. (b) Grid graph for routing.

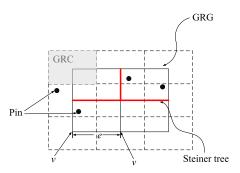

FIGURE 3. A GRG based on grid-graph.

research-oriented non-Manhattan architectures were proposed [30], [31]. Non-manhattan architecture routing trees mainly include Hexagonal Steiner Tree (HST) [30] and Octagonal Steiner Tree (OST) [31]. The routing directions of HST are considered at 0°, 60° and 120° to the horizontal direction called Y-routing, while OST with X-routing allows 45° and 135° directions in additon to traditional horizontal and vertical orientations. The non-Manhattan architecture related issues involved in this paper refers to X-architecture. Diversification of interconnection structures improves routing quality and improves chip performance.

#### **B. GLOBAL ROUTING**

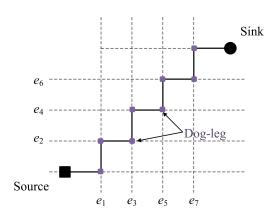

The global routing problem is a typical graph theory problem. The Global Routing Graph (GRG) abstracts the routing area, routing capacity of each area, pin information of routing areas, and the relationship between different routing areas into a grid graph, and then uses the corresponding graph algorithm to solve this problem.

### 1) PROBLEM FORMULATION

For global routing, modern designs usually have several metal layers and two adjacent layers are linked by *vias* as shown in Figure 2(b). We use a grid diagram to describe the global routing model, that is, the entire routing area is divided into a set of rectangles with rows and columns interlaced. Each Global Routing Cell (GRC) is represented by one vertex, and the adjacency relationship between GRCs is represented by horizontal and vertical edges. For a given set of nets, their pin sets are mapped to the vertices corresponding to the GRC according to the placement of this GRC. Figure 3 gives a GRG which is a set of dotted grids of interlaced rows and columns. Each dotted grid box represents a GRC, and a pin set is placed in the corresponding GRC according to the result of the layout. Each GRC is mapped into GRG as a vertex ( $\nu$ ) of GRG, and two GRCs having an adjacency relation are

connected by an edge (e) of GRG. So the relationship between GRC and GRG is one-to-one.

The global routing problem of VLSI can be described as follows: There is a grid-graph G specifying a set of vertices V and a set of edges E. As shown in Figure 2, each vertex  $v_i \in V$  corresponds to a rectangular region (or GRC) of the chip, and each edge  $e_{ij} \in E$  corresponds to a boundary between adjacent vertices. And there is a set of nets N, each net  $n_i \in N$  includes a set of pins  $P_i$  and each pin corresponds to a vertex  $v_i$ . The routing solution for a net is to find a tree that connects all pins of the net by using vias and routing edges. A solution of global routing is a set of SMTs in a grid graph, and a net corresponds to a Steiner tree that satisfies constraints. The goal of this phase is to minimize the length of the Steiner trees.

When evaluating a routing solution, one is typically concerned with three metrics, that is *overflow*, *wirelength*, *runtime* [32].

**Overflow** refers to the total amount of demand that exceeds capacity over all edges, here the demand corresponds to the number of routes that pass though the vertex [28]. In the actual design, we want this index to be as small as possible, ideally zero. The overflow of a routing edge e is defined as shown below:

$$overflow_e = \begin{cases} d_e - c_e, & \text{if } d_e > c_e \\ 0, & \text{otherwise} \end{cases}$$

(22)

where  $d_e$  represents the amount of nets that pass through e. The capacity  $c_e$  of routing edge e represents the number of available routing tracks it contains.

Wirelength is the total length of the segments that need to be connected for all nets, and it is desirable to be as small as possible. When using the routing tree models, the wirelength is generally equal to the length of the routing trees. Therefore, in many cases, various minimum trees are needed to be designed to solve the global routing problem. The Steiner tree mentioned above is one of the most common and effective models for solving global routing. In multi-dimensional routing, this calculation can also include vias.

**Time** is an indicator that we are particularly concerned about especially when reusing global routing to guide the layout algorithms [33].

# 2) COMMON GLOBAL ROUTING TECHNIQUES

Here is a brief list of some common global routing techniques.

# a: MAZE ROUTING

Maze routing is one of the most classic ways to solve the global routing problem, which considers all possible routes between a given source and a given sink on a routing graph. This technique finds the routing path with the least cost from source to sink by applying various shortest path algorithms. The earliest maze routing algorithm comes from Lee's algorithm [26], which is the most widely used minimum path algorithm for finding two-pin nets, but it has the problems of large search space and high complexity. Subsequently, the A\*

search technique [34] is used to improve Lee's algorithm to speed up convergence. For the problem of multi-pin nets, multi-source and multi-sink maze routing [35] developed from maze routing is applied to the tree edges, which considers more potentially better routes.

#### **b**: PATTERN ROUTING

Pattern routing routes a two-pin net with predefined patterns like L-shaped and Z-shaped patterns, which is more efficient than maze routing. However, the solution quality may become worse because not all possible routes in the bounding box of a two-pin net are considered [36].

# c: DECOMPOSITION TECHNOLOGY FOR MULTI-PIN NETS

This technology decomposes the task of global routing, that is, a multi-pin net is decomposed into several two-pin nets. The commonly used methods are SMT construction and MST construction. SMT often provides tree topologies with shorter wirelength, while MST shows greater flexibility because it can produce more L-shaped two-pin nets.

#### d: LAYER ASSIGNMENT

For multi-layer global routing, layer assignment maps a 2-D global routing result back to the original multi-layer solution space. Dynamic programming [37], Integer Linear Programming (ILP) [38], etc. are often used on this problem. Its main research focus is on minimizing the number of vias.

# e: OPTIMIZATION STRATEGIES

In order to improve the quality of solutions, researchers have put forward various optimization strategies. *Rip-up and reroute* [39] allows the nets passing through congested regions be ripped up and rerouted for finding alternative routes. And *negotiated congestion routing* can balance the competing goals of eliminating congestion and minimizing the performance degrading due to timing critical paths [40]. This idea based on negotiation mechanism has been widely used in the design of routing system.

## C. DETAILED ROUTING

Detailed routing realizes exact routing paths considering geometrical constraints based on the global routing solution, which is an important stage because it is directly related to the routing completion and design rule satisfaction.

#### 1) PROBLEM FORMULATION

For detailed routing based on grid models, the goal is to find a legal routing path on a given routing grid and detour the crowded area as much as possible. The relevant definitions and problem formula for detailed routing are given below [41].

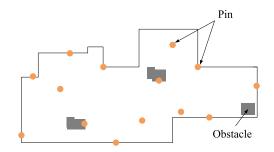

*Definition 1:* Channel (Routing Area). A rectilinear polygonal region between circuit blocks that can be used for interconnections (shown in Figure 4).

FIGURE 4. Routing area with obstacles.

*Definition 2:* Component. A set of pins and wire segments of a net which have been interconnected. Each unconnected pin is a trivial component.

The routing area is a right angle polygon. The location where the pins appear may be in the area or on the boundary. At the same time, we would like to take into account obstacles of various shapes and sizes. Detailed routing requires that all components of each net be connected within the routing area. The primary goal is to make the routing area as small as possible, and second, to minimize the number of vias and the wirelength of each net. At this stage, many other factors are also considered like power consumption, delay, coupling of interconnects, and so on.

#### 2) COMMON DETAILED ROUTING TECHNIQUES

Here is a brief list of some common detailed routing techniques.

#### a: BASIC PATH SEARCH ALGORITHM

Like global routing, detailed routing also uses the path search algorithm to find the wire routes such as Lee's algorithm, A\*, Soukup's algorithm [42], LCS\* [34], etc.

#### b: RIP-UP AND REROUTE

Most of detailed routing researches are based on serial routing. As with the global routing, serial routing is often optimized by rip-up and reroute. However, such a sequential net-by-net approach is ineffective in handling congested designs and it usually creates unnecessary detour [43].

#### c: PARALLEL ALGORITHMS

In order to reduce the dependence of routing results on the order of nets, a parallel detailed routing algorithm based on multi-commodity flow model is proposed [44], which can simultaneously route for multiple nets. Ozdal [45] presented an insightful technique to perform escape routing for dense pin clusters and a Lagrangian relaxation based heuristic was proposed.

# d: TRACK ASSIGNMENT

Track assignment is an ideal bridge between the global and detailed routing, which can effectively solve the mismatch between the two, thus better guiding detailed routing. In track assignment, segments extracted from global routing solution

are assigned to routing tracks. This technology provides a better initial routing scheme for detailed routing by considering constraints such as local nets, congestion, and the location of vias.

# IV. ROUTING PROBLEMS USING SWARM INTELLIGENCE

The purpose of this section is to introduce the application of SI techniques in VLSI routing. By analyzing the roles of SI techniques in routing problem, readers can more quickly and clearly realize the key points and difficulties to be solved in VLSI routing and advantages of SI in these aspects.

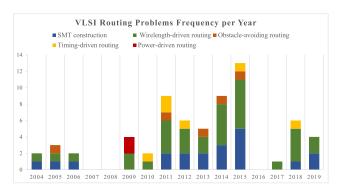

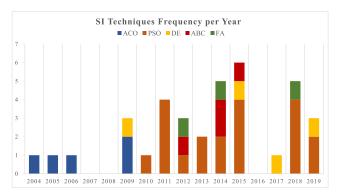

It is known that the basic optimization goal of routing is to minimize the interconnected wirelength while considering as many other optimization objectives as possible like obstacles, power consumption, timing and congestion. Therefore, every surveyed paper usually involves more than one routing problem mentioned in Table 2. And the application of SI techniques on global routing problems in Table 2 is given according to the most critical optimization objectives of surveyed papers.

#### A. APPLICATION OF ACO

#### 1) APPLYING ACO TO SMT CONSTRUCTION

ACO algorithm is widely used to construct SMTs [46]–[48]. In general, we generate the Hanan grid of the terminal set T. Then place the ants in each terminal that needs to be connected. An ant will determine a new vertex by some rules and move to that vertex via an edge in Hanan grid. Each ant maintains its own tabu-list, which records the visited vertices to avoid revisiting it again [46]. Every time the ants move, the ants will leave a footprint called pheromone on the edge that has just passed, which will evaporate at a constant rate.

The process of an ant moving to the next vertex depends on a higher value  $p_{i,j}$ , which is a trade-off between the desirability and the trail intensity. Given ant m in vertex i, the desirability of vertex j is defined as follows:

$$\eta_j^m = \frac{1}{c(i,j) + \gamma \cdot \psi_j^m} \tag{23}$$

where  $\gamma$  is a constant,  $\psi_j^m$  is the shortest distance from vertex i to all the vertices in the tabu-list of others as quickly as possible. We use Eq. (2) to update the trail intensity in Hanan edge (i,j), where the increment of updating is given by the following formula:

$$\Delta \tau_{i,j} = \begin{cases} \frac{Q}{c(S_t)}, & \text{if } (i,j) \in E_t \\ 0, & \text{otherwise} \end{cases}$$

(24)

where  $c(S_t)$  is the total cost of the current result tree  $S_t$ ,  $E_t$  is the edge set of it, and Q is a constant which matches the quantity of the tree cost. Based on Eq. (1), the probability of an ant using edge (i, j) to move is defined as follows:

$$p_{ij} = \begin{cases} \frac{[\tau_{ij}]^{\alpha} \cdot [\eta_j^m]^{\beta}}{\sum_{k \neq tabu-list(m)} [\tau_{ik}]^{\alpha} \cdot [\eta_k^m]^{\beta}}, & \text{if } j \in A \\ 0, & \text{otherwise} \end{cases}$$

(25)

TABLE 2. Application of SI techniques to the VLSI routing problems.

| SI Techniques | Routing problems                                     |                                       | References             |  |

|---------------|------------------------------------------------------|---------------------------------------|------------------------|--|

|               | SMT construction                                     |                                       | [46]–[48]              |  |

|               | Global routing                                       | considering obstacles                 | [48]                   |  |

| ACO           |                                                      | considering power consumption         | [49], [50]             |  |

|               |                                                      | considering interconnected wirelength | [46]–[50]              |  |

|               | SMT construction                                     |                                       | [29], [51]–[62]        |  |

| 700           | Global routing                                       | considering obstacles                 | [54], [56], [57], [59] |  |

| PSO           |                                                      | considering timing                    | [58], [63]–[66]        |  |

|               |                                                      | considering congestion                | [67], [68]             |  |

|               |                                                      | considering interconnected wirelength | [29], [51]–[68]        |  |

|               |                                                      | SMT construction                      | [69], [70]             |  |

| DE            | Global routing considering interconnected wirelength |                                       | [69]–[71]              |  |

|               | Restrictive channel routing                          |                                       | [72]                   |  |

| ARC           | SMT construction                                     |                                       | [73], [74]             |  |

| ABC           | Global routing considering interconnected wirelength |                                       | [73]–[77]              |  |

| EA            | Clabal and disc                                      | considering timing                    | [78]                   |  |

| FA            | Global routing                                       | considering interconnected wirelength | [62], [77], [78]       |  |

# Algorithm 1 Construct Steiner Tree by ACO

**Input**: terminal set *T*, connection graph **Output**: a rectilinear Steiner tree *T*

- Place an ant on each vertex in the terminal set T and put the vertex into its tabu-list;

- 2 Set the current sub-tree *t* empty;

- **while** ant number > 1 **do** 3 Select an ant m randomly; 4 5 AntMove(m);Add the edge m passing into t; 6 if m meets  $m_1$  then 7 Add vertices in tabu-list of m to that of  $m_1$ ; 8 9 m dies;  $Relocate(m_1);$ 10

- 11 **Prune**(t);

- 12 Return;

where A is the set made up of all vertices, which are connected with i and are not in the tabu-list of ant m [46].

The process of constructing an RST using ACO is shown in Algorithm 1 [47]. In Step 5, function AntMove(m) decides the next vertex that the current ant m will move to. And the encounter between two ants is described in Step 7 to 10. When ant m encounters ant  $m_1$ , ant m dies, and the vertices in the m's tabu-list are added into  $m_1$ 's. If  $m_1$  is still in the original position,  $Relocate(m_1)$  will re-create its position. When there is only one ant left, the tree is built. At the same time, Prune(t) is used to delete all 1-degree non-terminal vertices in the tree.

However, using ACO to find SMT is still time consuming because the ant's movement is based on the Hanan grid,

FIGURE 5. Definition of distance between two edges.

FIGURE 6. (a) BOTTOM\_ORIENT. (b) TOP\_ORIENT. (c) BOTTOM\_ORIENT segment. (d) TOP\_ORIENT segment.

and only a small segment can be moved per iteration. So [47] extends the tabu-list of each ant to record the edges instead of the vertices that this ant has visited so that every movement is not constrained by Hanan grid. They defined the distance between the two sides as follows: The distances between edge  $L_1$  and  $L_2$  in Figure 5(a), 5(b), 5(c), and 5(d) are h, h+w, h and h+w, respectively. And there are two possible ways to move when the shortest path is L-shape, which are TOP\_ORIENT and BOTTOM ORIENT. One orientation is chosen to move based on both the trail intensity and the topology. For a given edge orientation, the rules we find the closest vertex to the edge are shown in Figure 6. In Figure 6(c) and 6(d), vertex B represents the current location of an ant, and the closest vertex out of its tabu-list is vertex C. Next, the ant needs to decide the orientation of edge (B, C). Figure 6(c) shows that the closest vertex to edge  $(B_1, C_1)$  is  $A_1$  with distance  $|A_1A_1'|$  for BOTTOM\_ORIENT. While for TOP\_ORIENT, the distance between  $A_2$  and edge  $(B_2, C_2)$  is  $|A_2A_2'|$ , which is shown in Figure 6(d). So the gain in BOTTOM\_ORIENT

is  $|A_2A_2'| - |A_1A_1'|$  and the gain in TOP\_ORIENT is  $|D_1C_1| - |D_2D_2'|$ . The authors rewrote Eq. (23) according to this rule as follows:

$$\eta_d = \frac{[gain_d]^{\lambda}}{dist_d} \tag{26}$$

where d is the two orientations (BOTTOM\_ORIENT and TOP\_ORIENT),  $gain_d$  is the gain in orientation d,  $dist_d$  is the distance from the closest vertex out of its tabu-list to the edge in orientation d, and  $\lambda$  is a constant that is the trade-off between the closest distance and gain. In this way, an ant can cross several edges of Hanan grid in each iteration and one ant will be removed from the set of alive ants in each movement.

This ACO-Steiner algorithm [47] can be used to construct initial trees for all nets and optimize the routing tree iteratively to further reduce wirelength. Moreover, this algorithm can generate different topologies with the same wirelength for a net, which is beneficial to reduce congestion scarifying only a little wirelength.

Reference [48] presents an Obstacle-Avoiding Rectilinear Steiner Minimum Tree (OARSMT) algorithm based on ACO. In this algorithm, an efficient graph reduction method, called *T-Reduction*, is adopted to reduce the searching space. This method is implemented by maintaining an FIFO queue. Firstly all 2-degree vertices are pushed into the queue. Then pop the first vertex from the queue, delete the vertex and its adjacent edges, and its adjacent non-terminal vertices are pushed into the queue while the queue is not empty. Later, non-terminal convex corner points are reduced. And finally reduce 1-degree terminals. Such terminals can be deleted along with their adjacent edges. It's worth mentioning that T-Reduction method is very efficient when the case scale is not large and is also suitable for escape graph reduction. And a greedy obstacle penalty distance (OP-distance) local heuristic is used in this OARSMT algorithm at the same time, where the OP-distance is used to estimate the distance between two vertices in the presence of obstacles. The proposed algorithm has a high optimization capability of wirelength and can handle complex obstacle cases including both convex and concave polygon obstacles.

# 2) APPLYING ACO TO GLOBAL ROUTING

ACO-Steiner can be easily extended to other routing problems such as power-driven routing. References [49] and [50] implement ACO algorithms on both grid-less Manhattan architectures and non-Manhattan routing architectures that use diagonal routing, which aim at limiting the power consumption of the chip. The difference is that, [50] actives power on the chip not only by minimizing wirelength and vias, but also capacitance.

In [50], the characteristics of ant colony's memory, stochastic decision making and strategies of collective and distributed learning are used to find the shortest possible routes, then choose the one that minimizes capacitance from those routes. Unlike [46], an ant will not die when meeting another ant, but rather a particular connection is marked

as completed. Completing these paths can also reduce redundant paths, thereby decreasing the number of vias. The first step of the algorithm is to create a Hanan grid, then start routing nets using ACO. Notice that small nets are routed first in order to minimize obstruction from bigger nets. The specific ACO-Route approach can be described as Algorithm 2. The probability of unvisited nodes are calculated through the heuristic to minimize the distance between the ant and other ants and pheromone values (Step 10). If the ant meets another ant, for both the ants add the routes traveled by one to the route list of the other. The experiments prove that ACO is successful in solving the multi-constraint optimization problem of VLSI chip power minimization.

# Algorithm 2 ACO for Routing

- 1 Create Hanan grid;

- 2 Order nets according to degree and then size;

- 3 Initialize a small amount of pheromone on the whole grid;

- 4 while termination condition is not met do

# Route

7

11

6 **for** each ant **do**

Empty ant's memory;

8 Place ant at some terminal node;

Construct a complete tour for ant;

10 Calculate the probability of unvisited nodes;

Deposit pheromone on the paths taken by the ant;

Find the best ant of the iteration;

13 Update the global pheromone value;

14 End Route

Find the shortest ant routed solution, and check if any part of this solution interferes with any other solution.

#### B. APPLICATION OF PSO

# 1) APPLYING PSO TO SMT CONSTRUCTION

The PSO algorithm introduced in Section II is usually used to solve continuous problems, while VLSI routing is a discrete problem. For this reason, many scholars have improved SPSO to solve actual discrete problems. At present, PSO has been widely used in SMT construction for VLSI routing problem, and has achieved good results. The key of SMT construction is the selection of Steiner points.

#### a: RST CONSTRUCTION USING PSO

Dong *et al.* [51] proposed a routing algorithm based on discrete particle swarm optimization (DPSO-RA), aiming at length and the bound of connectivity rate. The algorithm adopts a novel encoding and several update operations for DPSO, and achieves interconnection of all destination nodes in VLSI.

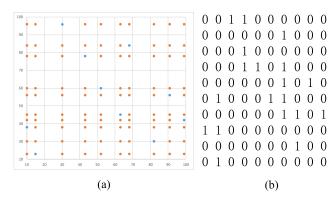

FIGURE 7. (a) The establishment of Steiner matrix. (b) Particle coding of Steiner matrix.

**Particle Encoding.** Each particle represents an MST. DPSO-RA encodes the particle by establishing Steiner Matrix. A particle  $X_i$  is a matrix and is expressed as:

where n is the number of components waiting for interconnection. Each bit of the particle encoding corresponds a node in the Steiner Matrix, and is valued in binary. The nodes to be connected, called "terminal nodes", are taken as input from the user or are generated randomly in the form of x and y-coordinates. If a node is selected to construct the RST, the value of the bit is '1', otherwise '0'. Usually, the matrix will be reduced by deleting some rows and columns that do not have any terminal nodes.

Steiner Matrix is established by the horizontal and vertical lines' cross-points of the components. And it represents the possible locations of the Steiner nodes of RST. Figure 7(a) shows a Steiner Matrix of 10 components (blue) to be connected. Its corresponding particle is shown in Figure 7(b).

The velocity  $V_i$  of particle  $X_i$  is also a matrix, expressed as follows:

$$v_{11}$$

$v_{12}$   $\cdots$   $v_{1n}$

$v_{21}$   $v_{22}$   $\cdots$   $v_{2n}$

$\vdots$   $\vdots$   $\ddots$   $\vdots$

$v_{n1}$   $v_{n2}$   $\cdots$   $v_{nn}$

where each bit of the velocity represents the probability of selecting the corresponding node in Steiner Matrix.

**Fitness Function.** The cost of MST is the fitness value of this particle, which is calculated by Prim's algorithm.

**Update Operation.** DPSO-RA redefines the operations of PSO and uses Eq. (3) and (4) as the position and velocity of the particle respectively.

*Definition 3:* "—" Operation. The result of "—" operation between two particle locations is a velocity.

Definition 4: "+" Operation. The result of "+" operation between two velocities is a new velocity.

FIGURE 8. Obstacle-avoiding construction by generating virtual vertexes.

Definition 5: " $\times$ " Operation. The parameters  $c_1$  and  $c_2$  are constants,  $r_1$  and  $r_2$  are random numbers between 0 and 1. The result of " $\times$ " operation between a velocity and parameters is still a velocity.

#### Algorithm Processes.

Step 1. Initialize the particle swarm.

Step 2. Calculate the fitness value of each particle.

Step 3. Update pbest and gbest.

Step 4. Calculate the self-adaptive inertia weight for each particle.

Step 5. Update the velocity and position of particles.

Step 6. If the termination condition is met, the algorithm ends. Otherwise return to Step 2.

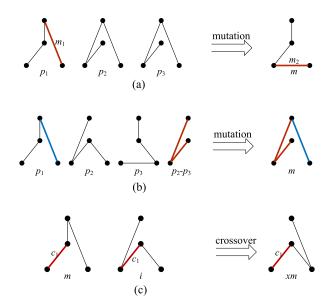

References [52] and [53] also use Steiner Matrix to encode the particles, and introduce the mutation operation of GA into DPSO. In [52], a matrix corresponding to a particle represents both position and velocity. Its velocity is updated by Eq. (3), while Eq. (4) is not used to update the position of the particle. The algorithm updates the position by selecting only some bits of the position matrix of the particles from the previous generation. This is the mutation process they introduced that can increase the efficiency and robustness of DPSO. Reference [53] uses PSO algorithm with constriction factor, that is, Eq. (7) is used to update the velocity and Eq. (4) is used to update the position. This algorithm adapts a novel mutation operation by selection of some bits of the previous position vector along with the information of the initial Steiner Matrix.

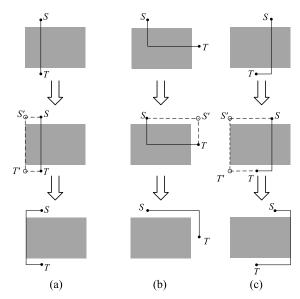

Shen *et al.* [54] considered wirelength and obstacles at the same time and then proposed a novel OARSMT construction algorithm, which avoids obstacles by generating virtual vertexes of the real vertexes. The algorithm designs the following obstacle-avoiding strategy for the case where the three types of routing across obstacles shown in Figure 8. Take Figure 8(a) as an example. First, vertices S and T

respectively produce corresponding virtual vertices, which have the same horizontal coordinate with the left (or right) edge of the obstacle and the same vertical coordinate with the original vertices. Next, sequentially connect S, S', T' and T, and dismantle the violate edges.

The OARSMT construction is divided into the following

- (1) Divide all the pins of the net into k groups, and generate corresponding RSTs based on the above-mentioned obstacleavoiding strategy. The algorithm places the pins that are close to each other in a group, while making the amount of each group of pins (at least two pins) as small as possible.

- (2) Wirelength minimization is the optimization goal, and then [54] connects all of the groups considered as real vertexes to construct the final RST.

In this algorithm, Prüfer number [79] is used to encode the solution of RST, and 0-1 coding is used to select Steiner points. For example, a particle is represented by:

$$X_i^t = \begin{bmatrix} 2 & 5 & 4 & 5 & 4 & 100 \\ 0 & 1 & 0 & 0 & 1 & 15 \end{bmatrix}$$

where the Prüfer number is  $\{2,5,4,5,4\}$ , and the Steiner point selection scheme is  $\{0,1,0,0,1\}$ , the total length of this tree is 100 and the obstacles quantities of this particle is 15.

The algorithm introduces crossover and mutation operators inspired from GA to handle Prüfer numbers which are discrete magnitude. Based on SPSO (Eq. (3)), the following position update formula is given for solving the discrete problems:

$$X_i^t = c_2 \oplus F_2(c_1 \oplus F_1(\omega \oplus F(X_i^{t-1}), P_i^{t-1}), G_i^{t-1})$$

(27)

Eq. (27) uses the "+" operation to connect the following three parts, in other words two operations including mutation and crossover operation.

# (1) Mutation operation:

$$\lambda_i^t = \omega \oplus F(X_i^{t-1}) = \begin{cases} F(X_i^{t-1}), & r_0 \le \omega \\ X_i^{t-1}, & else \end{cases}$$

(28)

where F represents the mutation operator from GA with the probability of  $\omega$ , and  $r_0$  is a random number on the interval [0, 1).

#### (2) Crossover operation:

$$\delta_{i}^{t} = c_{1} \oplus F_{1}(\lambda_{i}^{t}, P_{i}^{t-1}) = \begin{cases} F_{1}(\lambda_{i}^{t}, P_{i}^{t-1}), & r_{1} \leq c_{1} \\ \lambda_{i}^{t}, & else \end{cases}$$

(29)

$$X_{i}^{t} = c_{2} \oplus F_{2}(\delta_{i}^{t}, G_{i}^{t-1}) = \begin{cases} F_{2}(\delta_{i}^{t}, G_{i}^{t-1}), & r_{2} \leq c_{2} \\ \delta_{i}^{t}, & else \end{cases}$$

(30)

$$X_i^t = c_2 \oplus F_2(\delta_i^t, G_i^{t-1}) = \begin{cases} F_2(\delta_i^t, G_i^{t-1}), & r_2 \le c_2 \\ \delta_i^t, & else \end{cases}$$

(30)

where  $F_1$ ,  $F_2$  represent the crossover operators that influence self-cognitive and social-cognitive respectively, and the probabilities are  $c_1$  and  $c_2$ .  $r_1$  and  $r_2$  are random numbers on the interval [0, 1).

This paper proposes a novel framework of PSO to solve OARMST problem and extends the application of SI algorithm in VLSI physical design. Many of the later

FIGURE 9. Four options of Steiner point for a given line segment.

works [55]-[61], [67], [68], [80], [81] are also based on this PSO framework of Eq. (27).

#### b: OST CONSTRUCTION USING PSO

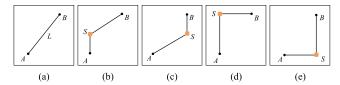

Liu et al. [55], [56], Huang et al. [56], [57], and Liu et al. [58]-[61] have done a lot of research work on the construction of Octagonal Steiner Minimum Tree (OSMT) based on the following interconnected structure, and have achieved excellent results.

**Interconnected Structure**. There are four choices for line segment L of connecting pins A and B as shown in Figure 9. And [55] gives four definitions about selection of Steiner points.

Definition 6: Choice 0 (as shown in Figure 9(b)). The Choice 0 of Steiner point corresponding to edge L is defined as leading rectilinear side first from A to Steiner point S, and then leading non-rectilinear side to B.

Definition 7: Choice 1 (as shown in Figure 9(c)). The Choice 1 of Steiner point corresponding to edge L is defined as leading non-rectilinear side first from A to Steiner point S, and then leading rectilinear side to B.

Definition 8: Choice 2 (as shown in Figure 9(d)). The Choice 2 of Steiner point corresponding to edge L is defined as leading vertical side first from A to Steiner point S, and then leading horizontal side to B.

Definition 9: Choice 3 (as shown in Figure 9(e)). The Choice 3 of Steiner point corresponding to edge L is defined as leading horizontal side first from A to Steiner point S, and then leading vertical side to B.

Particle Encoding. Based on the above design of interconnected wire, [55] uses numerical encoding called Edgeto-Point encoding to represent each candidate OST: For a net with n pins, a spanning tree would have n-1 edges, n-1 Steiner points and one extra bit which is the fitness of particle. Besides, two bits represent the two vertices of each edge. Namely, the particle is encoded with a numerical string of  $3\times(n-1)+1$ . For example, a particle can be expressed as follows:

# 7 6 **0** 6 4 **1** 7 5 **1** 5 1 **2** 1 3 **0** 1 8 **1** 5 2 **2** 0.0100

where the number '0.0100' is the fitness of the particle and each number in bold represents the Steiner point choice. Taking the first substring (7, 6, 0) for instance, it represents one edge of the spanning tree which is composed of *Vertex* 7, *Vertex 6* and the Steiner point choice (*Choice 0*).

Reference [55] introduces mutation and crossover operations as particle update strategies like [54]. Like the problems of RST, we also study related problems of OST

0 0 0

0

0

0 0

0

0

such as Obstacle-Avoiding Octagonal Steiner Minimum Tree (OAOSMT). References [56]–[58] consider the construction of OST with key issues such as obstacles, delay and number of bends, also based on this encoding method and particle update strategies, while using Union-Find Sets (UFS) to prevent the generation of invalid solutions. Reference [60] constructs OSMT based on self-adapting PSO with an effective Hybrid Transformation Strategy (HTS) to enlarge the search space. While [61] presents a unified algorithm for both octagonal and rectilinear SMT construction, and also applies HTS to PSO, which can achieve a better wirelength optimization. These two algorithms both have an ability to obtain multiple topologies of Steiner trees with the same wirelength, so that it can provide different topology options for congestion optimization in global routing.

# 2) APPLYING PSO TO GLOBAL ROUTING

PSO is also widely used for global routing because of its simplicity and the ability to quickly converge to an ideal solution.

Minimizing wirelength and reducing congestion are the most common and important tasks for global routing. Liu et al. [68] proposed a high-quality VLSI global router in X-architecture called XGRouter, which was based on ILP techniques, partition strategy and PSO. Their ILP formulation, called O-ILP, considers the congestion uniformity to get a more even routing distribution without generating too many hot spots and the solution has no overflowed edges. At the main stage of their algorithm, ILP is formulated from the original routing sub-region and an improved PSO is designed to solve the O-ILP formulation. In their proposed PSO, the 0-1 integer encoding is used for particle encoding, which can satisfy the completeness and non-redundancy principle. And based on the update formula of particles (Eq. (27)), a check strategy is incorporated in the crossover and mutation operators to meet the soundness principle. Finally, not only the wirelength but also the congestion uniformity is considered into the fitness function to generate better solutions. Reference [67] presents some enhancements based on XGRouter. In this paper, some new types of routing are introduced and PSO algorithm is combined with maze routing. This improved algorithm can be applied to multi-layer routing model, which can achieve good results on overflows and total cost of wirelength.

With the continuous development of the manufacturing process and design scale of IC, the feature size is continuously reduced, the parasitic effect of the connection is not negligible, and the interconnection delay exceeds the gate delay, which becomes the main factor determining the performance of the circuit. Therefore, it is necessary to consider other typical performance optimization targets except wirelength, such as delay and power dissipation. Several techniques have been used to reduce interconnection delay - wire sizing, buffer insertion, and buffer sizing. Among them, buffer insertion is the most effective interconnection optimization method to reduce delay.

FIGURE 10. (a) Location of obstacles. (b) Corresponding vertex value.

Ayob et al. [63] employed PSO to solve buffer insertion problem in VLSI routing, with considerations on wire and buffer obstacles. They used distributed RC network as interconnected model and applied the Elmore Delay formulation to calculate the interconnection delay from source to sink.

#### a: ELMORE DELAY CALCULATION

For computation delay where the iterative calculation starts from source then advance to the sink, each node in the wire is labeled with a resistance-delay pair (r, t) where r is resistance of wire and t is delay time accumulated up to that node, respectively [82]. If the subsequent segment is wire, then the subsequence delay pair (r', t') is defined as:

$$r' = r_w + r$$

(31)

$t' = (r + r_w/2)c_w + t$  (32)

$$t' = (r + r_w/2)c_w + t (32)$$

where  $r_w$  and  $c_w$  are the resistance and capacitance of the wire segment, respectively. If the segment consists of wire with buffer then (r', t') is defined as:

$$r' = r_b \tag{33}$$

$$t' = r(c_w + c_b) + r_w(c_w/2 + c_b) + d_b + t$$

(34)

where  $d_b$ ,  $r_b$  and  $c_b$  are the intrinsic buffer delay, buffer output resistance and buffer input capacitance, respectively.

#### b: GRID-GRAPH MODEL

This algorithm utilizes a grid-graph model to represent routing path and buffer placement location. Figure 10(a) shows the location of source and sink (dark), buffer obstacle (gray) and wire obstacle (dark). And Figure 10(b) shows the corresponding value of each vertex location. The value is set to 1, which indicates the presence of wire obstacle for routing the path. The region whereby buffer is not permitted (buffer obstacle area) will be set to 2. Value = 0 represents the area that is possible for routing path and for buffer placement location.

# c: PARTICLE ENCODING