Received December 11, 2019, accepted January 5, 2020, date of publication January 8, 2020, date of current version January 17, 2020. Digital Object Identifier 10.1109/ACCESS.2020.2965016

# A Survey on Machine Learning Against Hardware Trojan Attacks: Recent Advances and Challenges

ZHAO HUANG<sup>®1</sup>, QUAN WANG<sup>®1</sup>, (Member, IEEE), YIN CHEN<sup>®2</sup>, (Member, IEEE), AND XIAOHONG JIANG<sup>®3</sup>, (Senior Member, IEEE)

<sup>1</sup>School of Computer Science and Technology, Xidian University, Xi'an 710071, China

<sup>2</sup>Graduate School of Media and Governance, Keio University Shonan Fujisawa Campus, Fujisawa 252-0882, Japan

<sup>3</sup>School of Systems Information Science, Future University Hakodate, Hakodate 041-8655, Japan

Corresponding author: Quan Wang (qwang@xidian.edu.cn)

This work was supported in part by the National Natural Science Foundation of China under Grant 61572385 and Grant 61702395, and in part by the National Institute of Information and Communications Technology (NICT), Japan.

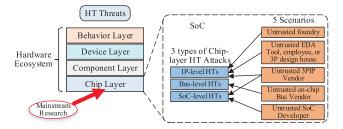

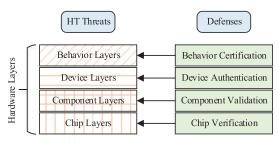

**ABSTRACT** The remarkable success of machine learning (ML) in a variety of research domains has inspired academic and industrial communities to explore its potential to address hardware Trojan (HT) attacks. While numerous works have been published over the past decade, few survey papers, to the best of our knowledge, have systematically reviewed the achievements and analyzed the remaining challenges in this area. To fill this gap, this article surveys ML-based approaches against HT attacks available in the literature. In particular, we first provide a classification of all possible HT attacks and then review recent developments from four perspectives, i.e., HT detection, design-for-security (DFS), bus security, and secure architecture. Based on the review, we further discuss the lessons learned in and challenges arising from previous studies. Despite current work focusing more on chip-layer HT problems, it is notable that novel HT threats are constantly emerging and have evolved beyond chips and to the component, device, and even behavior layers, therein compromising the security and trustworthiness of the overall hardware ecosystem. Therefore, we divide the HT threats into four layers and propose a hardware Trojan defense (HTD) reference model from the perspective of the overall hardware ecosystem, therein categorizing the security threats and requirements in each layer to provide a guideline for future research in this direction.

**INDEX TERMS** Machine learning, hardware Trojan detection, design-for-security, bus security, secure architecture.

# I. INTRODUCTION

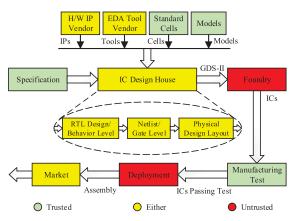

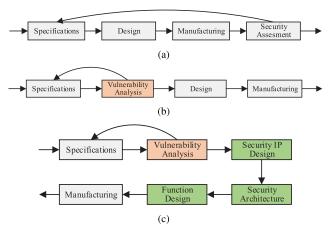

The tremendous advancements in semiconductor technology have resulted in a large number of participants coordinating during the design and manufacturing process of integrated circuits (ICs) [1], [2]. Particularly given the continuously increasing complexity of ICs, increasingly greater numbers of specialized teams and/or companies, typically dispersed geographically, are involved in this complex process to increase efficiency and manufacturability. However, due to its highly distributed nature, any stage of this complicated supply chain can be compromised by an adversary (or attacker) by implanting malicious circuits [2], [11]. Fig. 1 illustrates the stages that could be exploited in a typical design-fabrication process of modern ICs [3], [4]. Such malicious circuits, often referred to as hardware Trojans (HTs), will endanger the security and

The associate editor coordinating the review of this manuscript and approving it for publication was Liehuang Zhu<sup>(b)</sup>.

trustworthiness of the underlying hardware by, e.g., disclosing confidential information, impeding normal executions at vital points, and even prompting irreversible and fatal damage to the system [3], [11]. This fact also poses a serious threat to semiconductor suppliers and end IC users, which may include critical applications and cyber infrastructure such as mobile communications, aerospace agencies, medical electronics, military weapons, and nuclear reactors [4], [12]. Given this situation, it is both critical and challenging to study defensive strategies to alleviate the potential security threats posed by the so-called HT attacks.

# A. HT DEFINITION, TAXONOMY, AND PROTECTION

# 1) HT DEFINITION AND CLASSIFICATION

HTs are defined as malicious, intentional inclusions/deletions/ alterations, or inadvertent design defects of ICs or intellectual property (IP) cores that can be exploited by knowledgeable adversaries to achieve the purpose of an attacker, which may

**FIGURE 1.** Potential stages of modern IC supply chain that can be exploited to implant Trojans [4].

result in vast economic losses and great harm to society [13], [14], [16].

HT circuits can be categorized in a variety of forms according to different features. Several studies have introduced detailed taxonomies to cover a wide range of HT instances. Early work can be traced back at least to Banga et al., who classified HTs into two categories according to the logical types, i.e., *combinational* and *sequential* [5]. However, this classification failed to take the impacts of analog trigger conditions and effective payload into account. Tehranipoor et al. presented classifying HTs into three categories based on their physical, activation, and action characteristics [6]–[8]. Although this HT taxonomy was more detailed than previous approaches, it contained only a limited number of Trojan examples, and its correlation with the IC development cycle was not obvious. Zhang et al. classified HTs into two categories, namely, bug-based HTs and parasite-based HTs, based on their impacts on the normal functionalities of the circuits [9]. However, there was not much discussion about their trigger conditions and implantation stage. Bhunia et al. proposed classifying HTs as analog Trojans and digital Trojans based on the trigger and payload mechanisms [4], [8], wherein the digital Trojan also included both combinational and sequential types.

Karri et al. integrated and extended the above classification methods and introduced an *attributed-based* HT taxonomy [36], [37]. Based on the study of Wang et al., they classified HTs based on *five* different attributes, adding considerations of design phase, location, and abstraction level. Subsequently, Moein et al. separated HTs based on *eight* different *attributes* and included *three* more attributes, i.e., logic type, physical layout, and functionality, to further improve the HT classification [17], [38]. In particular, Table 1 lists these typical studies on HT taxonomies. These previous taxonomies continue to evolve as newer attacks and Trojan types are discovered.

Here, we present a new, systematic taxonomy based on the relationship between the *locations* of HT circuits inserted into a system-on-chip (SoC) and the *targets* affected by the

#### TABLE 1. Typical Studies on HT Taxonomies.

| Article    | Class            | Features                            | Each Category                                                                                                              |

|------------|------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| [5]        | 2                | Logical Types                       | Combinational and Sequential                                                                                               |

| [6], [7]   | 3                | Trojan Features                     | Physical, Activation, and Action                                                                                           |

| [9]        | 2                | Trojan Impacts                      | Bug-based and Parasite-based                                                                                               |

| [4]        | 2                | Circuit Features Analog and Digital |                                                                                                                            |

| [36], [37] | [36], [37] 5 Att |                                     | Design Phase, Abstraction Level,<br>Activation, Effects and Location                                                       |

|            |                  | Attributes                          | Design Phase, Abstraction Level,<br>Activation, Effects, Location, Lo-<br>gic Types, Physical Layout, and<br>Functionality |

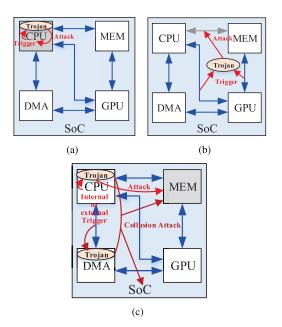

FIGURE 2. Typical representatives of the three types of Trojan threats [18]. (a) IP-level HTs. (b) Bus-level HTs. (c) SoC-level HTs.

Trojan attacks when triggered. Thus, the HT circuits can be categorized into three types: (1) IP-level HTs, (2) bus-level HTs, and (3) SoC-level HTs, as shown in Fig. 2.

- **IP-level Trojans** this type of HT is implanted into the individual function IP cores of the SoCs (or into simple logic circuits) and triggered by internal conditions such as rare nodes/nets. When activated, they can only affect the specific IP cores in which they are implanted (as shown in Fig. 2 (a)) [18].

- **Bus-level Trojans** this type of HT is connected with the network fabrics of buses (i.e., linkers [26], [27]) or embedded into the modules of the on-chip buses (such as routing nodes [19], [108], control units, and network interfaces [28]). They are mainly triggered by internal rare signals or by data flowing through the on-chip buses and can tamper with the integrity and reliability of interconnection fabrics and routers in the SoC designs (as shown in Fig. 2 (b)) [18]–[20].

- SoC-level Trojans this type of HT is inserted into the individual function IP cores of the SoCs and can affect the behaviors of other IP cores. Alternatively,

#### TABLE 2. Typical Studies on Broad Classifications of HT Countermeasures.

| Article    | Class | Each Category                                                                     |  |  |

|------------|-------|-----------------------------------------------------------------------------------|--|--|

| [6]        | 1     | HT Detection                                                                      |  |  |

| [8], [35]  | 2     | HT Detection and HT Prevention                                                    |  |  |

| [7], [10]  | 2     | HT Detection and Design for Hardware Trust (DFHT)                                 |  |  |

| [4]        | 3     | HT Detection, Design for Security (DFS), and<br>Runtime Monitoring                |  |  |

| [16]       | 3     | HT Detection, Design for Trust (DFT), and Split<br>Manufacturing for Trust (SMFT) |  |  |

| [13], [14] | 3     | HT Detection, HT Diagnosis, and HT Prevention                                     |  |  |

several untrusted third-party (3P) IP cores, which are obtained from 3PIP vendors, may collaborate to perform collusion attacks on other IP cores or even the SoCs. Moreover, the trigger conditions of this type of HT vary, e.g., rare conditions occurring within the implanted IP cores, special instructions or external sequences, etc. This type of HT is designed to affect the overall system functions rather than the infected IP cores (as shown in Fig. 2 (c)) [20].

#### 2) CLASS OF MITIGATION STRATEGIES

Substantial research efforts, from both academia and industry, have been devoted to the studies of HTs [11], [21], [22]. Table 2 lists several typical studies on the classification of HT protections. The initial mitigation strategies were mainly focused on HT detection approaches and design for security (DFS) [6]–[8], [35], [39]. HT detection is a pre-/post-silicon detection technique that is used to determine whether the hardware is contaminated by malicious logic or by an undesired functional unit [13], [14], [16], [23], whereas DFS<sup>1</sup> methods mainly prevent the inclusion of malicious circuits at hardware design time or facilitate detection at test time or run time [21], [24].

Bhunia et al. attempted to classify the mitigation strategies as HT detection, DFS, and runtime monitoring according to the effective stage of each kind of technique [4]. The runtime validation strategies were separated from DFS and employed as a major class of online monitoring approaches to safeguard against potentially undetected HT threats at run time. Xiao et al. categorized the defensive methods as HT detection, design for trust (DFT), and split manufacturing for trust (SMFT) [16]. Similarly, the split manufacturing approaches were used as a separate class of protections since these approaches can prevent the insertion of HTs at fabrication time. Furthermore, Li et al. also categorized the countermeasures for HTs into 3 classes: HT detection, HT diagnosis, and HT prevention [13], [14]. Different from the works of Bhunia and Xiao et al., they added a new class of protections to the previous 2 categories, i.e., HT diagnosis. An HT diagnosis approach is designed to identify the locations, types and trigger conditions of the HT circuits in an IC or IP core [14]. However, research on the classification of HT protections still faces some challenges, especially with the emergence of new HT countermeasures, and a new category of protection strategies for HTs is still required.

Based on the HT taxonomy discussed in Section I.A.1, we present that protections against HT threats can be categorized into 4 broad classes of solutions, namely, 1) HT detection, 2) DFS, 3) bus security, and 4) secure architecture. HT detection and DFS strategies are intended to defend against IP-level HTs. Moreover, research on HT defense techniques has also been expanded to bus security (e.g., network-on-chips, abbreviated as NoCs, [25]-[27], [108], and advanced-high-performance [29], [30], etc.) and secure architecture [18], [20], [31]–[34]. These countermeasures are special DFS strategies and are meant to address the integrity problems of on-chip buses incurred by bus-level HTs and suspicious behaviors created by SoC-level HTs at runtime, respectively. In particular, Table 3 lists the key distinctions between IP-level HTs, bus-level HTs and SoC-level HTs, as well as the corresponding mitigation countermeasures.

From Table 3, it can be concluded that IP-level HTs appear to be a special case of SoC-level HTs since they have some overlap in their locations and trigger mechanisms. However, they have significant differences in the following respects. (1) The design and attacker location are different. IP-level HTs are relatively simple and are designed to be implanted in an individual IP core (or simple logic circuit) by adversaries during the design or manufacturing stage, whereas SoC-level HTs come in many varieties and may exist in one or more 3PIP cores provided by untrusted IP vendors. (2) The impacts are different. IP-level HTs only affect the specific IP cores in which they are embedded, whereas SoC-level HTs more strongly impact other IPs or even the general SoC functions, rather than the implanted IP cores. (3) Most importantly, the defense strategies against these two types of HT threats are different. IP-level HTs are typically detected via circuit features, such as functional or structural features, or parametric characteristics, e.g., power or path delay, whereas SoC-level HTs are identified by using dynamic behavior analysis of the whole SoC design. (4) In addition, the effective application stages of the respective defense strategies are also different (see Table 3).

On the other hand, bus-level HTs are also clearly different from SoC-level HTs, which can be embodied in the following aspects. (1) The design and attacker location are different. SoC-level HTs are implanted inside one or more IPs, while bus-level HTs are embedded into the modules of the on-chip buses or connected with the buses, not inside the IPs. (2) The impacts are different. Bus-level HTs can only tamper with the interconnection among cores, while SoC-level HTs affect the function of other IPs and even the whole SoCs. (3) Most importantly, the defense countermeasures to address these two types of HT threats are also different. The defense strategies for alleviating the bus-level HTs only concern the linker and router behaviors, while the defense strategies for resisting SoC-level HTs incorporate the behaviors of IP cores or the overall system together.

<sup>&</sup>lt;sup>1</sup>In most of the survey articles on HTs, DFS, HT prevention, DFHT, and DFT have similar meanings. Therefore, this paper will uniformly adopt DFS in the following description.

| Type<br>Property  | IP-level HTs                                                                                      | Bus-level HTs                                                                           | SoC-level HTs                                                               |

|-------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Location          | Individual function IP cores<br>(or simple logic circuits)                                        | On-chip buses such as linkers,<br>routers, or interfaces                                | One or more function IP cores                                               |

| Attack Target     | IP cores (or simple logic circuits)<br>in which HTs implanted                                     | Fabrics, linkers, routers, or interfaces                                                | Other IP cores or even the entire SoCs                                      |

| Trigger Condition | Internal rare nodes/nets                                                                          | Internal rare signals or data flowing<br>through the on-chip buses                      | Internal rare nodes/nets, or special instruction/sequence external          |

| Attack Pattern    | Relatively simple                                                                                 | Normal                                                                                  | Diversity                                                                   |

| Trojan Impact     | Only affect the specific IP cores<br>in which HT implanted                                        | Tamper the integrity and reliability of in-<br>terconnection fabrics or routers in SoCs | Impact the behavior of other IPs<br>or even the overall SoC functions       |

| Defense Strategy  | Exploit static trust verification techniques for HT detection                                     | Extract and identify traffic patterns of on-chip buses                                  | Validate potentially suspicious activities<br>by dynamic or formal analysis |

| Effective Stage   | Design / Test time                                                                                | Run time                                                                                | Run time                                                                    |

| Technique Feature | Feasibility and impact analysis of<br>Trojans in individual IP cores<br>(or simple logic circuit) | Real-time matching of abnormal traffic linker or router features                        | Fine-grained SoC behavior analysis<br>and assertion-aware security decision |

| Deficiency        | Fail to address error correction<br>or recovery                                                   | Continuous verification of data features exchanged across on-chip buses                 | Focus mainly on in-field protections                                        |

#### TABLE 3. Key Distinctions between IP-level, bus-level and SoC-level Trojans.

#### **B. MOTIVATION AND CONTRIBUTIONS**

Several excellent surveys have been devoted to designs, categorizations, and protections for HT problems [1], [4], [7], [8], [13]–[17], [21], [35]–[39]. For example, Sumathi et al. provided a comprehensive review of complex HT threats and illustrated feasible countermeasures against HT attacks for PLD and ASIC life cycles [1]. Zhang et al. highlighted the potential security and trust threats associated with FPGA-based systems from a market perspective and discussed the relevant solutions available for each party [15]. In 2016, Bazzazi et al. explained the taxonomies of HT threats and presented a new classification of HT detection and counterattack techniques [8]. Li and Zhang et al. reviewed the specific HT threats faced by the parties involved in the IC development process and described up-to-date HT defense solutions [13], [14], [35]. Subsequently, Xiao et al. summarized the research advancements and lessons learned concerning HT problems in recent years and explored possible future trends [16]. In addition, Jacob et al. also elaborated the feasibility of Trojan insertions and corresponding defense strategies at each stage of the IC development and production chain [39]. Table 4 summarizes the primary research contents of several related surveys published in recent years.

Note that the aforementioned surveys primarily focus on HT threats and corresponding HT detection (such as reverse engineering [40]–[43], logic testing [44], [45], and sidechannel analysis [46]–[49]) and prevention (such as detection assistance [50]–[52] and implantation prevention [53]–[55]) techniques. Compared with the existing surveys, this paper intends to review the specific HT threats and defense solutions from a different perspective of SoC life cycle. We identify the potential HT types at each stage of SoC development and examine the state-of-the-art HT countermeasures related to each stage. The recent success of machine learning (ML) techniques in many research domains has inspired both academic and industrial communities to explore the potential of applying ML to address various HT attacks [11], [56].

#### **TABLE 4.** Primary Research Contents of Several Related Surveys.

| Article                                                                                                  | Main Research Contents                                                                                                                                                         |  |  |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [1]                                                                                                      | Review the potential HT threats and defense solutions at each stage of PLD and ASIC life cycle.                                                                                |  |  |

| [4]                                                                                                      | Describe the complex HT threat models and feasible pro-<br>tections against HT attacks in specific fields of ICs.                                                              |  |  |

| [8]                                                                                                      | Explore the taxonomy of HT threats and provide an over-<br>view of HT detection and counterattack techniques.                                                                  |  |  |

| [15]                                                                                                     | Discuss the potential security and trust threats for the par-<br>ties involved in the FPGA-based market model.                                                                 |  |  |

| [13], [14]                                                                                               | Explain the feasibility of HT insertions faced by the part-<br>ies involved in the IC life cycle models and describe up to<br>date HT defense solutions.                       |  |  |

| [16]                                                                                                     | Introduce a comprehensive adversarial model taxonomy,<br>review the defense strategies corresponding to each class,<br>and explore possible future trends.                     |  |  |

| [17], [38],<br>[36], [37]                                                                                | Present the attribute-based HT classification methods.                                                                                                                         |  |  |

| [21]                                                                                                     | Illustrate the robustness of specific DFS techniques to pr-<br>event HT threats and examine their limitations.                                                                 |  |  |

| [35] Analyze the possible infection scenarios and the de mechanisms of HTs for hardware development pro- |                                                                                                                                                                                |  |  |

| [39]                                                                                                     | Evaluate the feasibility of Trojan insertions and the pract-<br>icability and cost of Trojan detection techniques at each<br>stage of the IC development and production chain. |  |  |

A number of achievements utilizing ML for HT defenses have emerged in the last decade. However, this important progress has not been systematically reviewed in previous surveys [4], [13], [14], [16], [21], [35], [39]. Elnaggar et al. conducted a survey on the applications of ML in the general area of hardware security, including HT attacks, reverse engineering, IC counterfeiting, side-channel attacks, and IC overbuilding [56]. However, a dedicated survey on the applications of ML to HT defenses is still not available in the literature. In addition, most of the aforementioned surveys focused on IP-level HT threats and may overlook bus-level and SoC-level HT attacks or corresponding mitigation strategies.

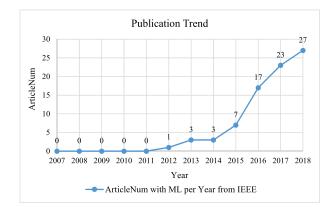

To fill this gap, we first investigate publications with regard to the HT problems found in the IEEE Xplore

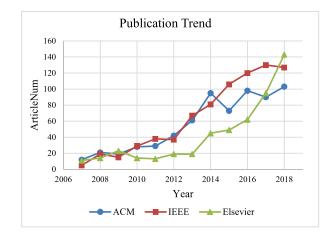

FIGURE 3. Publication trends on HTs from IEEE, ACM, and Elsevier.

digital library,<sup>2</sup> the ACM DL digital library,<sup>3</sup> and Elsevier ScienceDirect.<sup>4</sup> Fig. 3 illustrates the number of articles on HTs published in the digital libraries annually starting from 2007 to 2018. In particular, we have specifically reviewed the recent progress in utilizing ML techniques against HT threats and revealed the potential problems, challenges and possible future research directions in this domain. Note that the up-to-date bus-level and SoC-level HT attacks and ML-related mitigation strategies have also been elaborated in this paper. It is expected that this survey will serve as a general guidebook for those who want to contribute to the study of HTs.

The main contributions of this article are summarized as follows:

- (1) This article, for the first time to the best of our knowledge, systematically investigates the latest research progress in applying ML technology in the fields of HT detection and prevention.

- (2) The explicit analysis highlights the new advances in using ML-based techniques in HT defense domains to address the IP-level, bus-level and SoC-level Trojan threats from the perspectives of HT detection, DFS, bus security, and secure architecture.

- (3) We also analyze some important aspects related to the application of ML algorithms in HT defense domains and discuss its potential challenges facing the state-ofthe-art.

- (4) In addition, we propose a reference model for recommending possible strategies that each layer should be able to utilize along with future directions for HT research based on the analysis of the above situations.

The remainder of this article is organized as follows. In Section II, we present typical ML models used in HT defense studies. A detailed discussion of the HT threat models and the advancements in applying ML for HT defenses is presented in Section III. Section IV discusses the lessons learned

<sup>2</sup>http://ieeexplore.ieee.org/Xplore/home.jsp

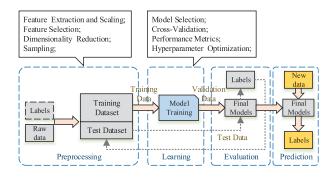

FIGURE 4. The general flow of ML framework.

and challenges arising from the previous studies. Section V gives a reference model of HTs from the perspective of the overall hardware ecosystem and provides a discussion on future research directions. Finally, we conclude this article in Section VI.

#### **II. ML MODELS USED IN HT DEFENSES**

This section presents typical ML models that have been widely utilized to solve HT problems. Section II.A depicts the general procedure of applying ML, as well as commonly exploited ML algorithms. Section II.B analyzes the current publication trend of ML in the HT defense domain.

#### A. ML MODELS

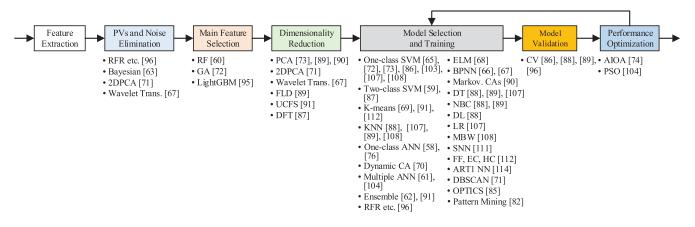

ML is a class of algorithms that primarily focuses on generating the "models", namely, learning algorithms, from a large amount of historical "data" and then utilizing these trained models for prediction or classification [57]. As illustrated in Fig. 4, the general procedure of applying ML algorithms involves the following: (1) In the preprocessing phase, the relevant features are first selected, and then, data with these features are extracted from the raw data so that they can be utilized to distinguish the different values of the target outputs. After that, several data cleansing and feature engineering operations, such as principal feature selection, scaling, and dimensionality reduction, are executed to generate the sample dataset for learning. (2) In the learning phase, the appropriate learning algorithms are selected and executed to derive the models from the training dataset. Such models correspond to a certain underlying law about the data. Then, operations such as cross-validation, result evaluation, and hyper-parameter optimization are carried out to acquire the final models. (3) In the evaluation phase, the final models are tested on the test dataset to evaluate their performance. In practice, evaluation criteria can be selected and customized according to different scenarios. (4) In the prediction phase, the final models are exploited to infer the predicted values of the target output for the newly input data.

According to the nature of the data types processed by ML, there are two major categories of learning tasks that are widely explored in HT defense domains: supervised learning and unsupervised learning. The supervised learning technique utilizes the labeled data to perform model training

<sup>&</sup>lt;sup>3</sup>http://dl.acm.org/

<sup>&</sup>lt;sup>4</sup>http:/www.sciencedirect.com/

and selects the final models to predict the target classes of the newly input data; in contrast, unsupervised learning techniques focus more on revealing the potential relations characterizing the data by learning from them when the data labels for all the target classes are unavailable. In particular, the major difference between supervised learning and unsupervised learning is whether the data labels are available.

Below, we present an overview of the most frequently explored ML algorithms, feature selection and dimensionality reduction methods, and several optimization and model enhancement techniques in HT defense studies.

# 1) SUPERVISED LEARNING

- Artificial Neural Networks (ANNs) [58] are an abstraction and simulation of the human brain. They can be viewed as a mathematical model from an algorithmic perspective and construct various networks according to different connection patterns. ANNs have been successfully implemented in diverse applications for classification, including HT detection.

- **Support Vector Machine (SVM)** [59] is a two-class classification model with the largest interval in the feature space. SVM's learning strategy is to maximize the interval, which can ultimately be transformed into solving convex quadratic programming problems. SVM is suitable for HT detection and has been widely applied in this area.

- **Bayesian Classifiers** [63] are a type of classification algorithm based on probability statistics and misjudgment losses. Bayesian classifiers can achieve the minimum error rate.

- **One-class Classifiers** are variants of supervised models; they are used when one wants to determine whether the new training data belong to a particular class (i.e., whether the data are normal or abnormal data). Thus, one-class classifiers have been proposed for novelty and anomaly detection, which can be regarded as one-class classification problems. At this point, the boundary of the training data needs to be learned rather than the maximum margin. **One-class ANNs** [64] and **One-class SVM** [65] are two representative one-class classifiers.

- **Back-propagation NNs (BPNNs)** [66], [67] are a kind of feed-forward ANN that may contain multiple hidden layers. BPNNs can adjust the network weights and thresholds during training to achieve a nonlinear mapping of the input and output as well as better generalization ability.

- **Extreme Learning Machine (ELM)** [68] is a singlehidden-layer feed-forward ANN (SLFN) that can randomly initialize the input weight and bias and obtain the corresponding output weight. ELM has been widely used in many fields due to its high learning speed and good generalization ability.

- **Decision Tree (DT)** [88] is a tree-structure-based learning model that contains a root node, several internal

nodes, and several leaf nodes. The leaf nodes correspond to the decision results, while the other nodes correspond to an attribute test. The decision-learning process of the DT method is similar to the method humans use to make choices. In this process, each judgment question raised is a "test" of a certain attribute, and the final conclusion corresponds to the decision result that we expect. Classification tree and regression tree are commonly used DT models.

- **K-Nearest Neighbors (K-NN)** [89] classify the training dataset by measuring the distance between different eigenvalues. The general idea is that if the majority of the *k* most similar samples (i.e., the nearest neighbor in the feature space) in a feature space belong to a certain category, then the sample also belongs to this category, where *k* is usually an integer less than 20. In K-NN, the selected neighbors are all objects that have been correctly classified.

# 2) UNSUPERVISED LEARNING

- **Clustering Algorithms (CAs)** [72] intend to group unlabeled data into different clusters. CAs do not require priori experience as input. One major reason for using CAs in the HT protection field is the unobtainable features of golden designs/ICs, as CAs will be unaffected by this issue.

- **K-means Clustering** [69] is a variant of prototypebased CAs that attempts to discover a user-defined number (k) of clusters and partitions a set of *n* data points into *k* clusters in such a way that the resulting intra-cluster similarity is high but where the inter-cluster similarity is low.

- Density-Based Spatial Clustering (DBSCAN) [71] and Ordering Points to Identify the Clustering Structure (OPTICS) [85] are typical density-based CAs. They can find points with higher density starting from the estimated density of the corresponding nodes, and then gradually connect the high-density points into one block to generate various clusters. The advantage of density-based CAs is that clusters of various shapes and sizes can be revealed in data possessing noise.

# 3) FEATURE SELECTION AND DIMENSIONALITY REDUCTION

- **Genetic Algorithms (GAs)** [72] are popular heuristic algorithms. A GA can be applied for the feature selection of classification problems whose goal is to find a small subset of variables from the dataset that provides the highest classification accuracy.

- **Principal Component Analysis (PCA)** [73] is a widely used data dimensionality reduction technique in which *n*-dimensional features are mapped to a *k*-dimensional space. The newly reconstructed *k*-dimensional features, also known as principal components, are orthogonal. Each of the principal components can reflect most of the original variables, and the information contained therein is not repeated. In this process, the dimension *k* of the

low-dimensional space is usually specified by the users in advance and is much lower than n.

- 2-Dimensional PCA (2DPCA) [71] is a variant of the PCA technique in which the covariance matrix can be constructed directly based on 2D matrices rather than being transformed previously into 1D vectors. 2DPCA can overcome the deficiencies of PCA such as high computational complexity and time consumption.

#### 4) DESIGN OPTIMIZATION AND MODEL ENHANCEMENT

- Adaptive Iterative Optimization Algorithm (AIOA) [74] is a model-enhancing technique in which a specific classifier is iteratively improved using the input training data weighted by a weight vector to reduce the errors.

- **Multi-Objective Evolutionary Algorithm (MOEA)** [75] is an enhanced optimization algorithm that starts from randomly generated populations and then increasingly approaches the Pareto-optimal solutions by applying multiple-generation continuous optimization operations with adaptability.

- **Particle Swarm Optimization (PSO) Algorithm** [104], [125] is an optimizer that attempts to find the optimal solution through the cooperation and information sharing among individuals in a group. PSO is simple and easy to implement, and it does not require complex parameter adjustments. The quality of the optimal solution can be evaluated by the fitness.

Table 5 illustrates the advantages and disadvantages of each type of ML algorithm. As shown in Table 5, supervised learning is effective in addressing cases with few features and can achieve relatively better classification results. Especially for HT detection, a definitive output can be presented for each input. However, supervised learning requires golden designs/ICs, i.e., data with labels, as a reference and is also unsuitable for training on large datasets. Unsupervised learning can overcome these deficiencies. However, unsupervised learning is sensitive to noise and readily falls into local optima. In particular, the output results for each training process cannot be determined clearly. On the other hand, feature selection and dimensionality reduction methods can reduce the related features and decrease the data dimensions; however, the HT features might be deleted as redundant information because they have little impact on circuits, and the threshold values need to be determined manually. In addition, some DFS strategies can be improved by design optimization algorithms. However, this process is time consuming and takes multiple iterations to achieve the optimal solution.

# **B. PUBLICATION TREND OF ML APPLIED IN HT DEFENSES**

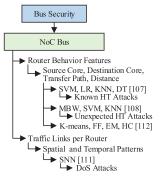

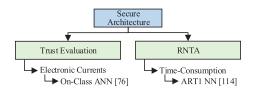

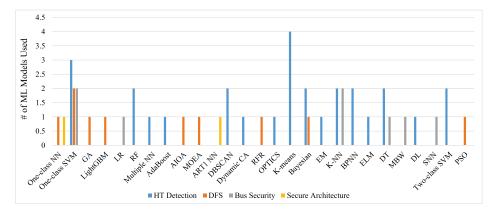

Fig. 5 shows publications on ML-based techniques exploited for HT defense in the IEEE Xplore digital library, which can be used to represent the research trends in HT defense studies to a certain extent (as shown in Fig. 3). In particular, the mitigation strategies that are tackled using ML primarily involve HT detection, DFS, bus security, and secure architecture.

| TABLE 5.         Advantages | and Disadvantages o | f each Type of ML in HT |

|-----------------------------|---------------------|-------------------------|

| Defense Studies.            |                     |                         |

| Machine<br>Learning<br>Algorithms                            | Advantages                                                                                                                                                                                                                                                                                               | Disadvantages                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supervised<br>Learning                                       | <ol> <li>Handle quickly for cases<br/>with fewer features;</li> <li>Having clear output to t-<br/>he input;</li> <li>Relatively better classifi-<br/>cation results;</li> <li>Learning models is non-<br/>sensitive for noise.</li> </ol>                                                                | <ol> <li>Require golden designs<br/>or ICs as reference;</li> <li>Easy to over-fitting and<br/>under-fitting;</li> <li>Improper to train large<br/>dataset;</li> <li>Unsuitable to address<br/>multi-classification proble-<br/>ms.</li> </ol>                       |

| Unsupervised<br>Learning                                     | <ol> <li>Need no golden designs<br/>or ICs as reference;</li> <li>Unexpected output;</li> <li>For addressing large da-<br/>taset, it is scalable and effic-<br/>ient;</li> <li>Model is simple, easy to<br/>implement, and the perform-<br/>ance does not depend on par-<br/>ameter choosing.</li> </ol> | <ol> <li>Relatively poor classification results;</li> <li>Easy to slip into local optimal solutions;</li> <li>Learning models is sensitive for noise;</li> <li>Cluster number is difficult to select;</li> <li>Sensitive to initial cluster center value.</li> </ol> |

| Feature<br>Selection<br>and Dimen-<br>sionality<br>Reduction | <ol> <li>(1) Select effective features,<br/>decrease data dimensions an-<br/>d remove redundant features;</li> <li>(2) Improve the accuracy of<br/>HT detection and prevent<br/>over-fitting;</li> <li>(3) Reduce attribute space.</li> </ol>                                                            | <ol> <li>This process will take<br/>a little more time.</li> <li>HT features may be lo-<br/>st as redundant data;</li> <li>Require to determine<br/>the threshold manually;</li> <li>Need to make multiple<br/>attempts and adjustments.</li> </ol>                  |

| Design<br>Optimization<br>and<br>Model<br>Enhancing          | <ol> <li>Mostly used to enhance<br/>DFS strategies;</li> <li>Decrease rare signals;</li> <li>Improve the performance<br/>of learning models.</li> </ol>                                                                                                                                                  | <ol> <li>This process is time consuming;</li> <li>Only effective for simple combinational circuits;</li> <li>Need many iterations to select the best solutions.</li> </ol>                                                                                           |

FIGURE 5. Overall publication trend of ML in HT defenses.

As can be seen from Fig. 5, approximately 80 articles were published on the studies of ML-based HT defense from 2007 to 2018. Early work in this area can be traced back at least to Jin et al., who proposed in 2012 that a one-class ANN model could be used to determine whether chips have been infected by Trojan circuits [76]. The publication count was scarce and remained basically stable from 2012 to 2014. Since 2014, the research achievements in this area have been expanding rapidly each year. As a result, it is expected that increasingly more articles on ML-based solutions will be published in this regard.

| Scenario | Attacker Location                                                 | Trojan Type          | Specific Attack Goal                                                                                                                               | Insert Stage            | Defender                                             | Defend Strategy        |

|----------|-------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------|------------------------|

| A        | Untrusted Foundry                                                 |                      | Leak Sensitive Information / Modify                                                                                                                | Fabrication             | 3PIP Vendor / SoC Developer                          | HT Detection           |

| В        | Untrusted EDA Tool<br>or Employee<br>Untrusted 3P Design<br>House | IP-level<br>Trojans  | Functionality / Reduce Reliability /<br>Irreversible Destruction etc. (by<br>maliciously modifying circuit<br>structures, functionalities, or      | Design                  | 3PIP Vendor / SoC Developer<br>/ Foundry             | DFS /<br>HT Detection  |

| C        | Untrusted 3PIP<br>Vendor                                          | -                    | parameters)                                                                                                                                        | Design                  | SoC Developer / Foundry                              | DFS /<br>HT Detection  |

| D        | Untrusted SoC<br>Developer                                        | Bus-level<br>Trojans | DoS / Traffic Diversion / Routing Loop<br>/ Core Spoofing (through untrusted<br>links and/or routers)                                              | Design /<br>Fabrication | Foundry / System Designer<br>/ Integrator / End User | Bus Security           |

| E        | Untrusted SoC<br>Developer or<br>3PIP Vendor                      | SoC-level<br>Trojans | Interception / Interruption / Divert /<br>Tamper / Masquerader / Fault Injection<br>/ Failure / Collusion Attack (through<br>untrusted 3PIP cores) | Design /<br>Fabrication | Foundry / System Designer<br>/ Integrator / End User | Secure<br>Architecture |

#### TABLE 6. HT Threat Models at Chip Layer.

# III. THREAT MODELS AND ML-BASED COUNTERMEASURES

This section introduces the major advances of ML techniques applied in HT defenses. Section III.A reviews the HT threat models in the modern IC supply chain from the perspective of the chip layer. Section III.B details the advances in ML-based countermeasures from the aspects of HT detection, DFS, bus security and secure architecture.

# A. THREAT MODELS

HTs can be implanted at any stage of the design and fabrication process, which leads to diverse threat models [16]. From the perspective of the chip layer, the overall designfabrication process of an SoC design can be divided into three stages: IP core development, SoC development, and fabrication [77]. Therefore, *five* types of participants in this process, i.e., 3P design houses or employees, commercial electronics design automation (EDA) tools, 3PIP vendors, SoC developers, and foundries, have opportunities to implant HTs. Table 6 systematically summarizes five typical scenarios of the chip-layer HT attacks that have appeared in the literature.

Each scenario is explained as follows:

- Scenario A (i.e., untrusted foundry): An attacker at the foundry could implant an HT instance into the design by manipulating the lithographic masks. These HTs appear in the forms of modification to the transistors, gates, and interconnects into the original layout.

- Scenario B (i.e., untrusted EDA tool, employee, or 3P design house): Because increasingly more specialized IC designers and tools have become involved in the design-fabrication process, HTs might be inserted by untrusted 3P commercial EDA tools or rogue designers within the in-house team (also called insider threats) [16]. Moreover, customers may also outsource their specifications to offshore 3P design houses, and these untrusted design houses may add additional modules or functions to the original design.

- Scenario C (i.e., untrusted 3PIP vendor): SoC developers may purchase and employ 3PIP cores to complete their SoC designs. These IP cores provided by

untrusted 3PIP vendors to customers may contain malicious logic or backdoors.

- Scenario D (i.e., untrusted routers or links in on-chip bus): An adversary may compromise the integrity of the on-chip buses using malicious routing nodes or traffic links that have been infected with HTs. Such malicious bus fabrics would then be integrated into the SoCs.

- Scenario E (i.e., untrusted SoC developer): This attack scenario assumes that an untrusted SoC developer may develop SoC designs infected with SoC-level HTs or integrate the soft/firm/hard IP cores from untrusted 3PIP vendors containing such HT circuits that can separately or jointly impact other IP cores or the functions of the overall SoC functions.

# **B. ML-BASED COUNTERMEASURES**

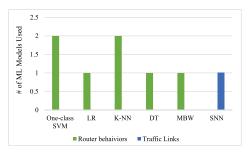

ML has been extensively exploited in a variety of HT defenses. Here, we consider the *four* primary types of countermeasures that can be applied to one or more attack scenario: 1) HT detection that utilizes available circuit features, e.g., structures, functionalities, and parameters, to reveal the HTs (i.e., Scenarios A, B, and C); 2) DFS that exploits security design strategies to enhance the trustworthiness of IC designs or intends to facilitate HT detection, prevention, and monitoring via on-chip modules (i.e., Scenarios B and C); 3) bus security that aims to identity malicious on-chip traffic behaviors created by bus-level HTs (i.e., Scenario D); and 4) secure architecture that is designed to resist SoC-level HT threats and secure the original IC designs from an architectural point of view (i.e., Scenario E).

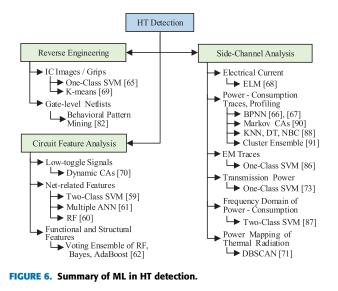

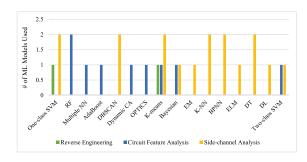

# 1) HT DETECTION

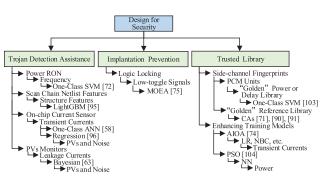

HT detection techniques are typically used to verify whether any unwanted circuit is implanted in designed or fabricated ICs. Thus, ML-based techniques have seen progress in terms of (1) reverse engineering, (2) circuit feature analysis, and (3) side-channel analysis. Fig. 6 shows a summary of ML techniques applied in these aspects. In particular, Table 7 briefly elaborates the primary research contributions and innovations of ML algorithms applied in HT detection according to Fig. 6.

#### TABLE 7. Main Research Contributions and Innovations of ML in HT Detection.

| HT Detection | Article     | Main Research Contributions and Innovations                                                                |  |  |  |

|--------------|-------------|------------------------------------------------------------------------------------------------------------|--|--|--|

| Reverse      | [65], [69]  | One-class SVM or K-means can classify or cluster IC images in destructive RE.                              |  |  |  |

| Engineering  |             |                                                                                                            |  |  |  |

| Circuit      | [70]        | Dynamic CAs can cluster LTS features in the gate-level netlists of IP cores.                               |  |  |  |

| Feature      | [59], [61]  | Two-class SVM or multiple ANN can classify Trojan-related features extracted from the net of ICs.          |  |  |  |

| Analysis     | [60]        | RF can be used to select the best set of Trojan-infected features from the original IC features.           |  |  |  |

| Anarysis     | [62]        | Voting Ensemble of RF, Bayes and AdaBoot can classify functional and structural features of ICs and incre- |  |  |  |

|              | [02]        | ase the HT detection accuracy.                                                                             |  |  |  |

|              | [68]        | ELM can classify the electrical current features of ICs.                                                   |  |  |  |

| Side-        | [66], [67], | PNN, KNN, DT, NBC, DL, PCA+Markv. CAs and CA ensemble can classify or cluster power-consumpt               |  |  |  |

| Channel      | [88], [89], | trace, or profiling features of ICs.                                                                       |  |  |  |

| Analysis     | [90], [91]  |                                                                                                            |  |  |  |

| 7 mary 515   | [86]        | One-class SVM with the RBF kernel can classify EM traces infected by HTs.                                  |  |  |  |

|              | [73]        | PCA+one-class SVM can preprocess and classify the transmission power waveform.                             |  |  |  |

|              | [87]        | DFT+two-class SVM can preprocess and classify the frequency domain of power-consumption converted          |  |  |  |

|              | [ [07]      | from time domain.                                                                                          |  |  |  |

|              | [71]        | 2DPCA+DBSCAN can preprocess, cluster and locate HTs by using the power mapping of thermal radiation.       |  |  |  |

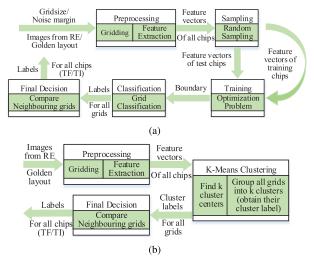

FIGURE 7. Block diagram of ML-based HT detection methods. (a) SVM-based Trojan Detection Method [65]. (b) K-means-based Trojan Detection Method [69].

As shown in Table 7, the main application of ML methods in these aspects is to classify or cluster IC-related features to improve the HT detection accuracy. Next, we present the main elements of each ML-based approach, as well as the advantages and disadvantages between ML-based and non-ML-based methods in detail.

# - Reverse Engineering

A reverse engineering (RE) technique is utilized to repackage the ICs and obtain microscopic images of each layer to reconstruct the original design of the end products [4]. This technique has the potential to achieve very high accuracy in identifying any modifications to the ICs. However, such an irreversible approach might require several weeks or even months to apply this intrusive process to a complex IC, making its application usually limited to the testing of a limited number of IC samples [78].

However, it is still attractive to perform destructive reverse engineering on a limited number of IC samples to obtain the characteristics of a golden batch of ICs [79], [80].

10804

For instance, Bao et al. presented an efficient and robust reverse engineering-based method to identify HT-free ICs via ML [65], [69]. By using the one-class SVM and K-means technique successively, a classifier was developed to automatically learn how to distinguish between the expected and suspicious structures in an IC, as shown in Fig. 7. Such procedures can simplify traditional 5-step reverse engineering to 3 steps and avoid the need to generate and manually enter the gate-level netlists extracted from the image-based IC designs in the last 2 steps. Moreover, the performance of K-means clustering does not depend on the choice of parameters, making it easier to train and adjust than SVM. However, this intrusive process still requires golden designs, i.e., Trojan-free designs.

Moreover, non-destructive reverse engineering, which attempts to reverse the gate-level netlist of an IC design into a high-level description of the control logic, such as finite state machines [42], [43], [81], has also been investigated. For instance, Li et al. proposed reversing the unknown ICs into the

FIGURE 8. LTS-based directed graph caused by HTs [70].

input-output track model via behavioral pattern mining and discovering the Trojan circuitry through behavioral pattern matching [82]. Though non-intrusive, such a process only outlines an approximate functional model of the original design and cannot fully represent its actual function design. In particular, non-destructive reverse engineering still suffers the same deficiencies as destructive engineering, e.g., only being valid for simple logic circuits and being costly and time consuming.

# - Circuit Feature Analysis

An adversary may create a HT instance that is activated under rare conditions or implanted into IC designs as a redundancy module. Due to their stealthy nature, such Trojans cannot be detected during traditional formal testing [84], [85]. Therefore, circuit features, e.g., functional or structural features, extracted from the gate-level netlists can be quantified and analyzed to potentially identify whether a net or gate is suspicious, wherein the switching activity and net feature are two quantitative metrics that are commonly utilized for HT detection [83].

Zhou et al. presented a structural feature matching method to detect sequential HTs in 3PIP cores [70]. By analyzing the structural features of less-toggled signals (LTS) in the gate-level circuits of IP cores, this method first abstracts the LTS caused by HTs into a directed graph (as illustrated in Fig. 8) and then utilizes dynamic CAs for structural feature matching. On the other hand, *n* features extracted from each net can be utilized to differentiate Trojan-infected nets from normal nets. For example, Kasegawa et al. extracted five HT-net feature values from each net in gate-level netlists and learned them using a classifier such as SVM or ANNs [59]. After that, the trained classifier can be used to classify a set of features from an unknown gate-level netlist. This method can increase the true positive rate (TPR) of detecting an HT circuit; however, there are deficiencies in terms of the true negative rate (TNR) and average accuracy [61]. Additionally, they applied RF to select the best set of Trojan features and reduce the original 51 features to the most effective 11 features, which are then utilized to classify the target nets [60]. In addition, Hoque et al. proposed a systematic learningbased approach to verify the trustworthiness of untrusted hardware 3PIPs [62]. Unlike existing learning models that rely only on structural features, they incorporated both functional and structural features to create a robust training set and used an average probability voting ensemble combined with multiple learning models to improve the HT detection efficiency.

Side-channel analysis refers to measuring circuit parameters, such as power, path delay, temperature, and electromagnetic (EM) radiation profiles, to isolate a Trojan-infected IC from the golden ICs. This analysis fully utilizes the advantage of the parametric variations in side-channel information created by extra circuitry and/or the activities from HTs. However, the effectiveness of HT detection through sidechannel analysis largely relies on the signal-to-noise ratio (SNR) and the Trojan-to-circuit ratio (TCR) [4] because the side-channel features could be affected by process variations (PVs) and noise.

ML is expected to overcome the deficiencies when incorporated with side-channel analysis, thereby improving the SNR [65], [86], and research along this direction has drawn increased attention in recent years.

Some researchers have attempted to apply ANNs to sidechannel analysis. For example, Wang et al. presented an HT detection method to indicate whether the ICs are Trojaninfected by sampling and classifying the current features using an ELM [68]. Li et al. extracted the nonlinear features from the power-consumption through the HT detection model established by the BPNN [66], [67]. The ELM and BPNN can be used for feature extraction and inference because they can better retain and extract useful information for analysis, thereby avoiding the inaccuracy of manual modeling. However, there is a lack of preprocessing of the sampled side-channel features and the results of each training may be slightly volatile.

SVM can overcome the instability of ANNs during training and theoretically enhance the HT detection capability and classification accuracy. SVM is also a relatively general classification algorithm employed in side-channel analysis. For instance, Dimanto et al. proposed that HT detection can be modeled as an outlier detection problem, and the effects of an HT instance on EM traces can be directly identified through one-class SVM with the RBF kernel [86]. However, this process only contains a simple feature selection and fails to substantially improve the SNR. In contrast, Liu et al. presented a combined PCA and SVM approach (i.e., PCA+SVM) to detect the covert communication-type Trojans by utilizing the transmission power waveform [73]. Iwase et al. suggested converting the power waveform data from the time domain to the frequency domain through a discrete Fourier transform (DFT) and then conducting HT detection using SVM [87]. The PCA+SVM and DFT+SVM methods first preprocess the sample features and extract the effective part, which is more conducive to detecting and classifying HT instances. In addition, the PCA+SVM method is more accurate than the combined PCA and minimum volume enclosing ellipsoid (MVEE) method (i.e., PCA+MVEE) [73].

Furthermore, Lodhi et al. developed a runtime HT detection approach based on an online adaptive ML model [88]. The power profiling of a given micro-controller instruction set is first extracted and then classified by K-NN, DT, naive Bayesian (NBC), and deep learning (DL). This approach is

| HT Detection                | Non-ML bas                                                                                                                                                                                                             | ed Strategies                                                                                                                                                                                                                                  | ML based                                                                                                                                                                                                                                                                  | Strategies                                                                                                                                                                                                                                                       |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology                  | Positives                                                                                                                                                                                                              | Negatives                                                                                                                                                                                                                                      | Positives                                                                                                                                                                                                                                                                 | Negatives                                                                                                                                                                                                                                                        |

| Reverse<br>Engineering      | <ul> <li>Include physical level and<br/>design level</li> <li>Physical level reverse is<br/>irreversible</li> <li>Design level reverse is a<br/>non-destructive method</li> <li>Accuracy could be 100%</li> </ul>      | <ul> <li>Costly, time consuming</li> <li>Physical level reverse is a destructive method</li> <li>Effective for simple logic circuits</li> <li>Require golden ICs as reference</li> </ul>                                                       | <ul> <li>No golden chips are available.</li> <li>Automatically learn to identify<br/>suspicious circuits</li> <li>Simplify traditional 5-step re-<br/>verse engineering to 3 steps</li> <li>Avoid generating and entering<br/>the gate-level netlists manually</li> </ul> | <ul> <li>Require golden designs as<br/>reference</li> <li>Performance of classification<br/>models relies on parameter</li> <li>Clustering models are sensiti-<br/>ve to noise</li> <li>Mainly valid during test time</li> </ul>                                 |

| Circuit Feature<br>Analysis | <ul> <li>Typical heuristic methods</li> <li>Easy to implement and effective in practice</li> <li>Extract and quantify circuit characteristics</li> <li>Can detect the suspicious statements or modules</li> </ul>      | <ul> <li>Require golden designs<br/>as reference</li> <li>Fail to detect implicit HT</li> <li>Manual post-processing is<br/>required to analyze if it is<br/>(part of) a HT circuit</li> <li>Suitable for simple logic<br/>circuits</li> </ul> | <ul> <li>Can identify and classify HT-net<br/>features automatically</li> <li>Increase the TPR and efficiency</li> <li>Extract the most important HT-<br/>net features</li> <li>decrease the size of feature vec-<br/>tors, i.e., attribute spaces</li> </ul>             | <ul> <li>Require golden designs as<br/>reference</li> <li>Fail to detect implicit Trojan</li> <li>TNR and accuracy need to fur-<br/>ther improve</li> <li>Execution time depends on the<br/>circuit scale and the quantitati-<br/>ve metrics selected</li> </ul> |

| Side-channel<br>Analysis    | <ul> <li>Non-invasive approaches</li> <li>Easy to operate and implement, applied widely</li> <li>High detection accuracy</li> <li>No require to activate HT</li> <li>Can effectively identify large Trojans</li> </ul> | <ul> <li>Can be affected by noise<br/>and PVs easily</li> <li>Perform poorly on the det-<br/>ection of small Trojans</li> <li>Require golden designs/<br/>ICs as reference</li> <li>High precision requireme-<br/>nt on equipment</li> </ul>   | <ul> <li>Decrease the impacts of noise<br/>and PVs</li> <li>Can effectively extract relevant<br/>features, reduce data dimensions</li> <li>Partly offset the golden ICs</li> <li>Improve the accuracy, TPR, etc.</li> </ul>                                               | <ul> <li>HT effects may be removed as<br/>irrelevant features or noise</li> <li>Performance relies on the sele-<br/>ction of relevant features, ML<br/>models, and parameters, etc.</li> <li>Increase time overhead</li> </ul>                                   |

| TABLE 8. Comparisons of Positives and Negatives between ML-based and non-ML-based Approaches in | HT Detection. |

|-------------------------------------------------------------------------------------------------|---------------|

|-------------------------------------------------------------------------------------------------|---------------|

able to compare and analyze various ML models and choose the most suitable model [89]. However, such a process is very time consuming, and the selection of the most appropriate ML algorithm heavily relies on the detection cases and the number of attributes required.

Most of the aforementioned classification algorithms for side-channel analysis assume that there are available golden ICs (i.e. Trojan-free fabricated ICs) to refer to during training. However, such an assumption is difficult to realize in practice. To this end, researchers have also attempted to apply CAs to side-channel analysis because they do not need priori experience as input and can eliminate the dependence on golden designs/ICs to a certain degree [91].

Nowroz et al. introduced a post-silicon multi-model approach that utilizes runtime thermal radiation and power maps for HT detection [71]. Multiple scenarios are considered there. If trusted data from known chips are available for training, a supervised thresholding method can be applied to classify the chips under detection by the Euclidean distance of the feature matrix and the golden design. Otherwise, 2DPCA can be performed to address the high-dimensional power maps converted from thermal radiation data; then DBSCAN can be exploited to detect and locate the HTs. Cui et al. developed an HT detection method with the Markov distance as the clustering center [90]. The collected power-consumption is first analyzed by PCA, and then, the clustering operation is completed with the Mahalanobis distance as the class center. Multi-mode-based HT detection takes both supervised learning and unsupervised learning into account to combine their advantages. Moreover, CA based on the Mahalanobis distance performs better than the Euclidean distance in that it is designed to optimize the detection process and can overcome the shortcomings of the Euclidean distance so that it can achieve lower computational complexity and higher accuracy.

Table 8 illustrates the advantages and disadvantages between ML-based and non-ML-based methods in HT detection. For reverse engineering, conventional solutions, including physical-level and design-level reverse engineering, can achieve 100% accuracy in detecting Trojans. However, these schemes are costly, time consuming, and only effective for simple logic circuits. They are also difficult to apply in practice. In contrast, ML can overcome some of the abovementioned deficiencies. For example, ML can simplify the reverse engineering process and learn to identify suspicious circuits automatically. However, the performance depends on the selection of learning models and corresponding parameters, and the golden designs are still required as references.

For circuit feature analysis, current studies mainly perform coverage analysis for the gate-level netlists of circuits under detection to identify suspicious statements or modules. Then, quantitative metrics are utilized to mark the signals or gates suspected of being a Trojan. Circuit feature analysis is a typical heuristic detection method and is effective in practice. However, the limitations are that such methods are only suitable for simple logic circuits. Even when the structural or functional attributes of the circuit under detection fully pass the coverage test, there is no guarantee that Trojans are not present. Manual post-processing is still needed to further analyze suspicious signals or gates to determine whether they were HTs (or part of a Trojan circuit). On the other hand, ML-based approaches can extract and identify Trojan-infected features automatically and screen out the most effective features for classification. This can not only enhance the TPR but also reduce the size of the sample feature vectors, thereby increasing the efficiency of the circuit

| DFS                        | Article             | Main Research Contributions and Innovations                                                                                              |  |  |  |

|----------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Traine                     | [72]                | GA can select the optimal set of ROs from Power RON and one-class SVM then classifies them, thus achieving a high HT detection accuracy. |  |  |  |

| Trojan<br>Detection        | [95]                | LightGBM can extract the key features from scan-chain netlist-based features to reduce feature dimensions.                               |  |  |  |

| Assistance                 | [58]                | One-class ANN can classify continuously transient currents measured by on-chip current sensor.                                           |  |  |  |

| Assistance                 | [96]                | Regression can classify PV-related parameters obtained from transient current waveforms and circuit nets.                                |  |  |  |

|                            | [63]                | Bayesian can calibrate PV distributions by PV monitors to facilitate HT detection by leakage current.                                    |  |  |  |

| Implantation<br>Prevention | [75]                | MOEA can reduce rare signals and maximize the efficiency of logic encryption at IC design time.                                          |  |  |  |

| Trusted                    | [103]               | One-class SVM can establish golden power or delay library by PCM units.                                                                  |  |  |  |

| Library                    | [71], [90],<br>[91] | CAs can cluster side-channel features to build golden side-channel fingerprinting library.                                               |  |  |  |

|                            | [74], [104]         | AIOA and PSO can enhance the performance of learning models such as LR, NBC, and NN by multiple iterations of model related parameters.  |  |  |  |

TABLE 9. Main Research Contributions and Innovations of ML in DFS.

feature analysis methods. However, there are still several potential challenges that remain to be addressed. First, golden designs are needed to establish the training dataset for the structural or functional attributes of the gate-level netlists. Second, these solutions are only valid for identifying explicit Trojans and are not effective at detecting implicit Trojans. Third, the TNR and average accuracy of HT detection need to be further improved. In addition, the execution time and reliability of ML-based approaches depend on the circuit scale, i.e., the number of nets within the circuits, and the quantization metrics selected. They are less effective when analyzing larger circuits.

Side-channel analysis is a non-invasive method. Because this solution can easily generate test vectors and does not need to fully activate the HTs, it is easy to implement and widely used in practice. Especially for large Trojans, it is possible to effectively identify and achieve high detection accuracy. However, this method is susceptible to PVs and noise and performs poorly in the detection of small Trojans. In particular, the main limitation of such a method is to assume that there are golden ICs available as a reference. The requirement for the precision of the equipment is high. For some methods that attempt to sidestep the dependence of golden ICs, the results are less satisfactory in terms of accuracy. ML can effectively preprocess relevant features, such as extracting relevant features and reducing the data dimensionality, to effectively reduce the impact of PVs and noise and improve the accuracy and TPR. However, in this procedure, since Trojans have negligible effects on circuits, they may be removed as unrelated features or noise, thus affecting the HT detection accuracy. Furthermore, the performance of ML-based methods is highly dependent on the selection of relevant features, learning models, and parameters, which may increase the time overhead. In addition, ML methods, such as unsupervised learning, can partially reduce their reliance on golden ICs but still require golden designs to build a training dataset. This, however, remains a limitation in practical applications.

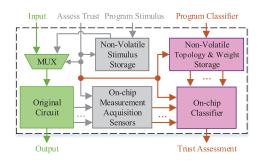

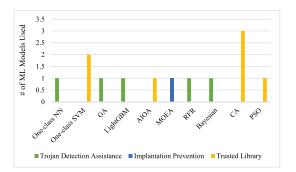

#### 2) DESIGN FOR SECURITY

Another important application of ML in HT defense domains is DFS. Several ML-based countermeasures have been

FIGURE 9. Summary of ML applied in DFS.

proposed for (1) Trojan detection assistance, (2) implantation prevention, and (3) trusted library. Fig. 9 summarizes the existing progress in DFS. In particular, Table 9 briefly summarizes the primary research contributions and innovations of ML applied in DFS based on Fig. 9. From Table 9, it can be concluded that ML, especially optimization algorithms, can be incorporated with design-time mechanisms to increase the accuracy of HT detection, the efficiency of design protection strategies and the performance of learning models. Below, we introduce the primary elements of each ML-based approach, as well as the advantages and disadvantages between ML-based and non-ML-based methods in detail.

#### - Trojan Detection Assistance

HT detection can benefit dedicated on-chip modules. Such embedded solutions can improve the sensitivity of HT detection at design and test time or be used to identify the abnormal behaviors caused by HTs at runtime [92], [93]. In particular, ML can be incorporated with on-chip modules to enhance the accuracy of HT detection at the expense of extra silicon areas in the ICs.

For instance, Karimian et al. proposed exploiting the power ring oscillator network (RON) structure to assist in HT detection [72]. They first utilized the GA to select an optimal set of RO measurements from the power RON and then applied one-class SVM to classify the measurements to identify HT-infected designs. This method can achieve a higher accuracy but requires substantially more training time than the PCA+convex hull and pure SVM-based methods and has a high area overhead [72]. Dong et al. introduced a scanchain feature-based analysis method to identify gate-level Trojans [95]. They first converted the gate-level HTs to scanchain netlists and then utilized a lightweight gradient lifting algorithm called lightGBM to extract the key features for training. LightGBM can reduce the feature dimensions, thereby improving the HT detection accuracy and optimizing the training speed. However, certain HTs with special structures and trigger modules cannot be effectively classified.